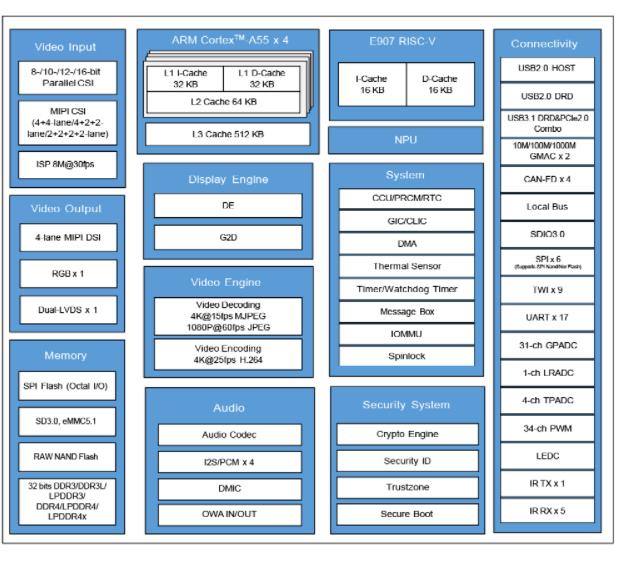

V853芯片包含两个CPU。一个是主核心Arm A7 CPU,运行Tina Linux(全志自研Linux)系统,为芯片主系统;一个是RISC-V E907辅助CPU,运行Melis(全志自研RTOS)系统,主要功能是提供通用算力补充、辅助 Linux 实现快起和低功耗管理等功能。

A7 - Linux系统

V853主核心 A7上运行的是Tina Linux系统。Tina Linux是全志针对AIoT类产品,基于Linux内核深度定制的嵌入式系统。

在 Tina Linux 中,提供 AMP 与 RPMsg 对接 E907

Linux remoteproc 管理控制 E907

RPMsg 与 E907 通讯

E907 - RTOS系统

V853 辅助核心 E907 上运行的是全志自研 RTOS 系统 Melis。其独立于 A7 主核心中的 Linux 系统。可以独立运行。

在 E907 Melis 中,提供 OpenAMP 软件框架来与 A7 Linux 系统进行通信。

提供了处理器的生命周期管理(LCM,Life Cycle Management),与 Linux 的 remoteproc 兼容

提供了处理器间的消息传输机制,与 Linux 的 RPMsg 兼容

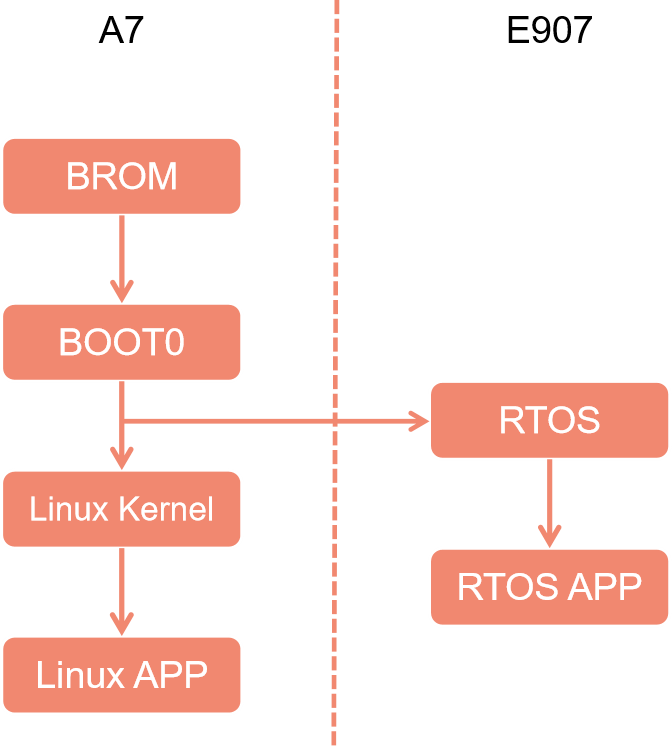

异构系统启动流程

首先,由芯片内部的 BORM 寻找启动介质,在 V853 开发板上便是 eMMC 储存器。找到启动介质后会运行其中的 BOOT0 代码。BOOT0 会在 A7 主核心中运行 Linux 系统,也会在 E907 核心中运行 RTOS 系统。启动的两个系统是独立运行的。

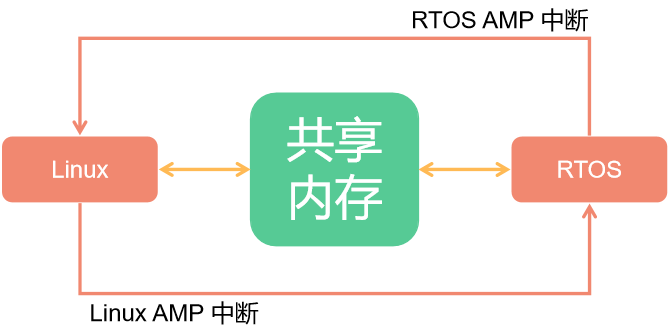

异构系统的通信

V853 的异构系统通讯在硬件上使用的是 MSGBOX,在软件层面上使用的是 AMP 与 RPMsg 通讯协议。其中 A7 上基于 Linux 标准的 RPMsg 驱动框架,E907基于 OpenAMP 异构通信框架。

V853 所带有的 A7 主核心与 E907 辅助核心是完全不同的两个核心,为了最大限度的发挥他们的性能,协同完成某一任务,所以在不同的核心上面运行的系统也各不相同。这些不同架构的核心以及他们上面所运行的软件组合在一起,就成了 AMP 系统 (Asymmetric Multiprocessing System, 异构多处理系统)。

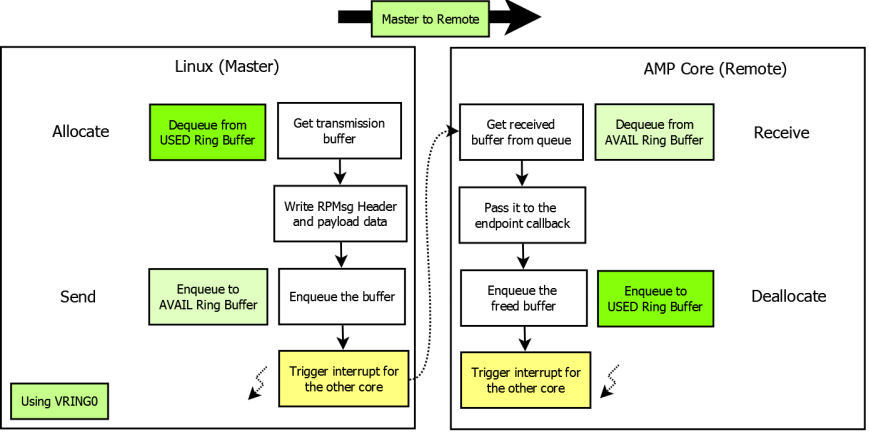

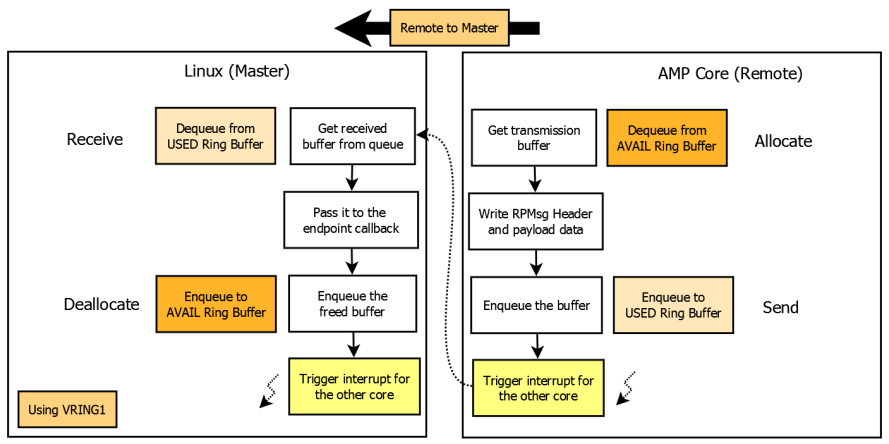

由于两个核心存在的目的是协同处理,因此在异构多处理系统中往往会形成 Master - Remote 结构。主核心启动后再启动辅助核心。当两个核心上的系统都启动完成后,他们之间就通过 IPC(Inter Processor Communication)方式进行通信,而 RPMsg 就是 IPC 中的一种。

在AMP系统中,两个核心通过共享内存的方式进行通信。两个核心通过 AMP 中断来传递讯息。内存的管理由主核负责。

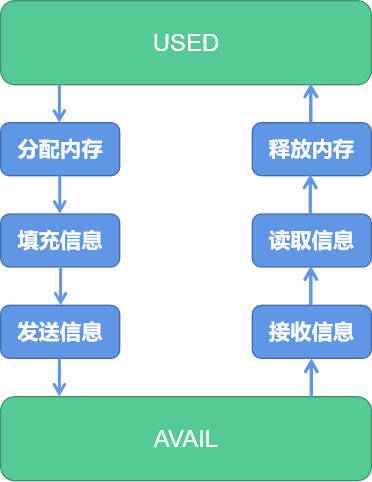

AMP 系统在每个通信方向上都有两个缓冲区,分别是 USED 和 AVAIL,这个缓冲区可以按照 RPMsg 中消息的格式分成一块一块链接形成一个环。

当主核需要和从核进行通信的时候可以分为四步:

主核先从USED中取得一块内存(Allocate)

将消息按照消息协议填充

将该内存链接到 AVAIL 缓冲区中(Send)

触发中断,通知辅助核有消息处理

反之,从核需要和主核通信的时候也类似:

主核先从AVAIL中取得一块内存(Allocate)

将消息按照消息协议填充

将该内存链接到 USED 缓冲区中(Send)

触发中断,通知主核有消息处理。

既然 RPMsg 是一种信息交换的协议,与TCP/IP类似,RPMsg 协议也有分层,主要分为三层,分别是传输层、MAC层和物理层。

其中 MAC层 的 VirtIO 是一种I/O 半虚拟化解决方案,是一套通用 I/O 设备虚拟化的程序,是对半虚拟化 Hypervisor 中的一组通用 I/O 设备的抽象。提供了一套上层应用与各 Hypervisor 虚拟化设备之间的通信框架和编程接口,减少跨平台所带来的兼容性问题,大大提高驱动程序开发效率。

RPMsg 总线上的消息都具有以下结构,包含消息头和数据两个固定的部分,该消息格式的定义位于drivers/rpmsg/virtio_rpmsg_bus.c中,具体定义如下:

struct rpmsg_hdr { u32 src; u32 dst; u32 reserved; u16 len; u16 flags; u8 data[];} __packed;

异构系统的控制

在异构系统中,不止需要消息的传输,还需要相关控制。例如主核对辅助核心的开启,加载固件,关闭等等。这就需要用到 remoteproc 框架。

remoteproc 框架支持对不同平台,不同架构的处理器进行控制,可以监控辅助核心的运行情况。

对于 V853 来说,remoteproc 用于对 E907 进行生命周期管理,一般来说包含有加载固件、 检测远端处理器是否崩溃等功能。它在加载远端处理器的固件时,会根据固件中定义的 resource table 来申请资源,并创建 VirtIO 设备。

审核编辑 :李倩

-

处理器

+关注

关注

68文章

19595浏览量

232197 -

Linux系统

+关注

关注

4文章

600浏览量

27937 -

通讯

+关注

关注

9文章

924浏览量

35345

原文标题:详解全志V853上的ARM A7和RISC-V E907之间的通信方式

文章出处:【微信号:gh_79acfa3aa3e3,微信公众号:全志在线】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Arm与RISC-V架构的优劣势比较

RISC-V 与 ARM 架构的区别 RISC-V与机器学习的关系

全志T536系列处理器特性概述 集成RISC-V E907协处理器

ARM A7和RISC-V E907之间的通信方式

ARM A7和RISC-V E907之间的通信方式

评论