前段时间,Soitec宣布8英寸SiC量产,而且还投资23亿建线(。点这里。),更为关键的是他们号称能让单块SiC晶锭产量增加10倍,使SiC MOSFET芯片尺寸缩小5-15%。

很多人都很好奇Soitec的技术细节,最近,“行家说三代半”拿到了他们的技术文献,今天就给大家分享一下。

插播:7月7日,欣锐科技、英飞凌、Wolfspeed、三菱电机、芯干线、百识电子和恒普科技等企业“大咖”,将参与“新能源趋势下第三代半导体产业化发展论坛”,发布最新技术报告,报名点文末“阅读原文”。

SiC功率器件已成为广泛应用的突破性技术,风靡汽车牵引逆变器、DC/DC转换器、车载充电器或充电站等领域。

但是目前,4H-SiC材料质量和供应限制了碳化硅在汽车等领域的爆发,因为这些领域对碳化硅衬底的质量要求非常高,而目前业界还很难提供近乎无缺陷的衬底晶圆。

Soite认为,他们通过Smart Cut技术,制造的SmartSiC衬底,具有非常高的质量,能够优化器件良率。

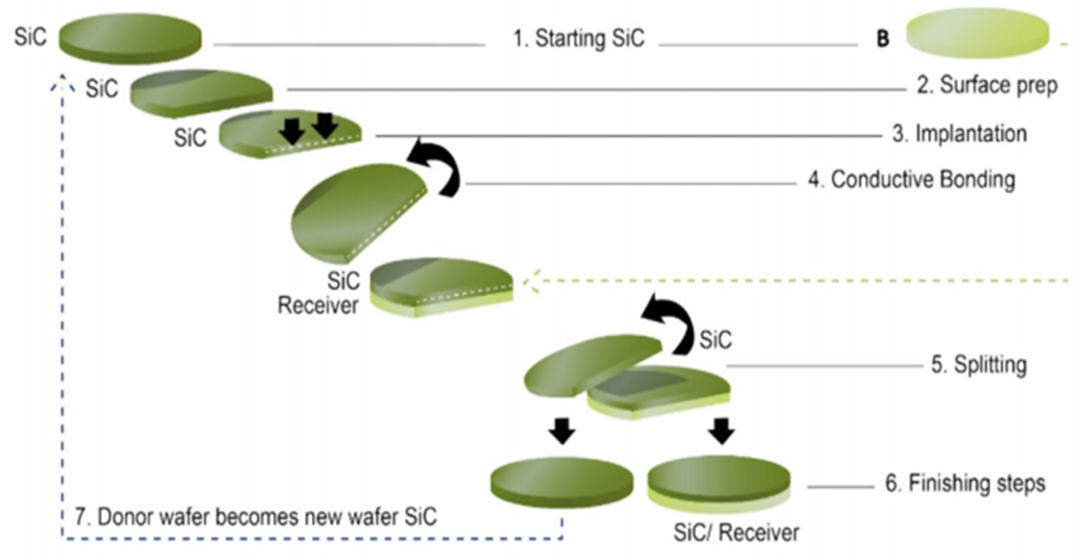

SmartSiC的制作步骤如下,这种方式的好处可以参考之前的报道:

图1:SmartSiC 衬底制造工艺

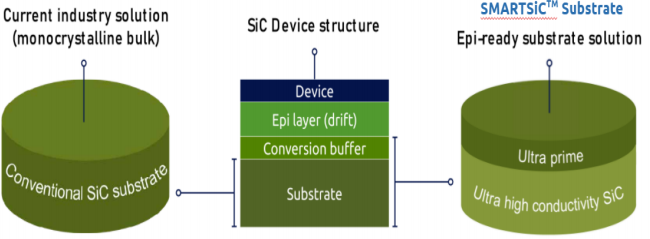

SmartSiC衬底概念图如下:

图2: SmartSiC衬底

目前,Soitec已经展示了SmartSiC开发样品,并可用于器件评估。

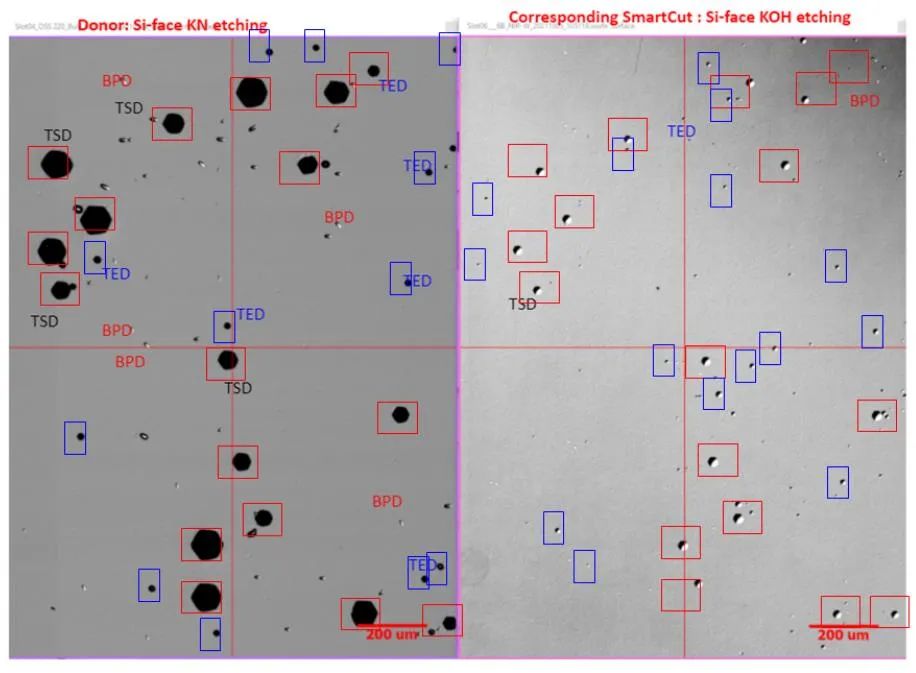

4H-SiC 衬底(左)和 SmartSiC衬底(右)

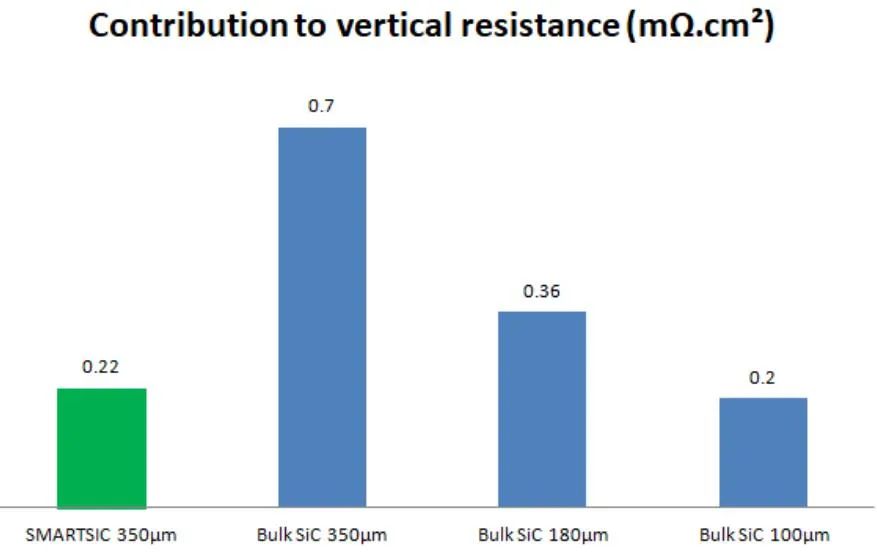

根据文献,Soitec通过多晶SiC衬底的开发,制作了电阻率低至 5mΩ.cm或更小的碳化硅晶片。从整个堆栈来看,对应的垂直电阻为0.22mΩ.cm2(或更小)。

350μm的SmartSiC电阻率与100µm的 4H SiC相当,比常规180µm的碳化硅衬底的电阻率降低了35%。

此外,多晶SiC衬底的另一个好处是能够提高材料的机械性能,从而使磨削下的变形可以忽略不计。与Bulk SiC 参考相比,优化的多晶SiC磨削至180µm变形得到改善。

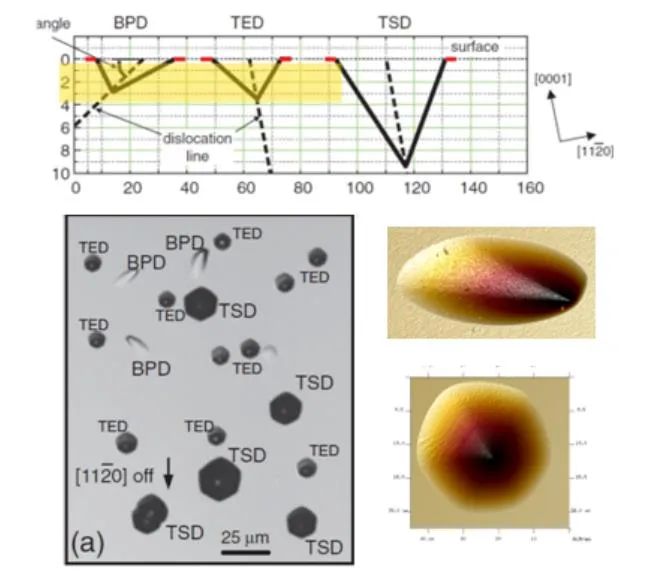

同时,Soitec还证明了SmartSiC衬底比供体晶圆更低的晶体缺陷率。

显微镜和 AFM 图像显示,SmartSiC的 TED、TSD 和 BPB都得到了明显的优化。

通过对比可以发现,Smart Cut 不会引入新的晶体缺陷。

为此,该公司认为,他们的SmartSiC在功率器件应用方面具有巨大潜力,不仅可以提高性能,而且可以提高可制造性。

原文标题:电阻率降低35%!Soitec公布碳化硅技术细节

文章出处:【微信公众号:第三代半导体风向】欢迎添加关注!文章转载请注明出处。

-

功率器件

+关注

关注

42文章

1832浏览量

91051 -

SiC

+关注

关注

30文章

2981浏览量

63417 -

MOSFET芯片

+关注

关注

1文章

7浏览量

9161

原文标题:电阻率降低35%!Soitec公布碳化硅技术细节

文章出处:【微信号:SiC_GaN,微信公众号:行家说三代半】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

N1X 英伟达Arm AI PC 芯片技术细节,性能表现

SONY编码板测试:技术细节与性能评估

台积电2纳米制程技术细节公布

有关UV固化你不知道的技术细节

机房精密空调外机的技术细节!

频谱仪怎么测量相位噪声

PCB电路板设计与制作的步骤和要点

探究双路或四路可选可编程晶体振荡器SG-8503CA/SG-8504CA的技术细节及其应用

图像边缘检测系统的设计流程

直通网线的作用及制作步骤

LED显示屏的换帧频率与刷新频率:技术细节与市场发展

示波器怎么测量直流电压

深入了解目标检测深度学习算法的技术细节

聊聊50G PON的技术细节

SmartSiC的制作步骤及技术细节

SmartSiC的制作步骤及技术细节

评论