神经网络是一种流行的机器学习模型,但它们需要更高的能耗和更复杂的硬件设计。随机计算是平衡硬件效率和计算性能之间权衡的一种有效方式。然而,由于算术单元的低数据精度和不准确性,随机计算见证了 ML 工作负载的低准确性。

为了解决与传统随机计算方法相关的问题,并通过更高的精度和更低的功耗来提高性能,正在进行的研究提出了一种改进的基于块的随机计算架构。通过在输入层中引入块,可以通过利用高数据并行性来减少延迟。更重要的是确定全局优化方法所需要的块数。

现有的方法包括增加比特流的长度以提高数据精度,甚至使用指数比特来获得准确的结果。然而,这引入了较长的计算延迟,这对于 TinyML 应用程序来说是不合理的。因此,为了应对这种不断上升的计算延迟,比特流被分成块然后并行执行。结合块内算术单元和输出修正 (OUR) 方案可缓解块间不准确问题,从而提供高计算效率。

基于块的随机计算架构

研究提供了一种新颖的架构,其中输入被划分为块并使用优化的块内算术单元并行执行乘法和加法。此外,在 TinyML 应用程序的延迟-功耗权衡方面,所提出的模型是一个出色的架构。

架构划分如下:

块划分

如上图所示,输入比特流被划分为“k”个值块。所提出的想法是,为比特流选择大量块并不能保证是最佳的,但可以用于接近近似值。如果在选择块数时出现错误,这可能会自相矛盾地导致大错误。在确定来自输入比特流的正和负部分的两个平均值的概率方面存在复杂的计算。

块内计算

缓解了传统加法器面临的OR加法器相关问题和分离加法器溢出问题。新修改的架构设计在输入之间带有 XNOR+AND 门,以消除双极计算的相关性。

每个输入位都在并行计数器 (PC) 中获取,对于正负部分 (Ap, An) 分别进行处理。有两个专用累加器用于处理有符号位。取输入位后,累加器之间发生减法,如正负部分所示。目标是获得所有输入的累积 1 的数量。进一步地,比较取时间输出(Sop,Son)中的一位,在多个“n”个循环之后,计算符号位,并根据符号位Ap和An,选择Sop和Son的输出结果。

这种新的基于累加器的符号幅度格式加法器利用 unNSADD 加法器来比较输出和输入中的实际累加 1 以确定输出位。这种方法消除了相关性和快速溢出问题的影响。

块间输出修正方案

尽管块内加法器解决了相关性和溢出问题,但块划分引入了新的块间不准确错误。乘法器不会发生这种情况,因为输入是 XNORed 和 ANDed。但是对于加法器,输出中 1 的数量可能会偏离所产生的不准确性。输出修订方案在并行块内计算阶段之后添加或删除 1s,而不会引入任何额外的延迟来解决这些块间不准确错误。

新颖的基于块的随机计算架构旨在提高随机计算运算电路的精度,同时降低计算延迟和能源效率。根据研究结果,该方法比现有方法的准确度提高了 10% 以上,并节省了 6 倍以上的功率。

审核编辑:郭婷

-

神经网络

+关注

关注

42文章

4842浏览量

108173 -

机器学习

+关注

关注

67文章

8564浏览量

137221

发布评论请先 登录

下一代汽车中现代计算架构的性能组件和保护

如何在LTspice仿真中实现伪随机数和真随机数的生成

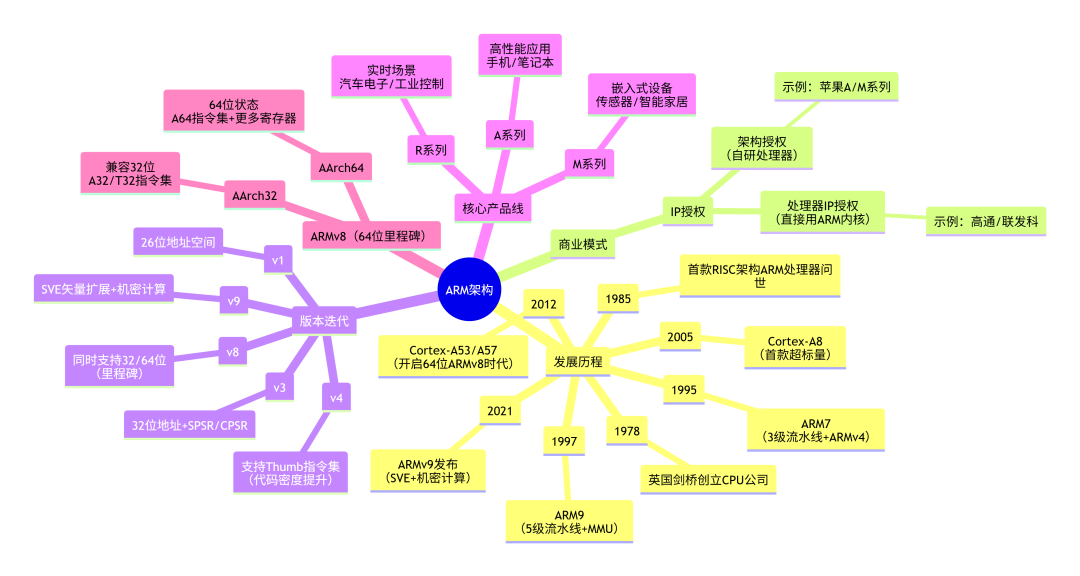

深度解析 ARM 架构:从剑桥车库到未来计算

双口SRAM静态随机存储器存储原理

龙架构计算机系统能力核心课程教学研讨会圆满举行

用于RISCV的F指令集实现的浮点计算单元(FPU)设计方案

奕斯伟计算CTO何宁:新场景助力新架构实现突破!

【PZ-ZU15EG-KFB】——ZYNQ UltraScale + 异构架构下的智能边缘计算标杆

知合计算:RISC-V架构创新,阿基米德系列剑指高性能计算

异构计算解决方案(兼容不同硬件架构)

如何释放异构计算的潜能?Imagination与Baya Systems的系统架构实践启示

用于有效使用TinyML的随机计算架构

用于有效使用TinyML的随机计算架构

评论