本文为明德扬原创文章,转载请注明出处!

由于AD9144是高速DA转换模块,转换速率可以达到2.5G,可以满足普通的DA数据接口。为了匹配高速AD/DA转换,JESD204B接口就应运而生,在本高速DA转换工程中,AD9144的参数设定与JESD204B有千丝万屡的关系,二者是相互对应的。

本次工程实现的目标:

波形:正弦波(波形由16个16位宽数据构成)

频率:31.25MHZ

采样率:500MHZ

DAC个数:2个

LANE个数:4个

插值:1

类型:单link

单次传输数据为:128位

一、 AD9144工作模式的选择

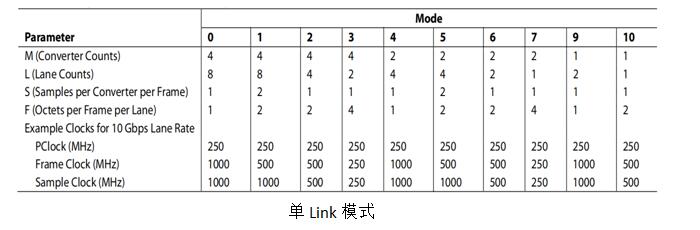

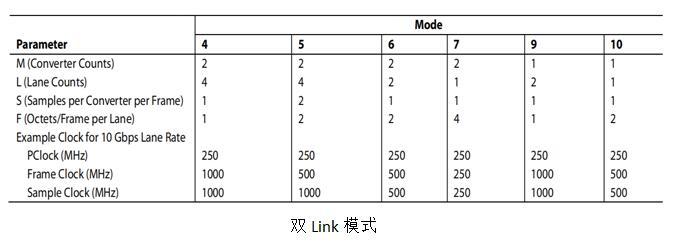

AD9144共有Single-Link和dual-Link两种类型可以选择,其中Single-Link类型有10种工作模式,Dual-Link有6种工作模式。

具体工作模式如下图所示:

1. 参数介绍:

M:转换DA个数;

L:lane的个数;

S:每一个AD的每一帧的采样点数;

F:每条lane的每一帧的字节数;

2. 模式的选择步骤

对于工作模式的选择不同的项目有着不同的思考:

1) 本次采用单link方式所以有10种工作模式选择;

2) AD9144使用两个DAC所以只能在mode4-mode7之间选择;

3) AD9144和JESD204B间采用4条lane相连,所以只能选择mode4或mode5;

4) 为了便于AD9144参数计算,本次采用JESD204B的mode4。

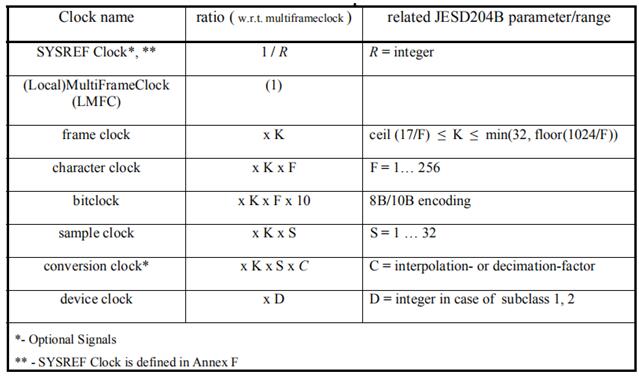

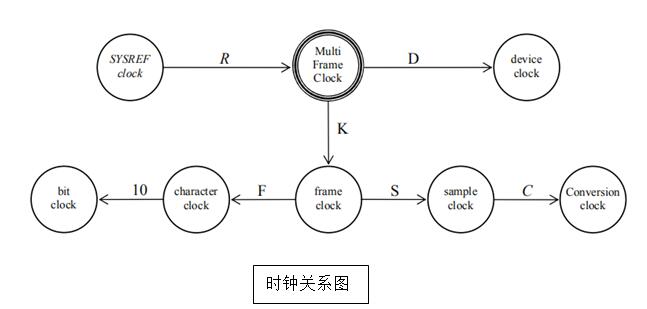

二、JESD204B的时钟关系

了解AD9144时钟关系是我们计算AD9144参数的前提,下面介绍一下JESD204B中各个时钟之间的关系。

1.名词解释:

SYSREF clock:同步时钟频率

Device clock:驱动时钟频率

Multifram clock:多帧频率

Fram clock:帧频率

Bit clock:单条lane数据传输速率

Sample clock:采样率

Conversation clock:转换率

2.关系介绍

1个同步时钟周期内,可以发R个多帧

1个多帧的发送需要D个工作时钟;

1个多帧由K个帧组成

1个帧内由F个字节数

1个字节经过8B/10B编码得到bit数

1帧内由S个采样点

1个采样点经过C倍插值得到转化后的采样结果(C由x1,x2,x4,x8四种模式)

三、 AD9144的参数设定

1.参数设定的意义

①确定配置AD9144所需要的寄存器值;

②设定JESD204B的IP核的参数;

③ 确定AD9516的分频时钟频率;

2.AD9144的时钟参数计算

由工程的设计目标,可以结合JESD204B对AD9144进行参数设置。

| = 1 * GB3 * MERGEFORMAT ① |

有效数据传输速率 =sample*16*2=16G/s;

实际传输数据速率 =16G*(10/8)=20G/s;

Lane_rate =20G/4=5G;

Sapmple_clock =500MHZ;

Frame_clock =sample_clock/S=500MHZ(S取1);

Char_clock =fram_clock*F=500MHZ(F取1);

Bit_clock =char_clock*10=5G(8b/10B编码得出);

Conversion_clock =sample_clock*C=500MHZ(单倍插值C=1);

Mul_fram_clock =fram_clock/K=15.625MHZ(K取32);

| = 2 * GB3 * MERGEFORMAT ② |

Sysref_clock =mul_fram_clock/R=7.8125MHZ(R取合适的整数即可R=2);

device_clock =mul_frame_clock*D=125MHZ(D 取合适整数即可D=8);

Refclk=lane/40 =125MHZ(AD9144参考时钟);

注释:

= 1 * GB3 * MERGEFORMAT ①实际速率是有效速率经过8B/10B编码得出;

= 2 * GB3 * MERGEFORMAT ②D最小值是,Dmin=有效数据量/128,D为整数;

四、 AD9144的配置表生成

1.实现方法

方法1;对照AD9144手顺根据工程的实现功能以及AD9144的计算参数进行逐个配置

方法2:使用AD9144的配置软件进行配置,然后对照手顺进行配置

本次使用方法2进行AD9144的寄存器值的配置

2.实现步骤

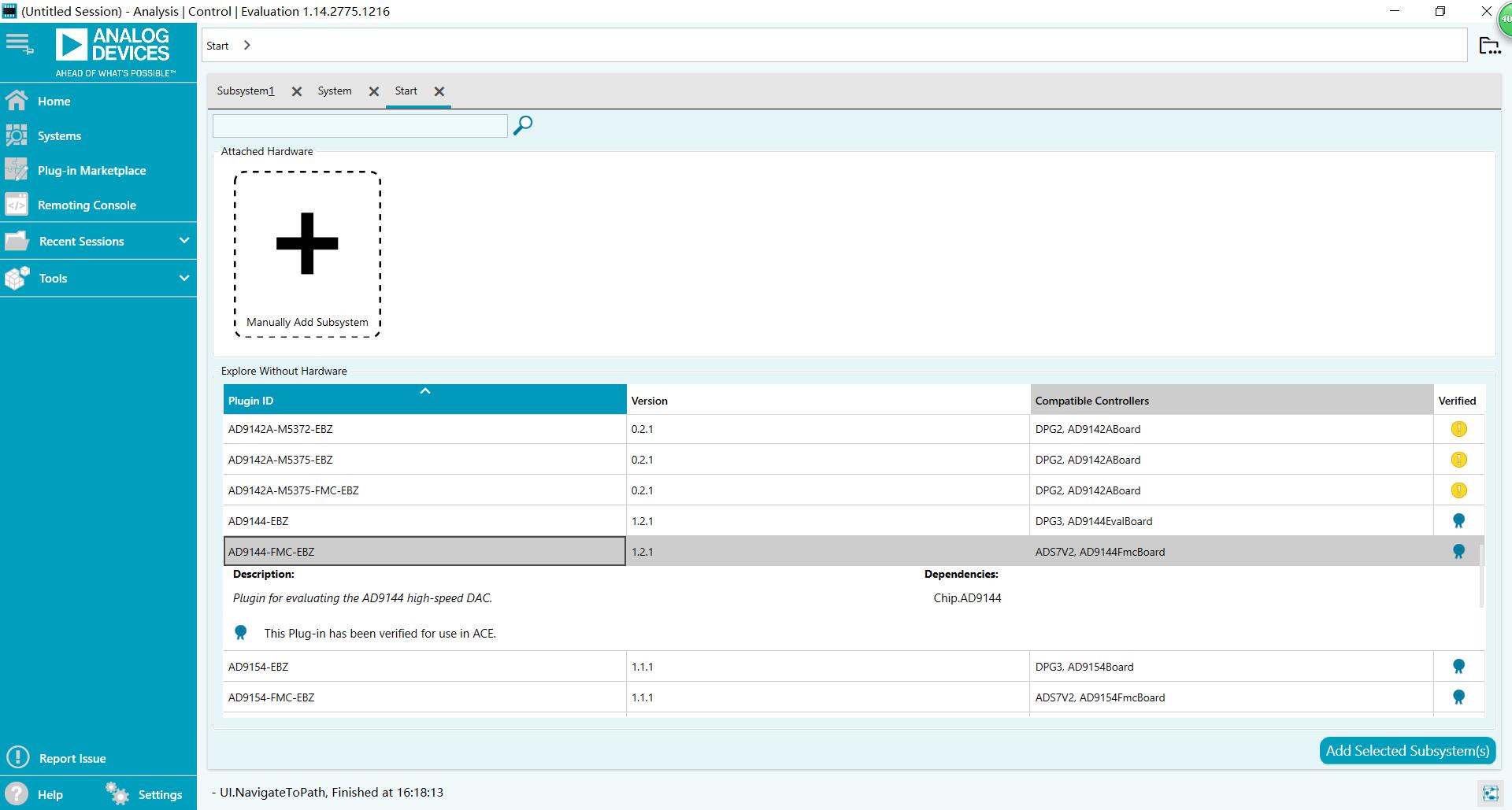

1. 打开ACE软件选择对应芯片AD9144-FMC-EBZ,并选择添加。

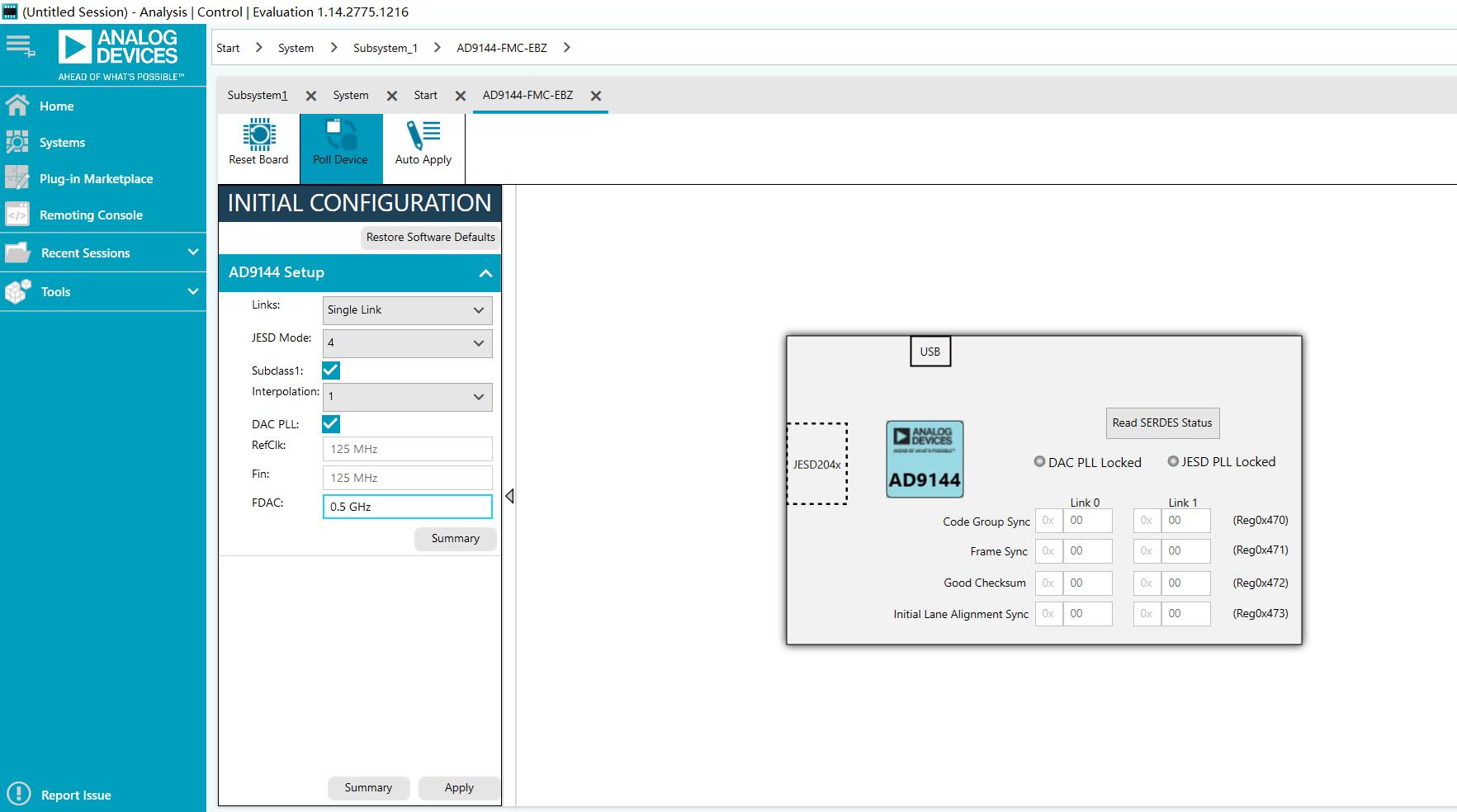

2. 对照计算的AD9144的参数进行芯片设置,完成后双击蓝色AD9144图标。

(1)Link模式:single; (2)link;JESD MODE :mode4;

(3)Subclss:子类1; (4)Interpolation:选择1倍插值(无插值模式);

(5)DAC PLL勾选; (6)RefClk:计算的AD9144参考时钟,125MHZ;

(7)FIN=device_clock=125MHZ; (8)FADC=采样率=500MHZ;

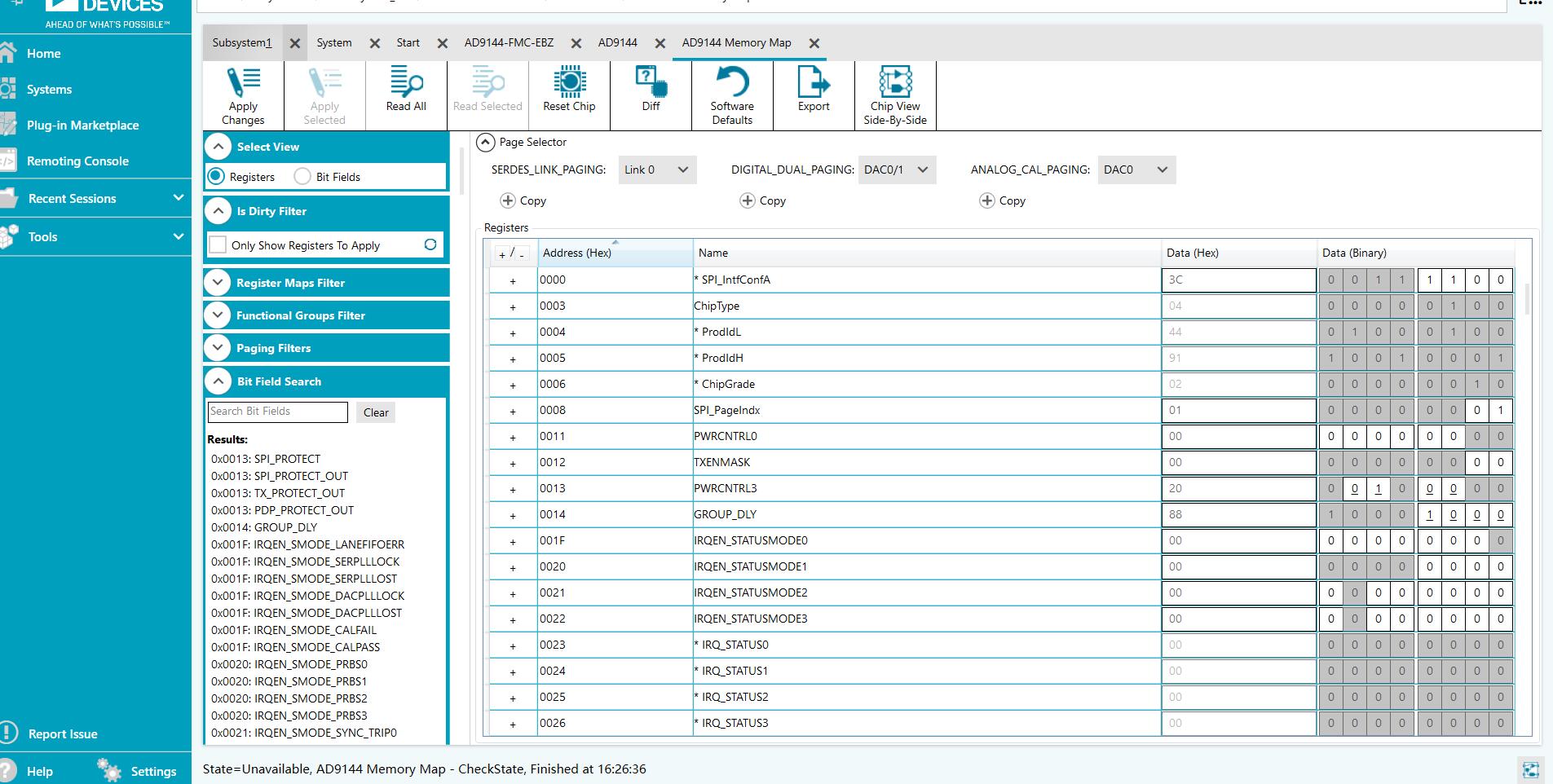

3. 寄存器配置表生成后,即可用来配置AD9144寄存器

以上就是AD9144的参数设定,感兴趣的同学可以留言相互讨论!

审核编辑 黄昊宇

-

FPGA

+关注

关注

1664文章

22516浏览量

639684 -

JESD204B

+关注

关注

6文章

86浏览量

19963 -

ad9144

+关注

关注

0文章

9浏览量

2105 -

jesd204b时钟

+关注

关注

0文章

2浏览量

977

发布评论请先 登录

AD9144:四通道16位高速数模转换器的技术剖析与应用指南

AD9083:16通道、125 MHz带宽JESD204B模数转换器的全方位解析

AD9094:8位、1 GSPS、JESD204B四通道ADC的深度解析

技术文章|高速DAC JESD204接口接收机物理层压力测试(下)

技术文章|高速DAC JESD204接口接收机物理层压力测试(上)

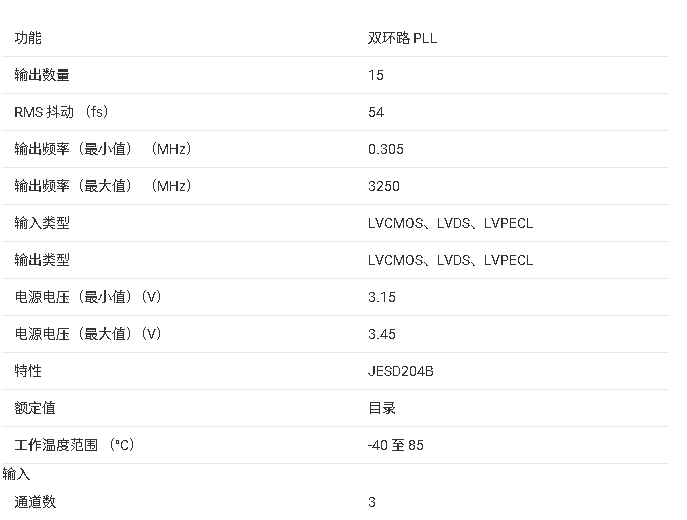

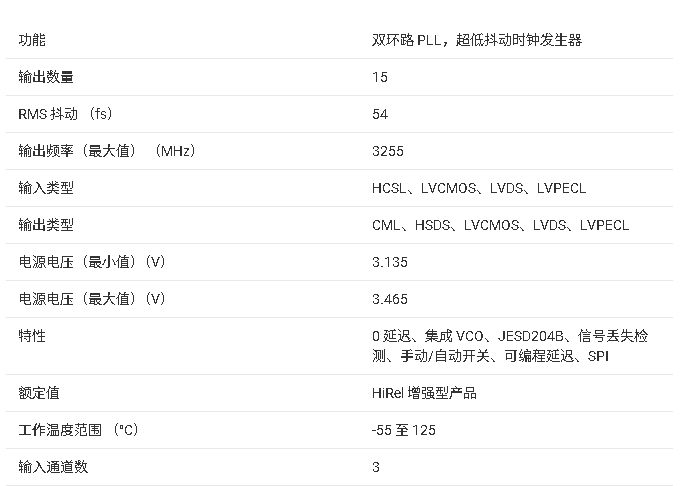

LMK04828 超低噪声JESD204B兼容时钟抖动清除器技术手册

LMK0482x系列超低噪声JESD204B兼容时钟抖动清除器技术文档总结

LMK04616 超低噪声低功耗JESD204B兼容时钟抖动清除器总结

LMK04828-EP 超低噪声JESD204B兼容时钟抖动清除器总结

LMK04832 超低噪声、3.2 GHz、15 输出、JESD204B 时钟抖动清除器技术手册

LMK04368-EP 超低噪声JESD204B/C双环路时钟抖动清除器总结

使用JESD204B接口的AD9144高速DA转换模块参数设定(私人总结版)

使用JESD204B接口的AD9144高速DA转换模块参数设定(私人总结版)

评论