在英特尔创始人戈登摩尔提出的摩尔定律中,每隔18个月集成电路上可容纳的集体管数目就会增加一倍,同时处理器的计算能力也会指数式增长。尽管我们都说摩尔定律已死,但这更多是针对最后一句话,也就是性能的增长趋势,因为现在的性能增长瓶颈已经不再局限于CPU处理器,还有存储、软件等多方面因素。

即便如此,晶体管数量的增加趋势其实仍有一定的参考价值,虽然各大厂商也不能完全遵循这一趋势,但基本也不会偏离太远。国外分析师David Schor为此做了一个摩尔定律追踪图,直白地显示各大厂商的芯片产品与摩尔定律存在多少偏差。

老牌厂商的跌宕起伏

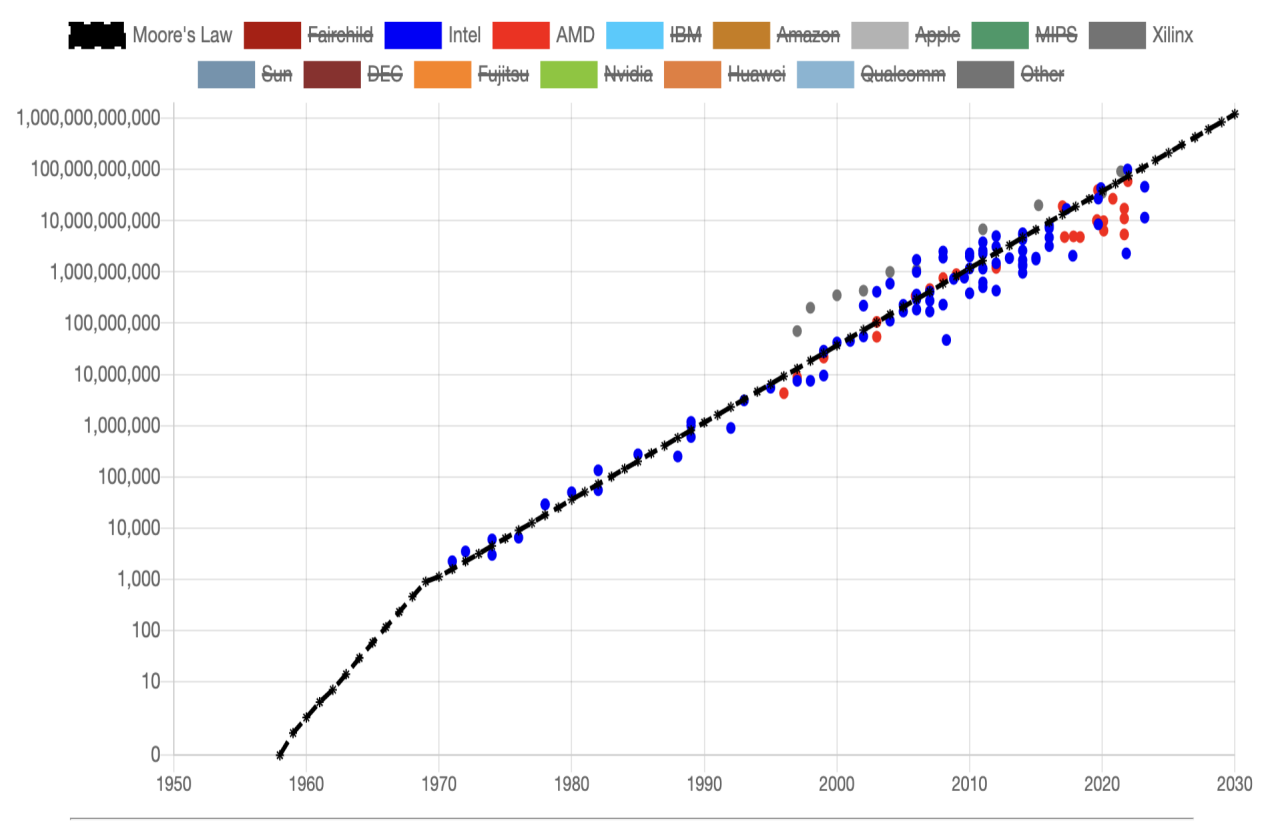

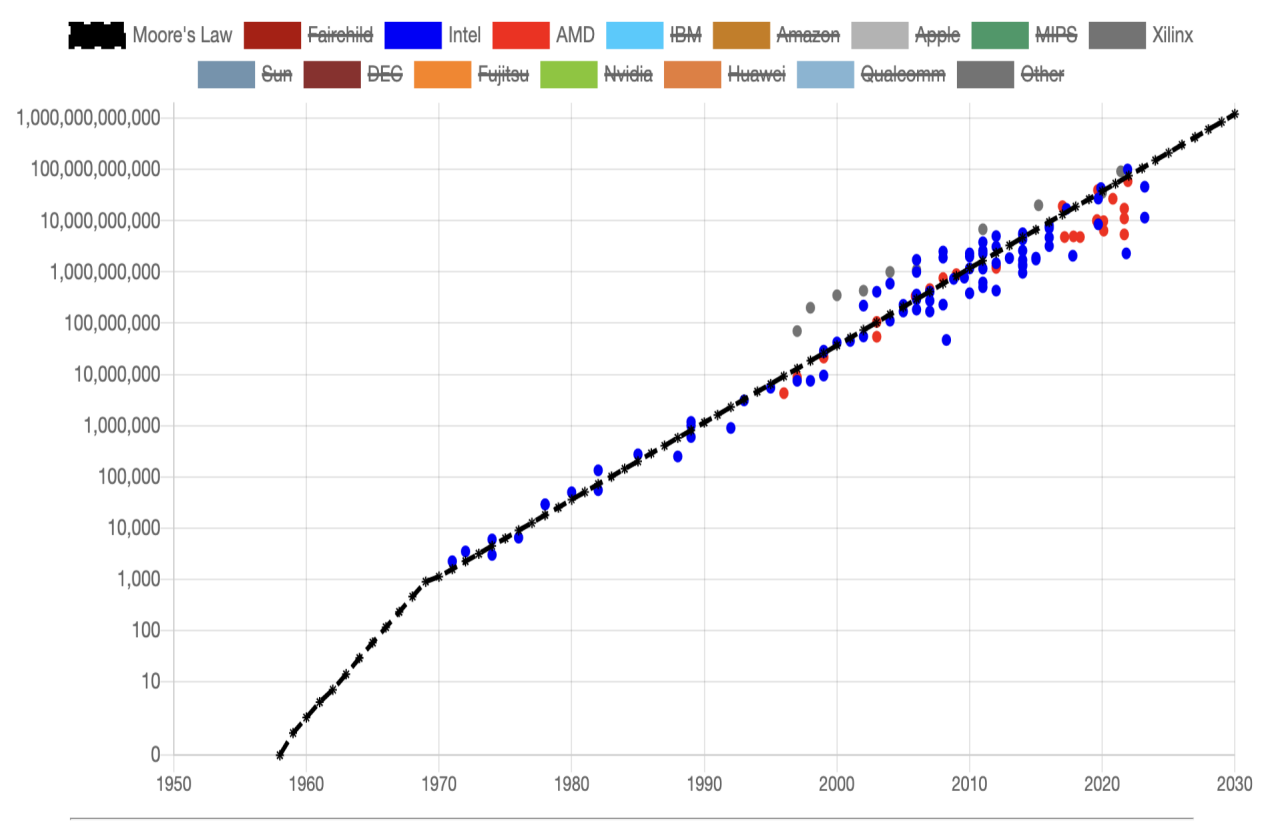

最初摩尔定律的提出,就是对CPU性能的提升做一个参照,所以我们先来看看英特尔和AMD两家x86巨头是否好好遵循摩尔定律。

英特尔、Xilinx/AMD产品晶体管数量趋势 / David Schor

从上图中可以看出,近年来两家的CPU、GPU产品基本都位于摩尔定律的晶体管数目之下,只有少数数据中心级别的GPU能够达标,比如英特尔的Xe HPC架构GPUPonto Vecchio、AMD的CDNA2 .0架构GPU Aldebaran,这些GPU产品要么用了MCM结构要么用了Chiplet设计,所以在晶体管数量上占据一定优势很正常。

至于图中那些高于摩尔定律的点,绝大多数并不是CPU、GPU芯片,而是Altera/英特尔和Xilinx/AMD的FPGA。对于追求最大化逻辑单元数的FPGA来说,超过摩尔定律可以说是必经之路,哪怕是这几年工艺发展变慢的情况下,英特尔的Stratix 10系列和Xilinx的Versal系列FPGA,也凭借着率先使用异构与Chiplet保持着较高的晶体管数目。

ARM的崛起

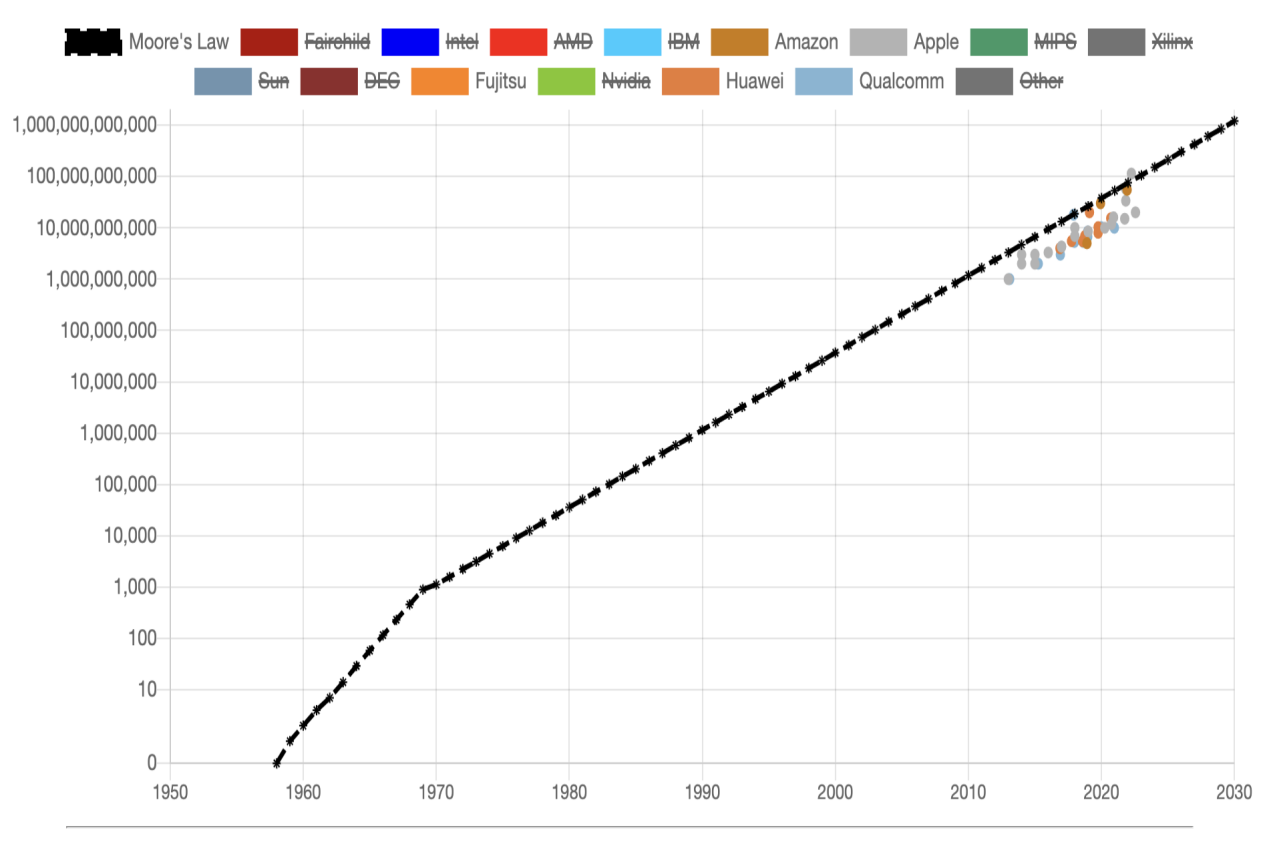

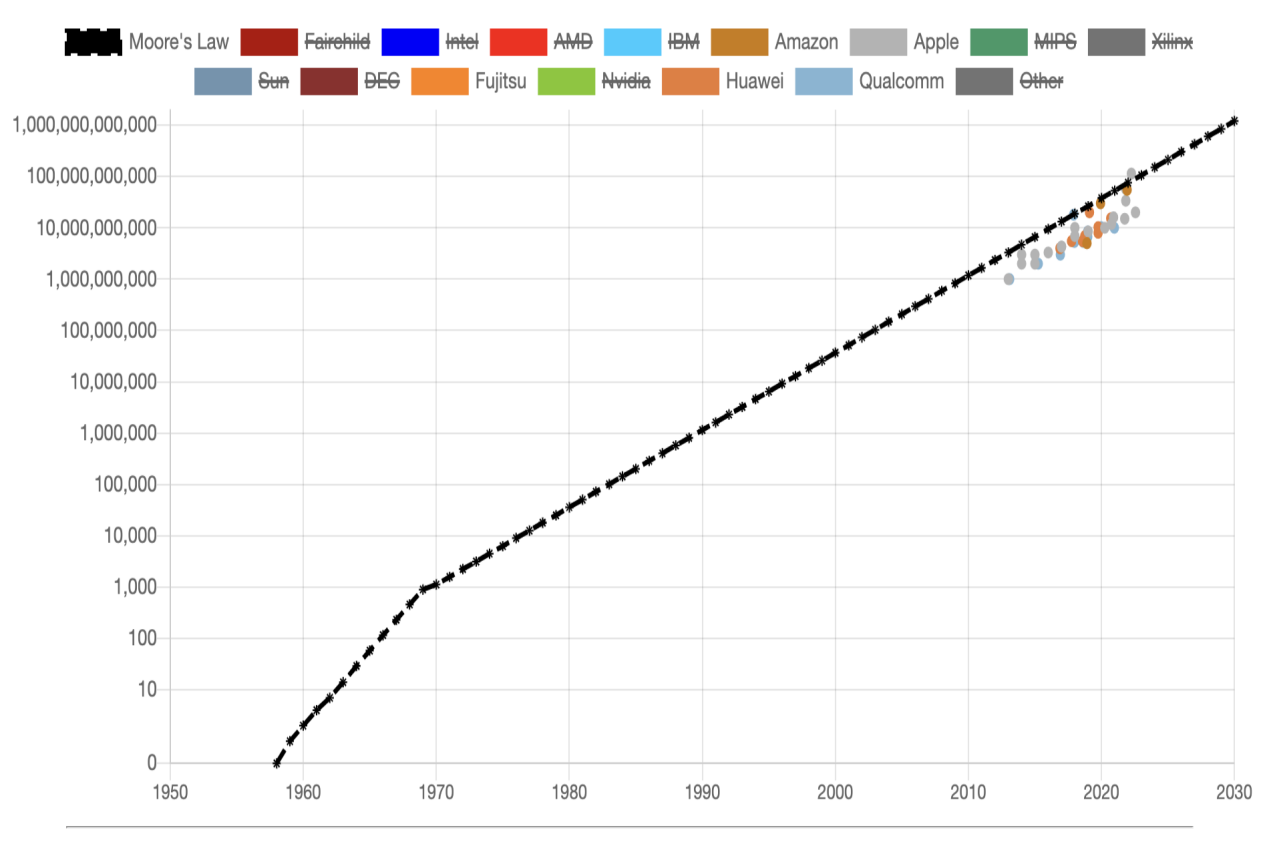

2010年之后,智能手机开始普及,也象征着ARM的崛起。以高通和苹果为首的一众手机/手机芯片厂商,开始追求如何在手机芯片极小的面积上,做到尽可能多的晶体管数量。这些手机处理器之间的竞争也在推动台积电等代工厂之间开始对先进工艺的疯狂追求,当然了手机SoC在这上面追求的表面上是高性能,其实还是高能效,至于朝摩尔定律曲线看齐,完全不是他们的目标。

ARM芯片晶体管数量趋势 / David Schor

从上图可以看出,无论是苹果、华为,还是高通,他们设计的ARM手机SoC都没有超过这条摩尔定律曲线。毕竟手机作为消费产品,处理器并不能占据全部的卖点,在面积、功耗、成本等各方面考量之下,手机SoC设计厂商都没有选择狂堆晶体管的方案。哪怕是苹果的A系列处理器,也只有对面积要求不高的A8X、A12X这样的平板SoC略微靠近了摩尔定律曲线。

但手机SoC从来都不是ARM追求晶体管数量的终点,这个任务将由数据中心的Arm处理器来完成。在上图的曲线中,有一些代表ARM处理器的点已经基本与摩尔定律曲线重合了,甚至还有超过的。

我们先来看下这几个与曲线重合的点,它们分别是高通的Centriq,亚马逊的Graviton 2/3、华为的鲲鹏920和阿里巴巴的倚天710,这些无一例外都是用于数据中心的ARM处理器。在数据中心这种场景下,无论是哪家厂商追求的都是最高的性能,所以如此多的晶体管数量也见怪不怪了。至于那个唯一超过的点则是苹果的M1 Ultra,其面积也达到了860mm2,M1的八倍之多。苹果在这颗庞大的芯片上塞入了1140亿个晶体管,完全超出了同期的竞争对手。

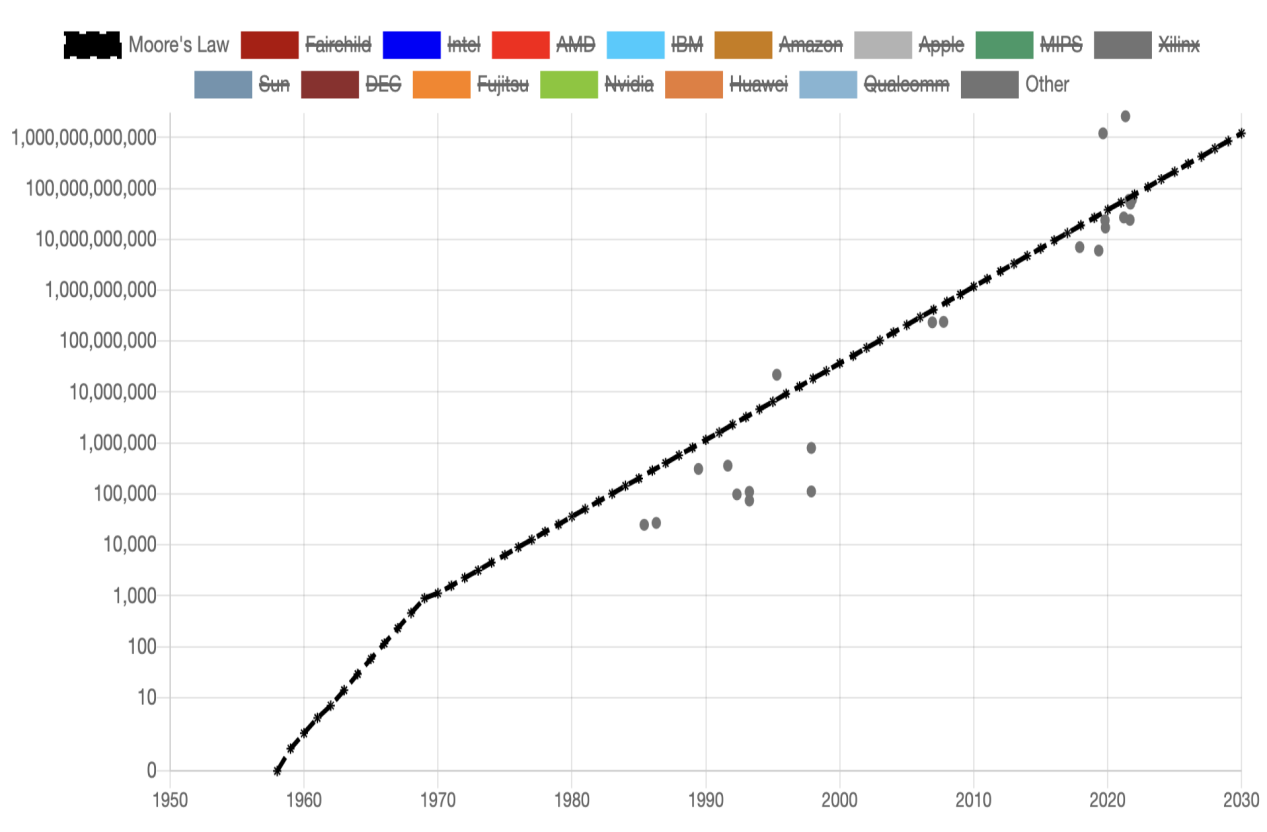

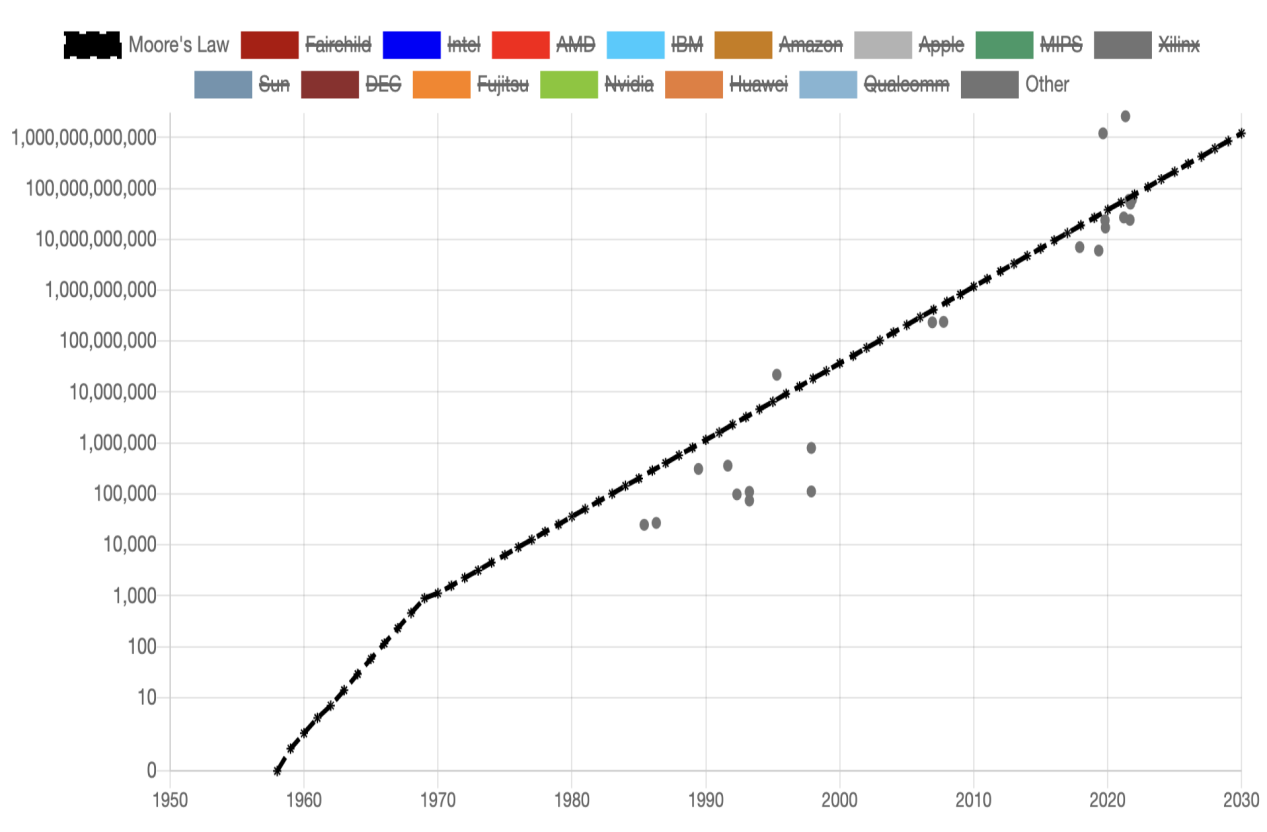

其他值得一提的厂商

其他芯片的晶体管数量趋势 / David Schor

对于一些刚成立不久的公司来说,他们的目标不是为了追求更高的晶体管密度。但对于一些AI/ML芯片初创公司,或者像上面提到的ARM芯片一样牵扯到数据中心,这些芯片的晶体管数目也少不了。在上图中,近年来接近摩尔定律曲线的也有不少,比如阿里巴巴的自研架构AI推理芯片含光800、Graphcore的WoW 3D封装IPU芯片Colossus MK2、Esperanto的千核RISC-V AI芯片ET-SoC-1,还有特斯拉为其Dojo超算打造的AI芯片D1。

你可能在看图时已经注意到了远在摩尔定律曲线之上的那两个点,是谁拥有如此可怕的设计实力,晶体管数目甚至超过了2030年的摩尔定律曲线呢?答案自然就是最大芯片尺寸的纪录保持者,坚持Wafer-Scale的Cerebras。Cerebras在去年发布的Wafer Scale Engine 2面积达到了46225mm2,近乎M1 Ultra芯片的54倍,接近一个12英寸晶圆的大小。别看Cerebras的第二点与第一个点的Wafer Scale Engine一代没差多少,这只是因为这个图的规模放不下了,因为Wafer Scale Engine 2的晶体管数量已经达到了可怕的26000亿。

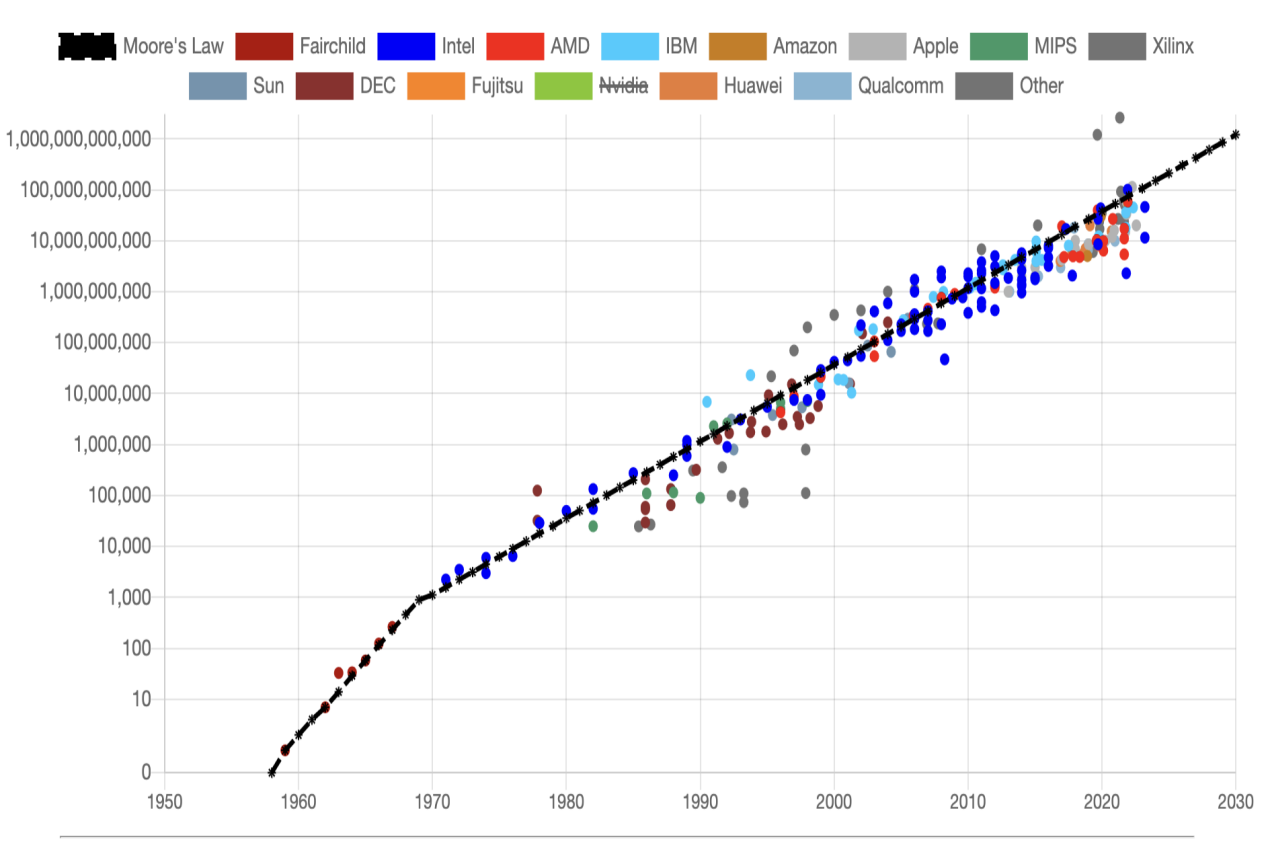

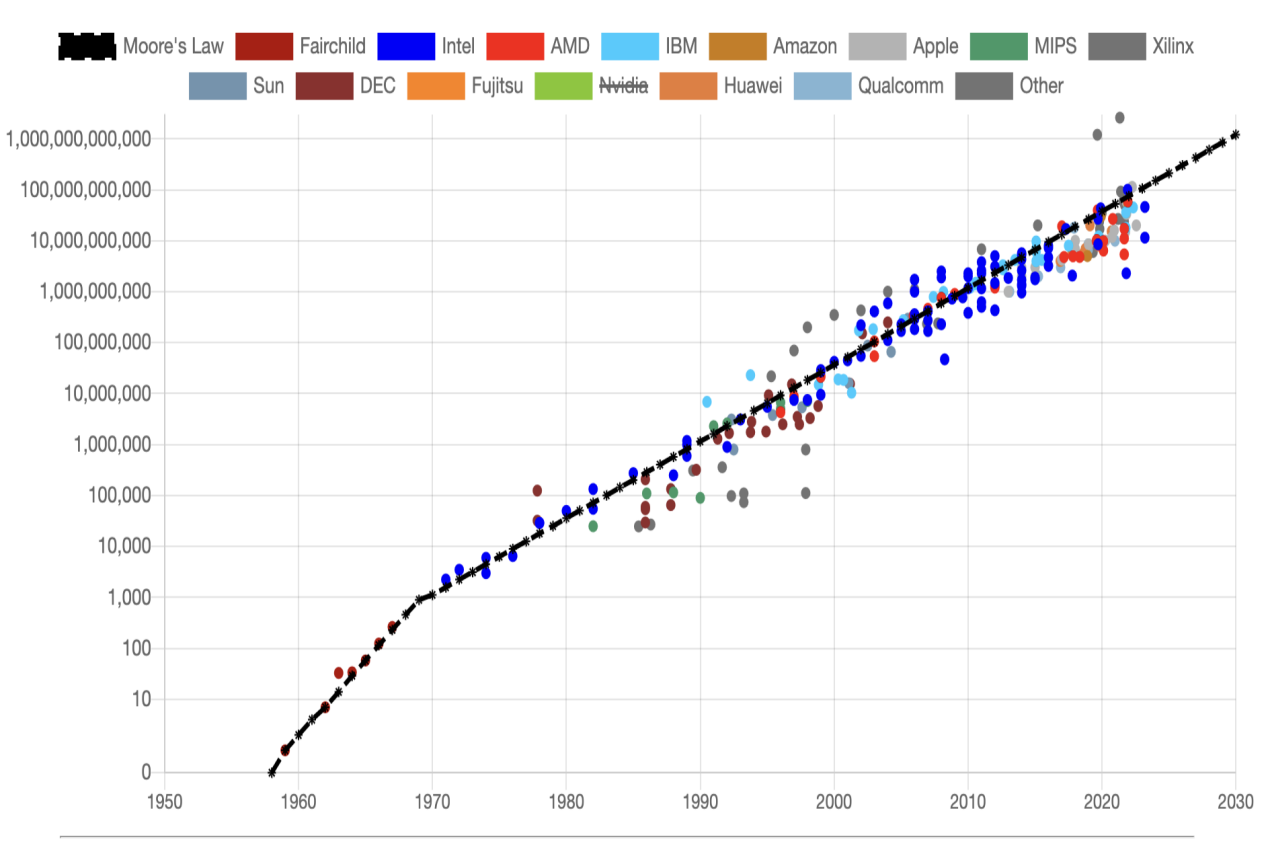

晶体管数量趋势与摩尔定律曲线 / David Schor

最后我们放出这张完整的图,在这几十多年晶体管数目激增的局势下,其实真正突破摩尔定律还是一件难事,这也是我们不断重复摩尔定律已死的原因。但我们看到新的设计思路也在涌现,无论是堆小芯片的Chiplet,还是单个大裸片的Wafer-Scale,未来这样的创新会持续爆发,但先行的肯定是数据中心这样的HPC领域。

即便如此,晶体管数量的增加趋势其实仍有一定的参考价值,虽然各大厂商也不能完全遵循这一趋势,但基本也不会偏离太远。国外分析师David Schor为此做了一个摩尔定律追踪图,直白地显示各大厂商的芯片产品与摩尔定律存在多少偏差。

老牌厂商的跌宕起伏

最初摩尔定律的提出,就是对CPU性能的提升做一个参照,所以我们先来看看英特尔和AMD两家x86巨头是否好好遵循摩尔定律。

英特尔、Xilinx/AMD产品晶体管数量趋势 / David Schor

从上图中可以看出,近年来两家的CPU、GPU产品基本都位于摩尔定律的晶体管数目之下,只有少数数据中心级别的GPU能够达标,比如英特尔的Xe HPC架构GPUPonto Vecchio、AMD的CDNA2 .0架构GPU Aldebaran,这些GPU产品要么用了MCM结构要么用了Chiplet设计,所以在晶体管数量上占据一定优势很正常。

至于图中那些高于摩尔定律的点,绝大多数并不是CPU、GPU芯片,而是Altera/英特尔和Xilinx/AMD的FPGA。对于追求最大化逻辑单元数的FPGA来说,超过摩尔定律可以说是必经之路,哪怕是这几年工艺发展变慢的情况下,英特尔的Stratix 10系列和Xilinx的Versal系列FPGA,也凭借着率先使用异构与Chiplet保持着较高的晶体管数目。

ARM的崛起

2010年之后,智能手机开始普及,也象征着ARM的崛起。以高通和苹果为首的一众手机/手机芯片厂商,开始追求如何在手机芯片极小的面积上,做到尽可能多的晶体管数量。这些手机处理器之间的竞争也在推动台积电等代工厂之间开始对先进工艺的疯狂追求,当然了手机SoC在这上面追求的表面上是高性能,其实还是高能效,至于朝摩尔定律曲线看齐,完全不是他们的目标。

ARM芯片晶体管数量趋势 / David Schor

从上图可以看出,无论是苹果、华为,还是高通,他们设计的ARM手机SoC都没有超过这条摩尔定律曲线。毕竟手机作为消费产品,处理器并不能占据全部的卖点,在面积、功耗、成本等各方面考量之下,手机SoC设计厂商都没有选择狂堆晶体管的方案。哪怕是苹果的A系列处理器,也只有对面积要求不高的A8X、A12X这样的平板SoC略微靠近了摩尔定律曲线。

但手机SoC从来都不是ARM追求晶体管数量的终点,这个任务将由数据中心的Arm处理器来完成。在上图的曲线中,有一些代表ARM处理器的点已经基本与摩尔定律曲线重合了,甚至还有超过的。

我们先来看下这几个与曲线重合的点,它们分别是高通的Centriq,亚马逊的Graviton 2/3、华为的鲲鹏920和阿里巴巴的倚天710,这些无一例外都是用于数据中心的ARM处理器。在数据中心这种场景下,无论是哪家厂商追求的都是最高的性能,所以如此多的晶体管数量也见怪不怪了。至于那个唯一超过的点则是苹果的M1 Ultra,其面积也达到了860mm2,M1的八倍之多。苹果在这颗庞大的芯片上塞入了1140亿个晶体管,完全超出了同期的竞争对手。

其他值得一提的厂商

其他芯片的晶体管数量趋势 / David Schor

对于一些刚成立不久的公司来说,他们的目标不是为了追求更高的晶体管密度。但对于一些AI/ML芯片初创公司,或者像上面提到的ARM芯片一样牵扯到数据中心,这些芯片的晶体管数目也少不了。在上图中,近年来接近摩尔定律曲线的也有不少,比如阿里巴巴的自研架构AI推理芯片含光800、Graphcore的WoW 3D封装IPU芯片Colossus MK2、Esperanto的千核RISC-V AI芯片ET-SoC-1,还有特斯拉为其Dojo超算打造的AI芯片D1。

你可能在看图时已经注意到了远在摩尔定律曲线之上的那两个点,是谁拥有如此可怕的设计实力,晶体管数目甚至超过了2030年的摩尔定律曲线呢?答案自然就是最大芯片尺寸的纪录保持者,坚持Wafer-Scale的Cerebras。Cerebras在去年发布的Wafer Scale Engine 2面积达到了46225mm2,近乎M1 Ultra芯片的54倍,接近一个12英寸晶圆的大小。别看Cerebras的第二点与第一个点的Wafer Scale Engine一代没差多少,这只是因为这个图的规模放不下了,因为Wafer Scale Engine 2的晶体管数量已经达到了可怕的26000亿。

晶体管数量趋势与摩尔定律曲线 / David Schor

最后我们放出这张完整的图,在这几十多年晶体管数目激增的局势下,其实真正突破摩尔定律还是一件难事,这也是我们不断重复摩尔定律已死的原因。但我们看到新的设计思路也在涌现,无论是堆小芯片的Chiplet,还是单个大裸片的Wafer-Scale,未来这样的创新会持续爆发,但先行的肯定是数据中心这样的HPC领域。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

cpu

+关注

关注

68文章

11365浏览量

226320 -

摩尔定律

+关注

关注

4文章

640浏览量

81186

发布评论请先 登录

相关推荐

热点推荐

封测巨头全球“圈地”,先进封装正成为AI时代的战略制高点

2026年全球半导体封测巨头密集扩产,日月光六厂同步动工、三星越南投建封测厂,先进封装突破摩尔定律瓶颈,成AI算力竞赛关键,解析行业扩产趋势与技术难题。

Chiplet,改变了芯片

1965年,英特尔联合创始人戈登·摩尔提出了“摩尔定律”。半个多世纪以来,这一定律推动了集成电路(IC)性能的提升和成本的降低,并成为现代数字技术的基础。摩尔定律指出,半导体芯片上的晶

【2025九峰山论坛】破局摩尔定律:异质异构集成如何撬动新赛道?

在半导体产业不断演进的历程中,异质异构集成技术正逐渐成为推动行业突破现有瓶颈、迈向全新发展阶段的关键力量。在这样的产业变革背景下,九峰山论坛暨化合物半导体产业博览会于武汉光谷盛大召开,吸引了来自美国

华大九天Vision平台重塑晶圆制造良率优化新标杆

摩尔定律驱动下,半导体产业正步入复杂度空前的新纪元。先进工艺节点的持续突破叠加国产化供应链的深度整合,不仅推动芯片性能实现跨越式发展,更使良率管理面临前所未有的技术挑战。纳米级尺度

【「AI芯片:科技探索与AGI愿景」阅读体验】+工艺创新将继续维持着摩尔神话

。那该如何延续摩尔神话呢?

工艺创新将是其途径之一,芯片中的晶体管结构正沿着摩尔定律指出的方向一代代演进,本段加速半导体的微型化和进一步集成,以满足AI技术及高性能计算飞速发展的需求。

CMOS工艺从

发表于 09-06 10:37

借助AMD无顶盖封装技术应对散热挑战

随着电子行业向更小节点迈进,现代应用要求更高的时钟速率和性能。2014 年,斯坦福大学教授 Mark Horowitz 发表了一篇开创性的论文,描述半导体行业面临相关登纳德缩放及摩尔定律失效的挑战

当摩尔定律 “踩刹车” ,三星 、AP、普迪飞共话半导体制造新变革新机遇

,揭示行业正处于从“晶体管密度驱动”向“系统级创新”转型的关键节点。随着摩尔定律放缓、供应链分散化政策推进,一场融合制造技术革新与供应链数字化的产业变革正在上演。

AI狂飙, FPGA会掉队吗? (上)

摩尔定律说,集成电路上的晶体管数量大约每两年翻一番。随着晶体管尺寸接近物理极限,摩尔定律的原始含义已不再适用,但计算能力的提升并没有停止。英伟达的SOC在过去几年的发展中,AI算力大致为每两年翻一番

先进封装转接板的典型结构和分类

摩尔定律精准预言了近几十年集成电路的发展。然而,逐渐逼近的物理极限、更高的性能需求和不再经济的工艺制程,已引发整个半导体行业重新考虑集成工艺方法和系统缩放策略,意味着集成电路产业已经步入后摩尔时代。

Chiplet与3D封装技术:后摩尔时代的芯片革命与屹立芯创的良率保障

在摩尔定律逐渐放缓的背景下,Chiplet(小芯片)技术和3D封装成为半导体行业突破性能与集成度瓶颈的关键路径。然而,随着芯片集成度的提高,气泡缺陷成为影响封装良率的核心挑战之一。

晶心科技:摩尔定律放缓,RISC-V在高性能计算的重要性突显

运算还是快速高频处理计算数据,或是超级电脑,只要设计或计算系统符合三项之一即可称之为HPC。 摩尔定律走过数十年,从1970年代开始,世界领导厂商建立晶圆厂、提供制程工艺,在28nm之前取得非常大的成功。然而28nm之后摩尔定律

突破!华为先进封装技术揭开神秘面纱

在半导体行业,芯片制造工艺的发展逐渐逼近物理极限,摩尔定律的推进愈发艰难。在此背景下,先进封装技术成为提升芯片性能、实现系统集成的关键路径,成为全球科技企业角逐的新战场。近期,华为的先进封装技术

摩尔定律下,真的有厂商实现了突破吗?

摩尔定律下,真的有厂商实现了突破吗?

评论