学习内容

关于AXI总线协议的一些简单知识,通过阅读Xilinx的使用指导手册(UG1037),结合正点原子的ZYNQ视频进行梳理总结。

AXI

AXI(Advanced eXtensible Interface) 高级扩展接口是ARM AMBA的一部分。(AMBA(Advanced Microcontroller Bus Architecture) 高级微控制器总线架构)

AMBA:高级微控制器总线架构,是1996年首次引用的一组微控制器总线协议。开放的片内互联的总线标准,能在多主机设计中实现多个控制器和外围设备之间的连接和管理。在Xilinx公司的芯片也广泛地使用AXI接口用于开发和设计。使用axi总线接口可以提高效率、开发的灵活性,以及可移植性。

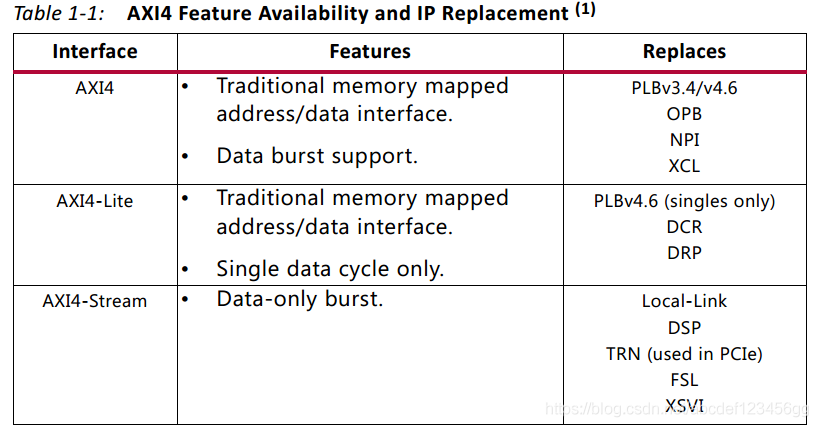

AXI4 三种类型

AXI4(AXI4-Full)

AXI4(AXI4-Full):用于高性能的存储器映射需求;(存储器映射:主机在对从机进行读写操作时,指定一个目标地址,这个地址对应系统存储空间的地址,表示对该空间进读写操作。)AXI4用于存储器映射接口,允许高达256个数据的的高吞吐量突发传输,并且传输周期只需要一个地址。

AXI4-Lite

AXI4-Lite:简化版的AXI4接口。用于低吞吐率存储器映射的通信。AXI4-Lite是一个轻量级、单次传输存储器映射接口。它使用了少量的逻辑器件进行实现总线功能,AXI4-Lite接口简单,在设计开发中简单易用。

AXI4-Stream

AXI4-Stream:用于高速的流数据通信。AXI4-Stream完全去除了对地址的需求,并允许无限制数据大小的数据突发的数据传输。AXI4-Stream接口在传输时没有使用地址单元,所以不是存储器映射。所以在对于那些只关心数据,对地址不关心或者没有地址需求的接口,可以采用AXI4-Stream接口。

AXI的工作方式

AXI4和AXI4-Lite包含5个独立的通道:

写地址通道

读地址通道

写数据通道

读数据通道

写响应通道

数据可以同时在主机和从机之间双向移动,并且数据传输大小可以不同。AXI4中的限制是一个突发传输最多可以传输256个数据。AXI4-Lite只允许单次传输一个数据。

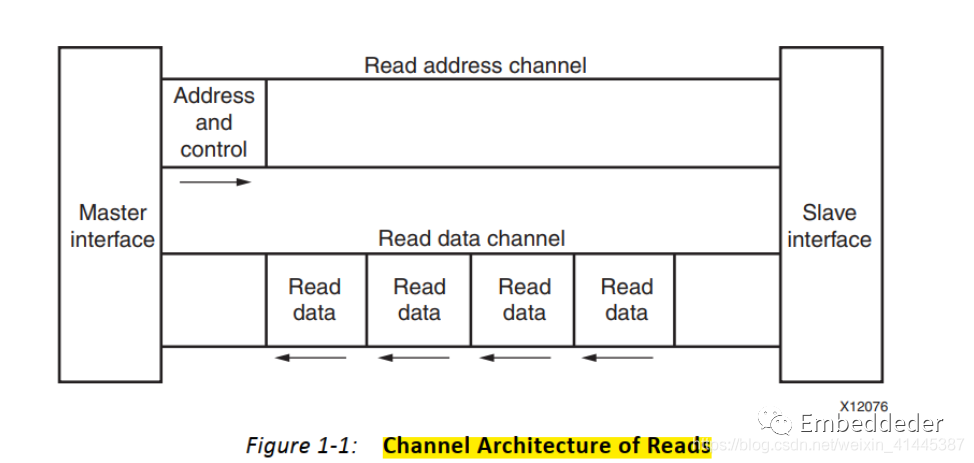

读取数据

下图演示了AXI总线如何进行读取数据的操作: 首先由主机通过读取地址通道发送地址和读操作的指令,在从机接收到读操作,并正确读取从主机发送的地址,通过读取数据通道将数据由从机发送到主机。

首先由主机通过读取地址通道发送地址和读操作的指令,在从机接收到读操作,并正确读取从主机发送的地址,通过读取数据通道将数据由从机发送到主机。

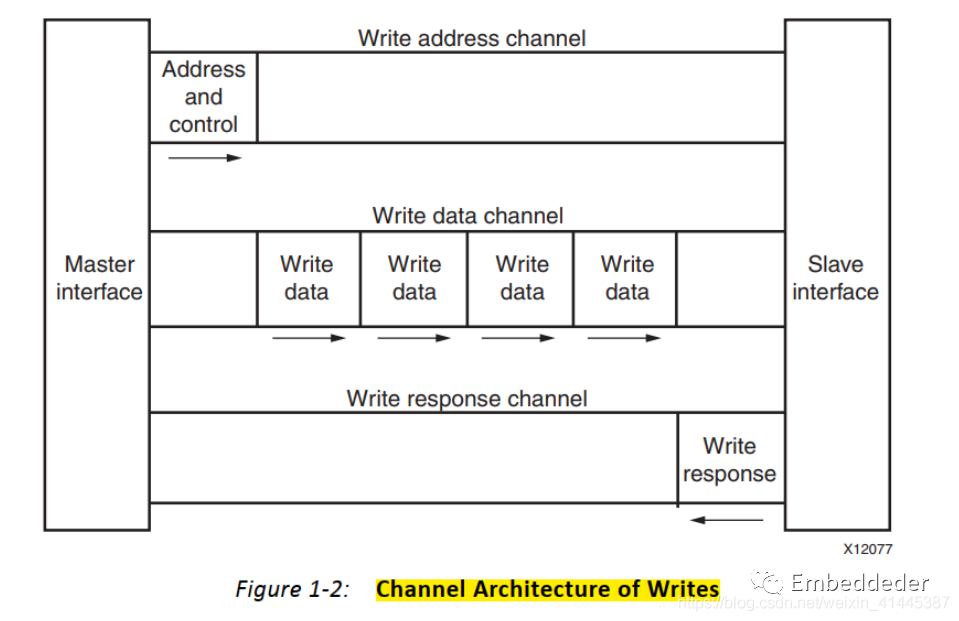

写入数据

下图演示了AXI总线如何进行写入数据的操作: 首先由主机通过写入地址通道发送地址和写操作的指令,在从机接收到写操作,开始接收主机从读取数据通道发送的数据信息并写入从机,当完成写入操作后,写响应通道将回应写响应。

首先由主机通过写入地址通道发送地址和写操作的指令,在从机接收到写操作,开始接收主机从读取数据通道发送的数据信息并写入从机,当完成写入操作后,写响应通道将回应写响应。

存储器映射协议

通过赋予每个任务不同的虚拟–物理地址转换映射,支持不同任务之间的保护。地址转换函数在每一个任务中定义,在一个任务中的虚拟地址空间映射到物理内存的一个部分,而另一个任务的虚拟地址空间映射到物理存储器中的另外区域。就是把一个地址连接到另一个地址。

AXI4-Stream协议

AXI4-Stream协议用于通常用于以数据为主和数据流的应用实例中,其中不存在或不需要地址的概念。每个AXI4-Stream都充当一个单向通道,并带有一个握手数据流。

连接存储器映射和 AXI4-Stream

一种常见的方法是构建将AXI4-Stream和AXI内存映射IP结合在一起的系统。通常,DMA的IP可用于将数据流移入或移出内存。例如,处理器可以与DMA一起工作来解码数据包,或者在流数据之上实现一个协议栈,从而构建更复杂的系统,使数据在不同的应用程序空间或不同的IP之间移动。

使用HLS添加AXI接口

在HLS中支持函数自动综合生成下面的AXI总线接口:• AXI4-Stream (axis)• AXI4-Lite slave (s_axilite)• AXI4 master (m_axi)

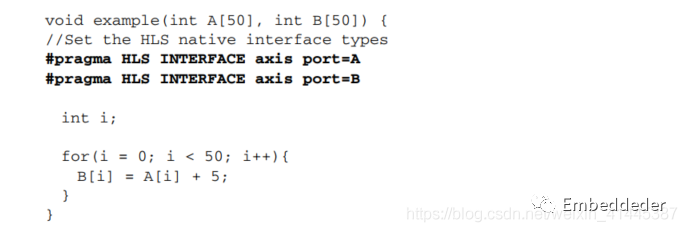

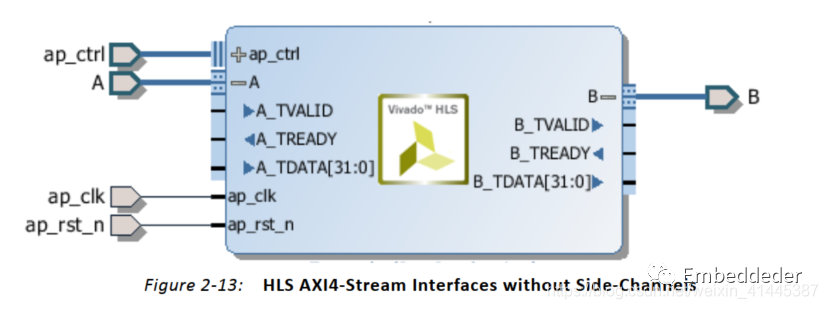

HLS AXI4-Stream Interface

你可以将AXI4-Stream接口(axis模式)应用于任何输入参数和任何数组或指针输出参数。因为axis 4- stream接口以顺序流的方式传输数据,所以不能与既可读又可写的参数一起使用。在设计时候又分为带side-channel和不带side-channel。带side-channel:使用带有边通道的axis4 - stream接口提供了额外的功能,允许作为组件的一部分的可选side-channel AXI4-Stream标准,可直接用于C代码。(这里我的理解是使用axi接口做了拓展功能)不带side-channel:使用AXI4-Stream 时候,数据类型不包含任何AXI4 side-channel的参数。(这里我的理解是仅仅使用数据流的交互)下面给出一个HLS设计的实例: 综合后对于A、B两个端口,都被定义为了AXI4-Stream的接口。而多了VALID和READY用于检测数据的是否有效和准备状态。

综合后对于A、B两个端口,都被定义为了AXI4-Stream的接口。而多了VALID和READY用于检测数据的是否有效和准备状态。

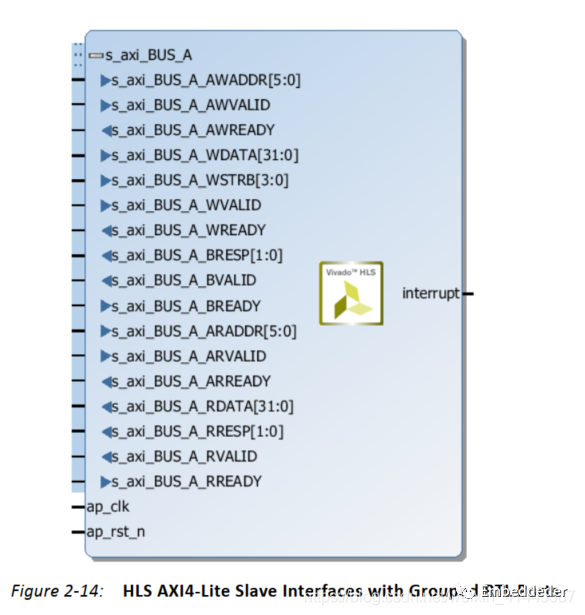

HLS AXI4-Lite Interface

AXI4-Lite slave接口通常用于可以被微控制器和处理器控制的外设和设备接口。AXI4-Lite slave接口的Vivado HLS特性(s_axilite模式):

将多个端口分组到同一个AXI4-Lite从接口。

将设计导出到Vivado IP目录时,输出C函数和头文件以与处理器上运行的代码一起使用。下面给出一个多个不同端口分配到一个接口的实例:

void example(char *a, char *b, char *c)

{

#pragma HLS INTERFACE s_axilite port=return bundle=BUS_A

#pragma HLS INTERFACE s_axilite port=a bundle=BUS_A

#pragma HLS INTERFACE s_axilite port=b bundle=BUS_A

#pragma HLS INTERFACE s_axilite port=c bundle=BUS_A

*c += *a + *b;

}

综合后的结果:

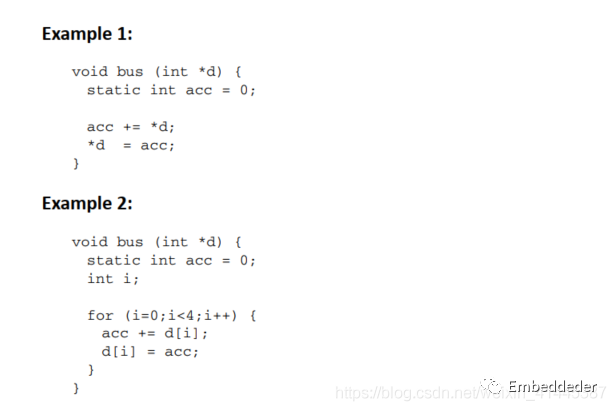

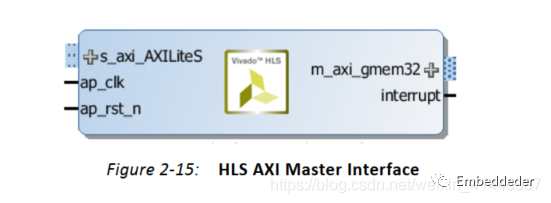

HLS AXI4 Master Interface

您可以在任何数组或指针/引用参数、实现HLS AXI4 Master接口(m_axi模式)。该接口使用两种模式:一是单独的数据传输,二是使用C memcpy功能的突发模式数据传输。单独的数据传输模式: 在这两个例子中,通过AXI4 Master接口进行的数据传输都是简单的读或写操作:一次传输一个地址和一个数据值。突发模式传输: 突发模式使用一个单一的基址传输数据,该基址后面跟着多个连续的数据样本,并且能够实现更高的数据吞吐量。只有在使用C memcpy函数将数据读入或读出用于合成的顶级函数时,才可能使用突发模式。下面给出一个具体实例:

在这两个例子中,通过AXI4 Master接口进行的数据传输都是简单的读或写操作:一次传输一个地址和一个数据值。突发模式传输: 突发模式使用一个单一的基址传输数据,该基址后面跟着多个连续的数据样本,并且能够实现更高的数据吞吐量。只有在使用C memcpy函数将数据读入或读出用于合成的顶级函数时,才可能使用突发模式。下面给出一个具体实例:

void example(volatile int *a){

#pragma HLS INTERFACE m_axi depth=50 port=a

#pragma HLS INTERFACE s_axilite port=return bundle=AXILiteS

//Port a is assigned to an AXI4-master interface

int i;

int buff[50];

// memcpy creates a burst access to memory

memcpy(buff,(const int*)a,50*sizeof(int));

for(i=0; i < 50; i++){

buff[i] = buff[i] + 100;

}

memcpy((int *)a,buff,50*sizeof(int));

}

当你用前面的例子合成一个设计时,它会产生如下图所示的接口(AXI接口):

原文标题:使用HLS添加AXI接口

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

-

存储器

+关注

关注

38文章

7502浏览量

163933 -

接口

+关注

关注

33文章

8617浏览量

151311 -

AXI总线

+关注

关注

0文章

66浏览量

14269

原文标题:使用HLS添加AXI接口

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Xilinx zynq AXI总线全面解读

AXI总线协议的几种时序介绍

玩转Zynq连载3——AXI总线协议介绍1

AMBA3.0 AXI总线接口协议的研究与应用

AXI总线协议的几种时序介绍

AMBA 3.0 AXI总线接口协议的研究与应用

AXI总线协议简介

AXI总线协议:AHB、APB、AXI对比分析

SoC设计中总线协议AXI4与AXI3的主要区别详解

AXI总线协议的简单知识

AXI总线协议的简单知识

评论