不知道UVM中的field automation机制怎么翻译,不管了,反正就是**机制,理解它能干啥就行了。

UVM中的field automation机制提供了2类宏,也可以理解为有2个用途。

第一类

uvm_object_utils_begin(TYPE) 和uvm_object_utils_end 宏用来声明几个uvm object基本的pure virtual 方法。

1.1 get_type_name() ,返回对象的类型,是一个字符串类型

1.2 create() 实例化一个对象,利用了工厂机制。对象类型能被override。

1.3 get_type()返回对象类型,用于工厂机制

第二类

`uvm_field_* 宏指定特定的属性域段所支持的方法(print(), copy(), clone(),

pack(), unpack(), compare()等等).

`uvm_field_*(field_name, flags)

1 class packet_header extends uvm_object;

2 rand bit [5:0] length;

3 rand bit [1:0] addr;

4 `uvm_object_utils_begin(packet_header)

5 `uvm_field_int(length, UVM_DEFAULT)

6 `uvm_field_int(addr, UVM_DEFAULT)

7 `uvm_object_utils_end

8 endclass : packet_header

上面的代码示例展示了这2类宏的配合使用方式。

不管你赞不赞同,这种用户类的声明继承方式已经是深入人心的UVM代码风格了。

你需要知道,每一次继承UVM基类去声明一个新的类,都需要有这些模版式的代码。

-

UVM

+关注

关注

0文章

182浏览量

19167

原文标题:UVM中的Field Automation

文章出处:【微信号:芯片验证工程师,微信公众号:芯片验证工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

IC验证"UVM验证平台"组成(三)

IC验证"一个简单的UVM验证平台"是如何搭建的(六)

IC验证"UVM验证平台加入factory机制"(六)

IC验证“UVM验证平台加入objection机制和virtual interface机制“(七)

数字IC验证之“什么是UVM”“UVM的特点”“UVM提供哪些资源”(2)连载中...

什么是uvm?uvm的特点有哪些呢

如何构建UVM寄存器模型并将寄存器模型集成到验证环境中

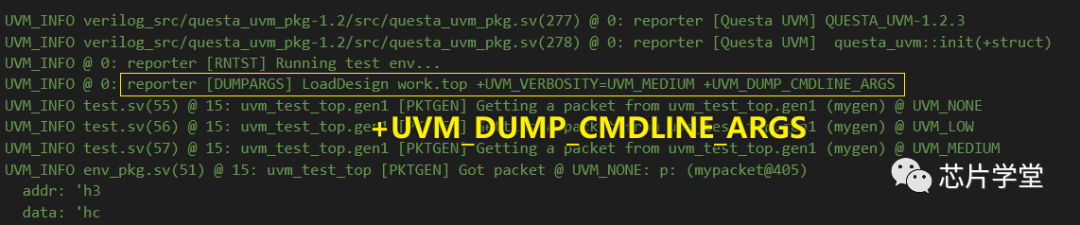

谈谈UVM中的uvm_info打印

UVM实战卷1 PDF电子书免费下载

UVM sequence机制中response的简单使用

浅析UVM不同机制的调试功能

UVM中的field automation机制有哪些用途

UVM中的field automation机制有哪些用途

评论