本文作者:赛灵思工程师 Vivek Krishna Kanchanapalli

赛灵思 Fast Fourier Transform (FFT) IP 具有专用于处理 FFT 输出中的位增长的缩放因子。本文旨在提供有关此 IP 中可用缩放方法的见解,并提供缩放调度选择方法以避免出现文中所述的溢出问题。

缩放原因:

《快速傅里叶变换 (Fast Fourier Transform) 产品指南》(PG109) 中对于缩放的解释如下:用于实现 FFT 算法的算术运算可能导致位增长,而使用缩放则可避免出现此问题。在 Radix-2 和 Radix-4 FFT 实现的最差情况下,可能会出现这种位增长问题。

在Radix-2 蝶形中,其输出可能按 1+sqrt(2) 的因子(即 2.414)出现增长。因此,在此情况下根据用于 FFT 的有符号格式,输出将增长 2 位。同样,Radix-4 的输出可能按 1+3sqrt(2)=5.24 的因子出现增长,即增长 3 位。

后续每个蝶形阶段都会引入这种位增长的问题(作为最差情况)。如果输出中的位数必须与输入中的位数相同,那么该位增长问题必须得到妥善处理。

对于 Radix-4,根据缩放调度中的值,其中位元可向右移 1、2 或 3 位。对应的输出值将缩小 2^(缩放值),这样结果即可得到妥善处理,且输出中不发生任何位增长。

如果不使用缩放,则会导致出现如上所述的位增长,即未经缩放的输出中包含整数值。输出精度将包含整数部分,而二进制小数点则仍位于输入精度中小数点所在相同位置。综上,输出精度为 (C_INPUT_WIDTH + C_NFFT_MAX + 1) 位,且在二进制小数点之后仍有 (C_INPUT_WIDTH - 1) 个小数位。

缩放类型:

仅当数据格式为定点类型时,FFT IP 中的“缩放 (Scaling)”选项才可用。假定 FFT IP 的输入精度类型为 Fix(C_INPUT_WIDTH,C_INPUT_WIDTH - 1)。

FFT IP 中有 3 个缩放选项可供使用:

1. 未缩放 (Unscaled)

2. 已缩放 (Scaled)

3. 块浮点 (Block Floating Point)

Unscaled:正如其名,对 FFT IP 中的数据不应用任何缩放。这会导致输出中出现位增长。在此情况下,输出精度将包含整数部分,LSB 中的增长将被截断或舍入。此时,输出精度为“Fix(C_INPUT_WIDTH + C_NFFT_MAX + 1, C_INPUT_WIDTH - 1)”,其中,给定的“C_NFFT_MAX”为 log2(maximum FFT point size)。

Scaled:通过在每个 FFT 阶段中对位元执行右移,从而使 FFT IP 的输出缩小。每个阶段的相移量是使用 scaling_sch 来设置的,并使用 FFT IP 上的“配置接口 (Configuration interface)”来提供此相移量。由于进行了缩放,FFT IP 的输出精度与输入精度相同,即,Fix((C_INPUT_WIDTH,C_INPUT_WIDTH - 1)。

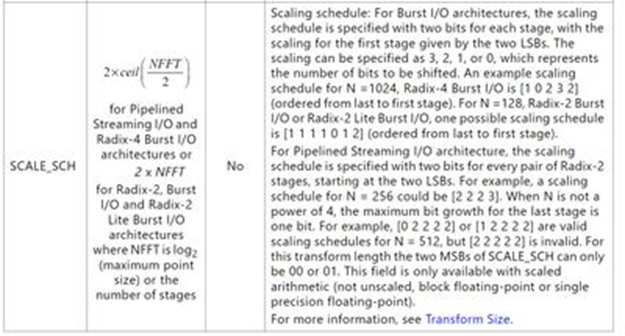

为每个阶段提供足够的缩放时请务必谨慎,否则,可能会发生溢出,导致数据卷绕。一旦发生溢出,则可能导致无法继续在应用中使用这些数据。(PG109) 描述了 Vivado 中的 FFT IP、C/Mex 模型和 System Generator 中的 FFT IP 块的缩放调度字段的宽度和格式。

Block Floating point (BFP):

在此模式下,核会自动判定缩放值,它会以最佳方式使用可用动态范围,并避免溢出。输出精度与输入精度相同,即 Fix((C_INPUT_WIDTH,C_INPUT_WIDTH - 1)。核所应用的位元右移总数的输出结果为“m_axis_data_tuser”接口和“m_axis_status_tdata”接口上的指数值 (blk_exp)。缩放因子计算方式为 (2^blk_exp)。由于该核自动计算缩放值,它会使用附加资源,从而导致资源计数比“scaled”模式下的资源数更高。

判定缩放调度:

在 FFT IP 中使用 scaled 模式时,需通过运行系统仿真来判定用于避免溢出的缩放调度。

对于特定类型的输入数据中的大部分帧而言,要选出能够避免溢出的最佳缩放值,可能难度较大。在此情况下,可使用 C 语言模型工具来帮助选择缩放调度。

在每个阶段中,对典型输入数据集运行仿真时,通过监控状态总线中的溢出信号,可以判定适用缩小还是放大。(PG109) 的第 5 章对 FFT C 语言模型和 MATLAB 模型进行了详细解释。

(PG109) 还描述了适用于每种 FFT 架构类型的保守缩放调度方法。此缩放调度可避免所有数据类型出现溢出。

如果 N=1024

Radix-4 突发 I/O:[10 10 10 10 11]

流水打拍式串流 I/O:[10 10 10 10 11]

Radix-2 突发 I/O 或 Radix-2 轻量级突发 I/O:[01 01 01 01 01 01 01 01 01 10]

保守型缩放调度可根据“N”的值进行进一步扩展或缩减。

例如,在流水打拍式串流模式下,保守型缩放调度如下:

如果 N=512:[01 10 10 10 11]

如果 N=2048:[01 10 10 10 10 11]

虽然保守型缩放可阻止所有输入值出现溢出,但由于过度缩放,它也会减小输出值。这可能导致无法有效利用输出值的可用动态范围,并导致输出值过度缩放。由此导致需要执行仿真才能判定相应的缩放因子,使所提供的输出既能有效利用可用动态范围同时也能避免溢出。

另一种缩放值的判定方法是在 Block-Floating Point (BFP) 模式下使用 FFT IP。FFT C 语言模型可在 BFP 模式下使用,并可对输入数据运行仿真。BFP 将在状态接口中生成块指数值,以指示核所应用的缩放量,从而以最有效方式利用输出的动态范围并避免输出发生溢出。

由于 BFP 下的块指数表示核内部的位元相移数,因此“Scaled”模式下的缩放调度的相移位数可设置为与之相同的值。例如,在 BFP 模式下且 N=1024,如果块指数值为“9”,那么“Scaled”模式下的“scaling_ sch”可设置为相移 9 位。有多种方法可用于在不同 FFT 阶段间实现相同的位移,遵循保守型缩放调度模式正是其中一种适合的“scaling_sch”配置方法。

在以上示例中,块指数值 9 可在“Scaling_sch”中配置为 ( 00 10 10 10 11),从而导致相移 9 位。此缩放调度所提供的输出比保守型缩放调度更好,后者可能导致数据过度缩放。

示例:

在 MATLAB 中,FFT Mex 模型的用途示例之一就是用于观测缩放对于输出的影响。由于使用了 Mex 模型,因此数据图也可供使用。在此示例中,FFT 含 14 种不同输入帧,并针对每个帧使用不同缩放调度来执行计算。MEX 文件包含在本文随附的 ZIP 文件内。

首先,在 BFP 模式下配置 FFT,并将其用于判定每个帧的块指数。随后,在 scaled 模式下配置 FFT,并通过将 scaling_schedule 设置为如下值来计算每个帧:

1. 保守型缩放值。

2. 等同于 BFP 模式下针对该帧获取的块指数的缩放值。

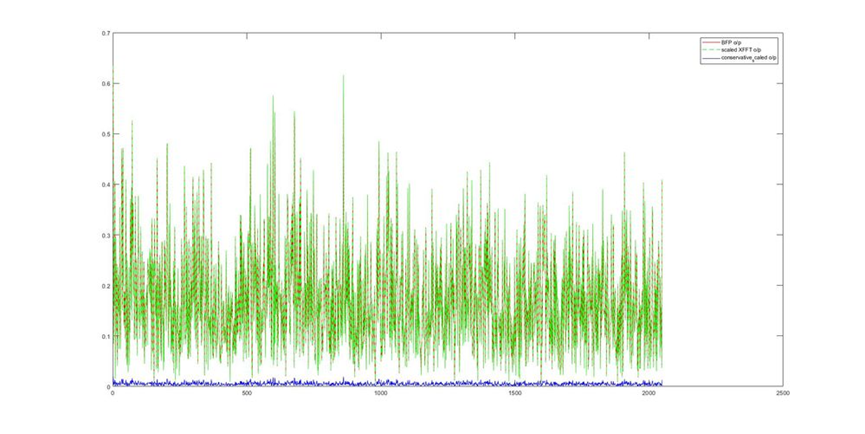

随后,即可绘制出通过 Block Floating pointing (BFP) 模式和 Scaled 模式使用上述缩放因子获取的 FFT 的量级。图例如下。在图中可以观测得知,保守型缩放导致数据缩放过度,并避免了溢出,而含块指数输出的 BFP 输出和 Scaled FFT 输出则可提供更高输出量级,同时避免溢出。

示例的局限性:此示例使用的 .txt 文件含 14 帧,每帧含 2048 个样本。要检查其它 FFT 点数大小“N”,请生成含“N”个样本的数据帧。

FFT IP 输出。红线 - BFP 模式输出,绿色虚线 - Scaled 模式下的 FFT IP 输出,缩放因子设置为块指数,蓝色 - 使用保守型缩放因子的输出。

说明:

此处随附的 m 脚本需要使用 FFT IP C 语言模型文件。要运行此示例,请将该目录解压,将示例文件(m 脚本和文本文件)复制到在 Vivado 中生成 FFT IP 输出文件时所创建的 C 模型目录中。

完成文件复制后,需构建专为 FFT 提供的 Mex 文件 (make_xfft_v9_1_mex.m)。如需获取有关使用 FFT C 语言模型的更多指示信息,请参阅 (PG109) 第 5 章:C 语言模型。

PG109:

https://china.xilinx.com/support/documentation/ip_documentation/xfft/v9_1/pg109-xfft.pdf

审核编辑:汤梓红

-

赛灵思

+关注

关注

32文章

1794浏览量

131733 -

IP

+关注

关注

5文章

1739浏览量

150391 -

FFT

+关注

关注

15文章

438浏览量

59816

原文标题:开发者分享|赛灵思 Fast Fourier Transform IP 中的缩放因子选择

文章出处:【微信号:gh_2d1c7e2d540e,微信公众号:XILINX开发者社区】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

赛灵思FFT IP中的缩放因子说明

赛灵思FFT IP中的缩放因子说明

评论