在系统级不断追求更高性能的过程中,集成设备制造商 (IDM) 已经精通开发能够在具有挑战性的电气环境中高速运行的。标准接口,如 SPI 和 I2C,提供了一种相对简单的方法,以可靠和有效的方式互连来自不同供应商的设备。其他类型的接口也是如此。

可以将数字域视为为希望使用“标准”技术快速构建复杂系统的开发人员提供的避风港。事实上,嵌入式行业很大程度上依赖于“正常工作”的基于标准的接口,因为它们为创新提供了框架。当它们不“正常工作”时,可能会导致混乱,尤其是在错误解释错误原因的情况下。任何混淆都是可以理解的,因为这些接口在按照规范应用时是健壮和可靠的。底层物理接口固定在硅片中的事实也可以提供保证。

各种形式的系统噪音、

信号的任何失真都可以被解释为噪声,并且可以合理地假设噪声在通信环境中最常见;收到的信号不是发送的信号。这种直接相关性比较容易找到,但在某些情况下,因果关系并不那么容易确定。当故障变得间歇性时,挑战变得更加复杂。

当今的微控制器旨在以最少的配置提供可靠的操作。在串行接口的情况下,这可能包括默认为 I/O 引脚上的高驱动电流,以对抗长 PCB 走线或高容性负载的影响。在某些情况下,这可能导致接口过度驱动,进而导致衍生效应被解释为错误或故障。

例如,串行闪存设备提供了许多高级功能,可确保可靠运行并允许对设备进行查询。这可以包括噪声过滤器、高级自适应编程和管理单元余量的擦除算法。一些制造商还在存储元件中包含 ECC,以在每次写入操作时保存额外的元数据,以允许检测和纠正单个或多个位错误,但当噪声破坏通信接口总线上的基本消息事务时,此 ECC 修复将无济于事。

SPI 接口上的噪声可能会被误解为额外的时钟脉冲。由于 SPI 是时钟驱动的接口,因此会产生一些影响,例如命令被忽略、数据被误解、使用错误命令等。但是,噪声也带有能量,在某些情况下,这种能量本身会在设备操作中引入错误.

电荷泵和过冲

在大多数情况下,数字接口可以容忍信号中的一些过冲或下冲。然而,不应忘记曲线下的能量仍然存在,并且在某些电路中这可能是破坏性的。

一个典型的例子是串行闪存中的电荷泵电路。如果 SPI 总线信号包含大量噪声,则该信号中的能量可能会传播到电荷泵并破坏其运行。

闪存中的电荷泵是一项关键功能,因为它提供了改变存储单元偏置所需的功率,并有效地存储逻辑 1 或 0。写入/擦除过程是闪存操作的关键时刻内存,在此期间对电荷泵的任何中断都可能导致写入或擦除错误,虽然可以检测到这些错误,但它们有可能不会很明显。

这种错误很容易被解释为闪存设备中的故障。嵌入式设计人员非常了解闪存具有制造商保证的有限数量的读写周期这一事实,但可能不太了解的是提供没有太多过冲或下冲的干净接口的重要性。

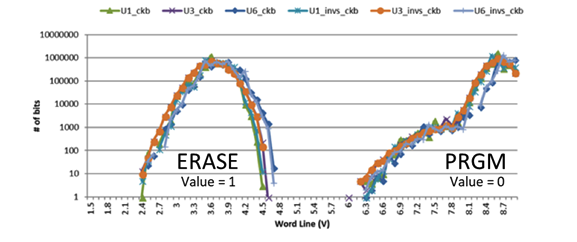

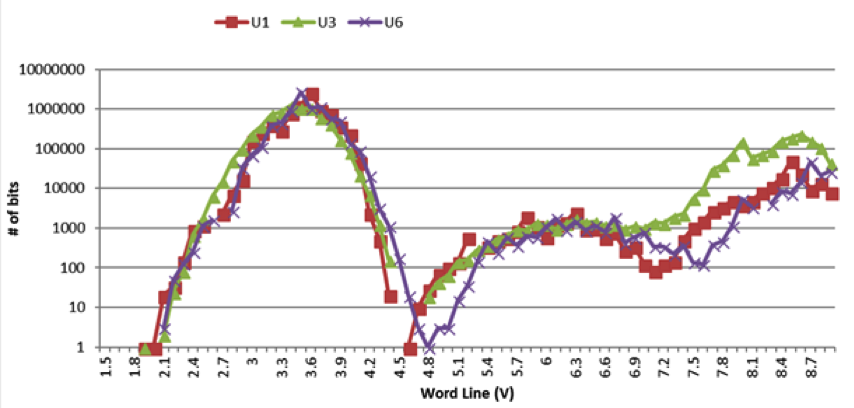

例如,考虑图 1 中的图像。它显示了六个闪存设备的健康单元边距。在用表示逻辑 1(2V 至 5V)和 0(>6v)的数据编程的单元之间出现了两种不同的模式。相比之下,图 2 中的图像显示了三个闪存设备的存储单元余量,这些设备因控制线上的过冲和下冲而遭受数据损坏。

图 1:该图显示了已编程和擦除的闪存的良好单元边缘分离数据。(来源:阿德斯托)

图 2:该图显示了闪存的单元边缘分离数据较差,其中 SPI 线路上存在明显的噪声。(来源:阿德斯托)

多种因素会影响噪声水平,例如工作频率、信号幅度、MCU 驱动水平以及噪声尖峰中包含的能量。PCB 设计和信号之间的串扰也可能是影响因素。

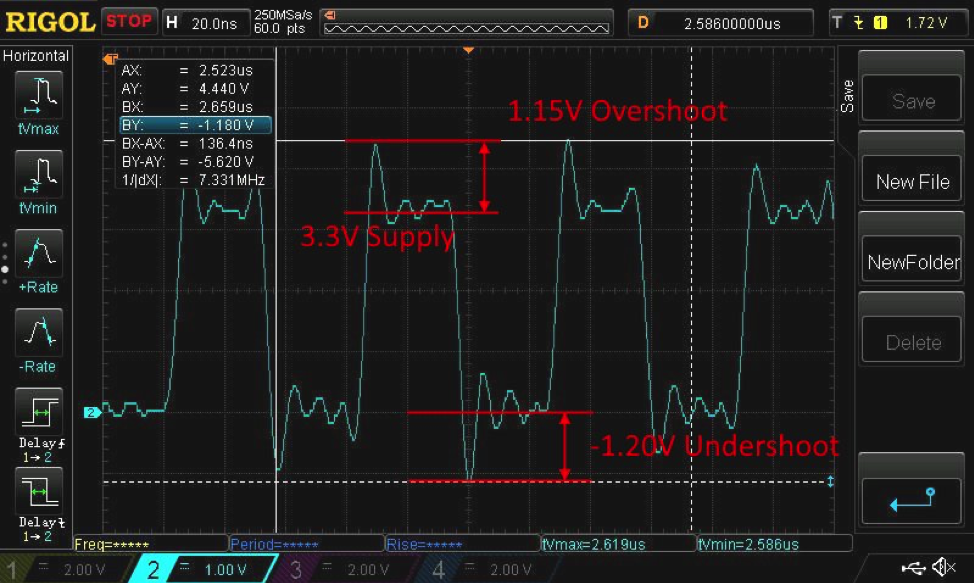

图 2 中的数据显示了过度过冲和下冲对串行接口的影响。下面的图 3 显示了这种过冲在实际应用中的样子。

图 3:此迹线图像清楚地显示了 SPI 线路上存在的过冲和下冲导致 5.65V 的峰峰值电压,超过了闪存规范中记录的绝对最大值。(来源:阿德斯托)

这种噪声的结果是错误的设备操作,表现为串行闪存存储值中的错误。最初,错误的真正影响被忽略了,因为以较低频率轮询状态寄存器报告的错误较少,导致设计人员对故障的根本原因做出错误的假设。

确定真正的根本原因

尽管此故障表现为内存故障,但根本原因并非闪存设备。Adesto 工程师通过探测 SPI 信号并识别存在的系统噪声发现了这一点。虽然噪声可能部分归因于 MCU 和闪存之间的 PCB 轨道上存在的阻抗不匹配,但这并不是全部。

噪声的来源实际上是 MCU 接口,它在上电时默认为高驱动电平。过度驱动足以导致 SPI 线路上的过冲和下冲,在某些情况下可能会被误解为信号转换,从而导致读取或写入错误。然而,在这种情况下,发现过冲具有足够的能量来破坏 Flash 电荷泵,这反过来又会导致错误。

在客户的设计中,所使用的微控制器为其 I/O 提供了可配置的驱动电流,在启动时默认为 HIGH。由于应用程序代码在初始化期间没有修改此级别,因此它在正常操作中保持高电平。

对于 SPI 总线上的其他设备,这种影响可能并不明显,因为数字接口通常被设计成稳健的。闪存的敏感特性,需要以更高的频率运行,特别是电荷泵的运行,使存储器容易出现过冲/下冲。这导致了最初被误解为闪存设备故障的错误操作。

纠正错误

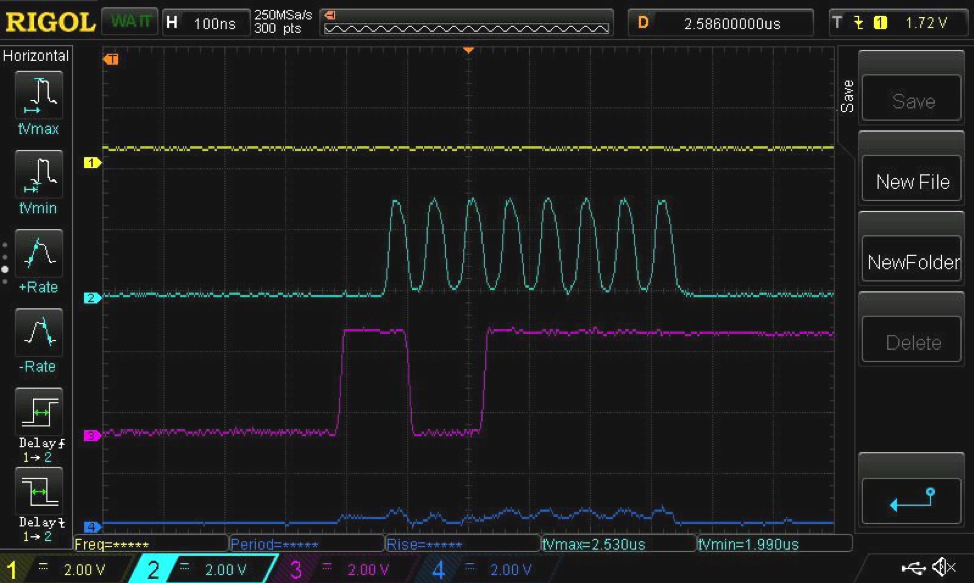

通过固件降低驱动电流可将过冲和下冲有效地减少为零(图 4),进而导致闪存的无错误运行。

图 4:没有明显的过冲,串行闪存的电荷泵能够正确运行并提供可靠的功能。(来源:阿德斯托)

故障的性质表明,Flash 设备正在尽一切努力补偿错误的影响,即 SPI 接口上的系统噪声过大。

也许这里最重要的一点是,原因实际上是所使用的 MCU 的设计特性,它默认为在大多数情况下完全可以接受的操作模式。高驱动输出和不完美的 PCB 电感相结合造成了导致间歇性故障的条件。通过简单的固件更改,减少 MCU 上的驱动输出,解决了这个问题。

这突出了这里真正的教训:看似真正的组件故障实际上可能是设计中的疏忽。更换存储设备本来是对最初认为是故障的自然反应,但通过客户和供应商以及硬件和软件工程团队之间的牢固工作关系,找到了实际原因并应用了正确的解决方案.结果是明显更好的设计、更高的系统性能和更高的可靠性。

结论

当没有明显影响时,系统噪音很容易被消除。在最佳条件下,间歇性错误特别难以定位,但当错误被误解时,挑战变得更加困难。

过冲可能是最不明显的系统噪声形式,但正如这里所解释的,它的影响可能很大。闪存是一种可靠的技术,但它依赖于精心设计的接口。串行接口上的过多噪声有可能传播到电荷泵电路,从而影响编程和擦除电路的操作。这会导致无法预料的特性,这些特性很容易被解释为设备本身的故障,表现为存储单元故障,以及不一致或不可靠的编程和擦除操作。

在这种情况下,更换闪存并假设问题已得到解决可能会导致产品上市,而这些产品可能会在某个时候失败。相反,设计人员能够将编程和擦除一致性提高一个重要因素,有效的耐久性从检测到错误之前不可接受的约 20K 周期跃升至超过 250 万个周期,没有错误,并且不需要补充错误检测和纠正例程。

现代微控制器提供的可配置性水平既可以看作是帮助,也可以看作是障碍。驱动电流可配置的事实可能是该示例中过冲的原因。然而,能够降低驱动强度对于解决问题也很有效。

-

闪存

+关注

关注

16文章

1814浏览量

115284 -

数字接口

+关注

关注

1文章

87浏览量

22129 -

IDM

+关注

关注

1文章

120浏览量

19010

发布评论请先 登录

相关推荐

昂科烧录器支持ISSI芯成半导体的串行闪存IS25WP128F

串行接口的工作方式有几种,串行接口的RXD1和TXD1是什么端口

异步串行接口有哪些,异步串行接口为何需要波特率

脉冲噪声对系统的影响

数字产品中电源轨噪声如何影响系统中时钟抖动

TLV320AIC3100接口中的SPKVDD、HPVDD是模拟电源还是数字电源?

航天级100krad隔离式串行外设接口(SPI)LVDS电路

航天级100krad隔离式串行外设接口(SPI)RS-422电路

如何让闪存多次编程呢?

如何将Littlefs安装到通过qspi连接到电路板的外部串行闪存上?

串行音频接口(SAI)中slot是什么意思?

昂科烧录器支持XinCun芯存科技的串行外设接口NAND闪存 XCSP4AAPK-IT

数字接口中的系统级噪声如何导致串行闪存中的虚假错误

数字接口中的系统级噪声如何导致串行闪存中的虚假错误

评论