瑞萨电子开发了一种新的内存处理器 (PIM) 技术,用于在低功耗边缘设备中加速 AI 推理。用于基于 SRAM 技术的测试芯片实现了 8.8 TOPS/W 的运行卷积神经网络 (CNN) 工作负载,这是最常用于图像识别的算法类型。

瑞萨电子现有一代 AI 推理加速器基于其动态可重构处理器 (DRP) 架构,达到 1 TOPS/W 量级,足以在终端节点实现实时图像识别。该公司表示,新的 PIM 技术在 TOPS/W 方面几乎提高了一个数量级,并且可能成为在端点实施增量学习的基础。

内存处理器是一种越来越流行的人工智能推理工作负载技术,其中涉及将大量输入数据与权重因子相乘。在 PIM 设备中,当读取数据时,在存储器本身中执行乘法累加 (MAC) 操作。

在瑞萨电子设备中,存储权重的存储单元可以通过控制单元的输出开关与输入数据相乘,从而控制输出电流。测量位线中的电流然后有效地将所有输出加在一起。以这种方式在内存中执行 MAC 操作,通过避免不必要的数据传输,消除了内存和处理器之间的瓶颈。

三元SRAM

在接受 EETimes 的独家采访时,瑞萨电子高级首席工程师 Koichi Nose 解释了用于提高精度和降低功耗的新技术。

“传统的内存处理器技术无法为大规模计算提供足够的精度,”Nose 说,并强调了传统上需要解决的变通办法,以规避由工艺变化引起的低可靠性。“二进制数据也不足以表达一些复杂的神经网络……它会导致准确性下降。”

新的 PIM 技术是三元的,这意味着每个单元都具有三种状态:-1、0 或 1。Nose 解释说,这允许表示比二进制单元更复杂的数据。

如果三进制存储单元保持+1或-1,则电流可以流入位线,但如果存储单元存储0,则没有电流流动,这有助于保持低功耗。

“此外,重量数据可以很容易地扩展到任意位数,”Nose 说。“神经网络中的权重数据是多位信息,一个零或一个大的正负值。在二进制单元中表达多位符号信息很困难。所提出的存储器电路可以通过利用三元单元和简单的数字计算块的组合来轻松表达任意符号位操作......因为这可以支持每个用户所需的不同计算精度,用户可以优化精度和精度之间的平衡能量消耗。”

能量消耗

Nose 表示,传统的 PIM 拓扑使用 ADC 将位线电流转换为输出数据值,但尽管 ADC 很有效,但它们耗电大且占用宝贵的芯片面积。

瑞萨电子的 PIM 技术使用标准 SRAM 宏中的 1 位读出放大器作为比较器,与可灵活控制电流的复制单元(相当于存储单元的当前生成部分)结合使用。将复制单元电流与三元单元电流进行比较有效地检测三元单元的电流输出。

零检测器还有助于降低功耗。如果 MAC 运算结果等于 0,则停止比较器的操作以节省能量。

“在 [典型] 神经网络电路中,几乎所有节点都分配为零;只有少量的神经元被激活,大约 1%。所以几乎所有的计算结果都归零,”Nose 说。“激活零检测器电路会关闭比较器并有助于降低功耗。通过将比较器 AD 转换器技术和零检测器技术相结合,可以将功耗降低一个数量级。”

工艺变化

在 SRAM 阵列中,制造工艺的变化经常导致故障。由于这些工艺变化,当将数据写入具有显着不同电气特性的单个单元时,就会出现错误。

“为了避免这个问题,我们使用了神经网络的相同特征——几乎所有节点都分配为零,”他说。“我们可以通过改组数据来避免计算错误,以便将零存储在 [不利] 受影响的单元格中。”

在三进制存储单元中,如果存储零,则位线中没有电流流动,因此求和结果不依赖于单元电流。

如何识别受到不利影响的细胞?

“我们正在开发其他一些错误单元检测方法,但在这个芯片中,我们使用了一种简单的方法,”他说。“我们测量神经网络的输出并检查结果是否正确,以识别[不存储]正确输出值的错误单元。”

测试芯片

Renesas 的 3×3 mm 测试芯片基于 12nm 工艺技术构建,由四个集群组成,每个集群可以同时运行不同的 AI 工艺。在每个集群中,神经网络权重数据存储在 PIM 块中,MAC 运算结果存储在标准 SRAM 块中。

测试芯片包含 4 Mb 的 PIM 计算内存和 1.5 MB 的 SRAM,足以在不使用外部存储器的情况下评估紧凑型 CNN。该芯片实现了8.8 TOPS/W的功率效率。

原型 AI 模块中的测试芯片的简单演示还结合了小型电池、微控制器、相机和其他外围设备,表明只需 5 mW 即可实现用于实时人员检测的推理。

审核编辑 黄昊宇

-

芯片

+关注

关注

455文章

50789浏览量

423464 -

sram

+关注

关注

6文章

767浏览量

114683 -

AI

+关注

关注

87文章

30851浏览量

269008

发布评论请先 登录

相关推荐

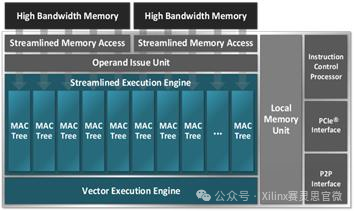

FPGA和ASIC在大模型推理加速中的应用

NVIDIA助力丽蟾科技打造AI训练与推理加速解决方案

李开复:中国擅长打造经济实惠的AI推理引擎

AMD助力HyperAccel开发全新AI推理服务器

摩尔线程携手东华软件完成AI大模型推理测试与适配

LLM大模型推理加速的关键技术

进一步解读英伟达 Blackwell 架构、NVlink及GB200 超级芯片

AI推理,和训练有什么不同?

用基于SRAM的测试芯片实现加速AI推理

用基于SRAM的测试芯片实现加速AI推理

评论