SERDES的优势

引脚数量和通道优势

SERDES最明显的优势是具备更少的引脚数量和线缆/通道数量。对于早期的SERDES,这意味着数据可以通过同轴电缆或光纤发送。

对于现代的SERDES来说,另一个优势是能够通过一对差分对信号引脚(而不是8、16、32或N个数据引脚和一个时钟引脚)发送数据。在串行传输这个方面得益于更小的数据包和更密集的pcb而节省了成本。具体取决于晶片成本、封装成本、PCB成本和PCB拥塞等因素。

距离优势

在过去的十年里,SERDES在PCB和基板上远距离传输的能力已经帮助它们应用在许多新的领域中。

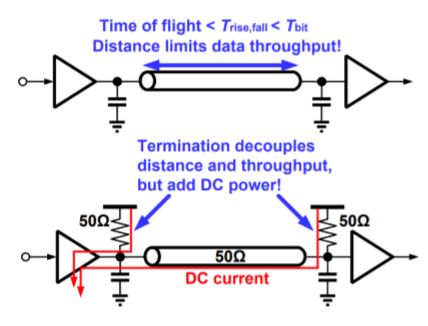

图1通过端接并行总线来极大地提高传输距离、功耗效率

从简单的微波设计中,当传输线的传输时间小于上升/下降时间时,看起来像是一个“集总元件”。对于一个GPIOs(通用输入输出)的并行接口,上升/下降时间通常在几纳秒以上。这使得非端接并行接口得以在典型PCB上以30cm的距离正常工作。端接并行总线将增加传输距离,但是,它会增加大量的功耗,并使功效急剧下降(如图1)。

SERDES接口通常通过两端(TX,RX)的受控阻抗传输线传输。这可以让数据快速的传输且不需要考虑反射损耗。当然,为了快速、串行地传输数据,需要增加很多额外的复杂设计—串行器、解串器、TXPLLs(发送)、RXCDRs(接收)、前馈均衡(FFE)、接收均衡等等。

注:

串行器的作用:在传递和保存对象时快,保证对象的完整性和可传递性。对象转换为有序字节流,以便在网络上传输或者保存在本地文件中;

解串器的作用:根据字节流中保存的对象状态及描述信息,通过解串重建对象;

总结:核心作用就是对象状态的保存和重建。

功耗优势

直到最近,SERDES相对于并行数据总线在功耗上的优势才得以显现。理想的并行总线所消耗的能量是发送(TX)和接收(RX)电容和迹线(trace)电容充放电时产生的。FR4(覆铜板)上的迹线(trace)电容在传输距离为10,20或100厘米时会变得非常大,这一点需要特别注意。

根据基本原理,我们知道LVCMOS链路的功耗是~C×V²×f。就数据而言,频率则是总比特率的二分之一乘以传输密度。传输的总数据量和功耗、线路数量无关——线路越多,每条线路传输的数据量就越少。对于1Gb/s的线路,10厘米到1米距离可能需要8-16条线路。对于10Gb/s的线路,1m的距离可能需要120条线路!这是非常不切实际的。

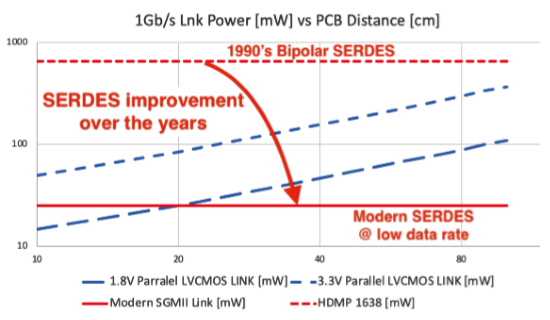

图2:不同电压下并行LVCMOS链路和1990年代及现代SERDES在功耗方面的对比

图2显示了不同电压下并行LVCMOS链路和1990年代以及现代SERDES在功耗方面的对比。可以明显的看出,现代SERDES在长距离上具有功耗上的优势,但是这个优势并不明显。

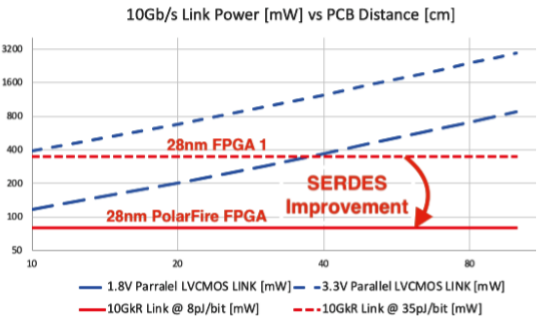

当数据速率越高时,SERDES在功耗上的优势就越明显。图3显示了在2010年代中期到后期,不同电压下并行LVCMOS链路的功耗与不同28nmSERDES功耗的对比。可以看出,现代的SERDES在几乎所有的距离上都保持着功耗上的优势。对于一个功耗经过优化后的SERDES,在所有距离上,功耗优势都是巨大的。

当然,随着工艺技术的进步,SERDES的功耗上的优势将会继续扩大。

图3:不同电压下并行LVCMOS链路的功耗与不同28nmSERDES功耗的对比

对SERDES演变的看法

我的职业生涯开始于惠普SERDESASICs的开发团队。HDMP-1638是我参与开发的首批产品之一。由于安捷伦从惠普剥离,该ASIC的logo为“安捷伦”,而非“惠普”。

由于这个芯片在当时十分具有竞争力,且销售很好,对于20到25年前的工业SERDES来说,它都是一个benchmark。该芯片设计为双极型(bipolar)工艺,它以1.25Gbps的线路速率来支持千兆以太网(802.3z)和1000Base-XGb/s的光纤以太网。

HDMP-1638的功耗约为1W,其中包括一个外部并行接口——毕竟是SERDES芯片!该芯片的功耗(不包括并行接口)估计为650mW,或大约500pJ/bit。稍后我们将继续说一说它与现代SERDES在功效(pJ/bit)方面的比较。

注:pJ/bit-发送每bit信息的能量消耗。

自2006年以来,我一直在SiliconCreations公司帮助开发高级节点的低功耗SERDES。近年来,SiliconCreations一直在开发高达32Gb/s传输速率的SERDES,并将功效降低到2.5pJ/bit。拿这些SERDES和20年前的相比:

1.速度增加了25倍

2.功效提高了200倍

工艺、电压调节以及设计方面的巨大进步促成了如此明显的性能提升。

SERDES面临的挑战

如前一节所述,SERDES在功耗、引脚数量和传输距离方面具有很大的优势。SERDES的缺点是则是其复杂性和成本。

复杂性在较低的数据传输速率上,至少需要TXPLL、RXCDR、TXdriver和RXfront。每一个都是复杂的模拟子系统。设计这些模块和整个SERDES系统需要一个熟练的模拟/混合信号设计团队来完成。这些模块(连同复杂的数字控制)包括:

TXPLL:这个模块需要用25-100MHz的参考时钟(具备1ps以下的长时抖动)产生一个数GHz级的时钟。

RXCDR:这个模块是一个复杂的控制回路,用于跟踪传入数据的平均相位,而不管链路上的任何噪声、失真或串扰。这通常是通过复杂的相位旋转器或CDR驱动的锁相环来完成的。

TXdriver:这个模块把序列化数据转化为一个典型的50Ω差分信号。

RX均衡器:此模块用连续时间均衡器和DFE(判决反馈均衡器)来均衡高速通道效应。通常需要一个自动增益(AGC)电路来促进均衡效果。RX均衡器通常以状态机逻辑或软件的形式来实现自动校准。

高速串行器和解串器逻辑:上面列出的所有模块都需要一个经验丰富的设计团队花费相当多的设计时间(需多人开发数年)。随着数据速率(Gb/s)的提高和对效率(pJ/bit)的要求的增加,SERDES的复杂性和成本也随之增加。对着可靠性需求的增加,必须进行越来越多的老化和电迁移模拟和分析,这又进一步增加了成本。

本文聚焦于PAM2/NRZSERDES,而PAM4提供了每个引脚具有更高带宽的替代方案,但通常的代价是在PAM2/NRZ系统上进一步增加芯片面积、功耗和复杂性。

幸运的是,SERDES已经作为IP模块被广泛的使用。因此,做系统的公司可以从主要的IP提供商那获取设计许可证(license)。通过这种方式,设计复杂度可由专门的设计团队来分摊,研发成本也可以在多个芯片、项目甚至行业之间共享,从而帮助降低成本。

成本

SERDES的主要费用来自设计(许多设计者花费了许多年)和验证,除此之外,芯片面积和PCB大小也是十分重要的影响因素。

PMA层的SERDES验证通常由一个设计子团队处理。在系统层,验证可能相当复杂,特别是对于像PCIe这样的标准。

注:SerDes主要由物理介质相关(PMD:PMD-PhysicalMediaDependent)子层、物理媒介附加(PMA:physicalmediumattachment)子层和物理编码子层(PCS:PhysicalCodingSublayer )所组成。PMD是负责串行信号传输的电气块,PMA负责串行化/解串化,PCS负责数据流的编码/解码。在PCS的上面是上层功能。针对FPGA的SERDES,PCS提供了ASIC块和FPGA之间的接口边界。

对于复杂的串行标准和测试程序(比如SystemVerilog),需要从物理层(包括PMA和PCS)、数据链路层、业务层和设备层去验证系统。涵盖这些层的验证通常需要检查协议、模式、错误注入和恢复等方面。验证通常也需要很多个月的时间,并且经常涉及到第三方来验证IP。

在晶片价格上,SERDES和并行接口不好比较。根据工艺节点的不同,一个SERDES每条线路大约占用0.15到0.5mm²的空间。一个并行接口可以比这个小得多,但是需要更多的I/O口。因此,晶片成本取决于芯片对I/O和对引脚的需求如何平衡。

在封装和PCB方面,SERDES允许减少引脚和迹线总数。因此,这样的封装和PCB设计的尺寸将更小,成本更低。但是,由于高速受控阻抗的复杂性,SERDES的封装和PCB设计将十分困难,因此,在这方面比使用相对速度较低的并行接口更昂贵。

总结

在过去的20年里,SERDES已经从光纤和网络电路转变为我们身边常见的电路,从手机到笔记本电脑,从电视到数据中心等等。

PCIe大约是在2002年引入的,那时的线速率是2.5Gb/s。从那时起,设计的改进和CMOS工艺的提高使得线路速率提高了约20倍(从2.5Gb/s到50Gb/s),功率效率(pJ/bit)提高了约200倍。

SERDES(Serializer-Deserializer)是串行器和解串器的简称。串行器(Serializer)也称为SerDes发送端(TX),(deserializer)也称为接收端(RX)。

PLL模块、TX发送模块、RX接收模块。

串行器把并行信号转化为串行信号,解串器把串行信号转化为并行信号。

-

数据

+关注

关注

8文章

7222浏览量

90135 -

引脚

+关注

关注

16文章

1291浏览量

51300 -

SerDes

+关注

关注

6文章

203浏览量

35228

原文标题:SerDes的好处在哪里(下)

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

SerDes技术优势明显,解决车内高速传输难题

ASP4644在FPGA SERDES供电中的应用

请问6678中的srio的serdes和以太网的serdes是共用还是各自有自己的serdes?

SERDES接口电路设计

SERDES传输和引脚关联

请问单个SERDES Quad可以同时运行4个接收通道吗?

SerDes是怎么工作的

基于FPGA芯片的SERDES接口电路设计

如何使用FPGA实现SERDES协议

SerDes收发器内部的电路物理层结构设计分析

SerDes是怎么设计的?(一)

SERDES的引脚数量和通道优势

SERDES的引脚数量和通道优势

评论