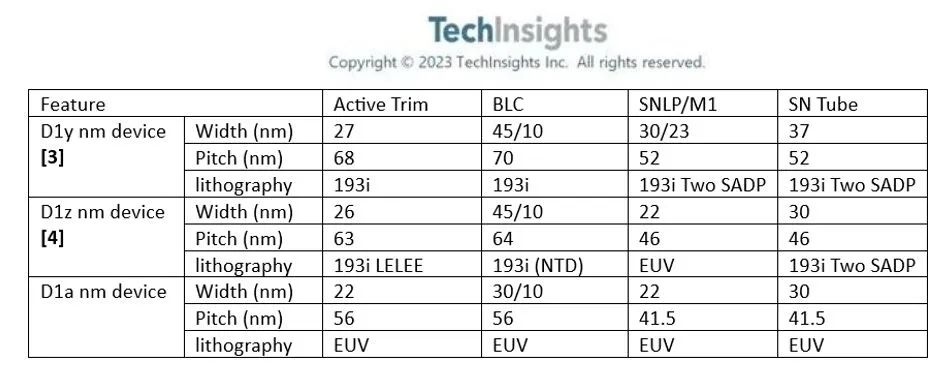

对于如今的半导体产业而言,EUV光刻机是打造下一代逻辑和DRAM工艺技术的关键所在,为了在未来的工艺军备竞赛中保持优势,台积电、三星和英特尔等厂商纷纷花重金购置EUV光刻机。

然而,当这些来自荷兰造价上亿的庞大机器到位并组装好后,并不意味着EUV光刻机的生产工作完全准备就绪。随着先进工艺晶圆制造中图案化策略和分辨率重视程度的攀升,为了满足这些需求,与EUV光刻技术相关的材料同样需要纳入考量,尤其是光刻胶和防护膜。

EUV光刻胶

大家最为熟知的一大光刻材料自然就是光刻胶了,光刻胶为晶圆生产带来的不仅是高分辨率,同样也是控制随机缺陷的关键。极紫光透过光掩膜透明的部分在光刻胶上曝光,接着去掉曝光的光刻胶,蚀刻曝光的材料,最终去掉所有光刻胶留下光刻后的图案,而我们常说的分辨率也就是光刻胶所能产生的最小尺寸了。

与此同时,在ASML看来,下一代高NA EUV光刻机为光刻胶再度带来了挑战,更少的随机效应、更高的分辨率和更薄的厚度。首先传统的正胶和负胶肯定是没法用了,DUV光刻机上常用的化学放大光刻胶(CAR)也开始在5nm之后的分辨率和敏感度上出现瓶颈,所以光刻胶上的创新已经成了2023年/2024年后高NA EUV光刻机的必要条件。

2020年,泛林集团宣布在ASML和imec的战略合作下,已经研究出了用于EUV光刻机图案化的干式光刻胶技术,这种干式光刻胶技术可以显著提高EUV的敏感度和分辨率优势,而且其生产工艺耗能更少,所用的原材料也比传统光刻胶工艺少上5到10倍,从而改善了每次处理EUV晶圆所需的总成本。近日,泛林集团宣布将与三菱化学旗下Gelest以及Entegris这两大材料公司合作,共同推进EUV干式光刻胶的量产。

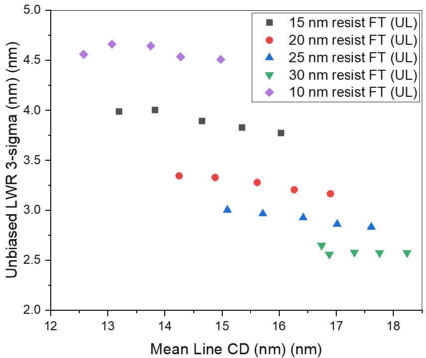

线宽粗糙度增加下厚度减少的金属氧化物光刻胶 / imec

而imec和JSR这样的厂商则选择了在金属氧化物光刻胶(MOR)上下注,在他们的研究评估中,MOR光刻胶拥有更好的图案转移能力,能够实现更高的分辨率,并把光刻胶做得更薄。不过虽然这类光刻胶已经被一票光刻胶厂商、晶圆厂看好,但目前在量产上还是存在一些问题的,比如在制备过程中需要将金属污染等级降低至传统行业等级之下。

EUV防护膜

对于利用EUV光刻机制造芯片来说,其实EUV防护膜的使用并不是必要的,这个材料的存在更多是为了保证光掩膜的清洁。尽管如今庞大的EUV都被放置在遵循严格标准的无尘洁净室里,基本杜绝了外部颗粒的污染,然而在EUV光刻机的曝光过程中,要想做到零颗粒是不可能的,依照ASML的说法,约摸1万次曝光就会有一个杂质颗粒的出现。

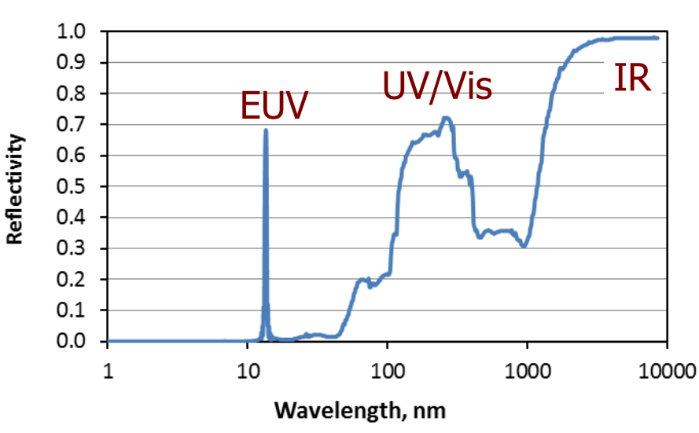

部分厂商对此或许并不在意,比如三星就一直在推迟防护膜的使用,以至于最后干脆自己投资并开发EUV防护膜。因为这些杂质的存在或许会对良率产生一定影响,但如果为光掩膜贴上透射率不高的防护膜,那么就会吸收部分13.5nm波长的极紫光,届时影响了的就是产量了。EUV光刻机开始普及使用的那段时期,恰好遇上了全球半导体产能短缺,自然保产量才是各大晶圆厂的首要目标。

不过如今产能情况逐渐转好,EUV防护膜的开发与普及也是时候提上议程了。要想不对EUV光刻机的产能输出造成太大的影响,晶圆厂都希望防护膜的透射率能做到90%以上。从去年开始,已经有一批企业打造出了90%透射率以上的防护膜了。比如Canatu打造的碳纳米管EUV防护膜,就可以做到97%的透射率。

既然如此,这些晶圆厂已经早已经跟进了才对,为何防护膜至今仍然没有受到台积电、三星等厂商的青睐,难不成他们在等更低成本的方案不成?其实不然,光刻过程中还有一个问题也在影响EUV防护膜的普及,那就是材料寿命。

虽然这些防护膜已经实现了90%的透射率,但随着新一代EUV光刻机的光源功率已经超过了250W,未来的高NA EUV光刻机的功率还将进一步提升,光源带来的热应力会破坏这些防护膜,所以在选择防护膜的同时还得考虑耐热性,否则不会有晶圆厂想要频繁替换防护膜的。所以大部分防护膜厂商即便实现了90%以上的透射率,也还在推进具有可观寿命防护膜的大规模量产,至于这些EUV防护膜的广泛使用,还需要等待材料和工艺上后续创新。

审核编辑 :李倩

-

芯片

+关注

关注

453文章

50360浏览量

421638 -

半导体

+关注

关注

334文章

26988浏览量

216002 -

光刻机

+关注

关注

31文章

1144浏览量

47232

原文标题:EUV光刻机就位后仍需解决的材料问题

文章出处:【微信号:elecfans,微信公众号:电子发烧友网】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

美投资8.25亿美元建设NSTC关键设施,重点发展EUV光刻技术

日本与英特尔合建半导体研发中心,将配备EUV光刻机

日本大学研发出新极紫外(EUV)光刻技术

日企大力投资光刻胶等关键EUV材料

阿斯麦和IMEC联合光刻实验室启用

Rapidus对首代工艺中0.33NA EUV解决方案表示满意,未采用高NA EUV光刻机

ASML考虑推出通用EUV光刻平台

台积电A16制程采用EUV光刻机,2026年下半年量产

英特尔率先推出业界高数值孔径 EUV 光刻系统

英特尔突破技术壁垒:首台商用High NA EUV光刻机成功组装

ASML 首台新款 EUV 光刻机 Twinscan NXE:3800E 完成安装

EUV光刻技术相关的材料

EUV光刻技术相关的材料

评论