导读:所有的产品离不开电源,从芯片级到封装级再到板级,从晶体管到键合线再到铜箔,电源的协同设计可以贯穿整个产品级。电源如此重要,却充满着设计挑战,从耦合到串扰再到噪声,如何保证电源的输送是电源工程师必须要考虑和解决的。

一、阻抗的管控说到底就是路径管控

电源输送可以理解为电源分配网络(PDN),从源端稳压模块(VRM)到芯片,芯片分配电压,再到电源路径(单层直达或过孔转换的几个层面),最终流向使用芯片或终端设备。

电源路径与信号路径是有区别的,电源分配网络中一个电源路径可以在一个节点分成多个路径,或者说转换成多个电源,终端挂多个元器件,可以理解为一对多,而信号路径只能一对一。

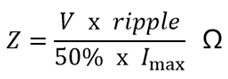

既然电源分配网络是为终端设备提供所需电源,那就是有要求,就需要对电源分配网络管控。当交流电流通过电源路径时,电源分配网络上也将产生电压降,这个压降会随着频率发生变化。电源路径的不同(层数&Shape宽度等),造成的压降变化是不同的,输出稳定电压到终端的难度很大,我们所要做的只是保证电压的变化在一定的范围之内,也就是所谓的噪声容差,将其转换为目标阻抗:

一般默认,电流为最大电流值的50%。PCB板级PDN设计,最先需要确定的便是电源分配网络的目标阻抗。

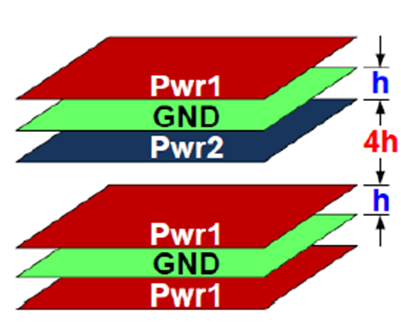

说到目标阻抗管控,在实际工作中,铺电源网络,即电源从源端到终端的路径,路径上电压是有变化的,那么电源分配网络的电流就会有波动,目标阻抗的管控说到底就是路径管控。如何管控?两个方向:电源和地平面的介质和短而宽的连接。

二、电源分配网络(PDN)分析方向

电源分配网络(PDN)有两种分析方向:单点式和分布式。

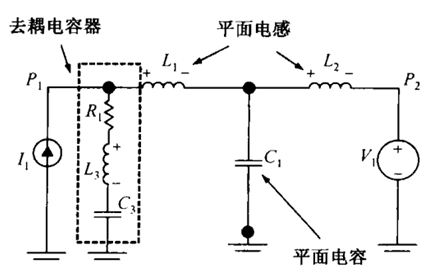

单点式分析假设平面电压为常量,终端的去耦电容为并联,这里主要考虑的是谐振与反谐振,低频情况下,可以忽略平面电感的影响,但是还是要考虑平面电感和平面间距的影响。

平面电感可以看成为分布式电压,有平面有变化的电压,会产生驻波(全波即为360°相移,半波则为180°反相),就会在一些频率处产生谐振。

任何谐振电磁结构中存储的能量(电&磁)在一段时间内都会在电场和磁场之间周期性振荡,这说明能量在交替变换,在最大值和零值之间。

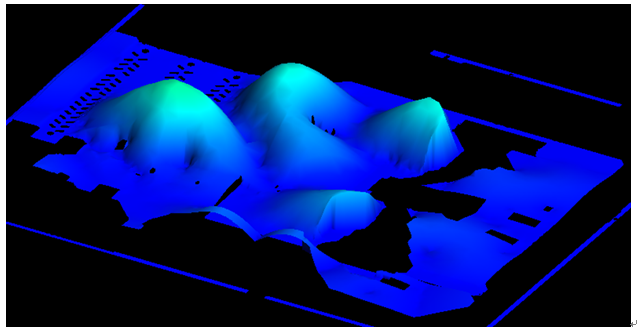

以版图设计的平面,可以理解为矩形谐振腔为例,能量到达平面边缘,会发生反射。反射回来的能量会和入射能量进行交换,相位相同形成最大值,即波峰,相位相反形成形成零值,即波谷。有些达到平面边缘的能量没有反射回来,就会形成噪声,产生EMI问题。

在平面谐振的频率点上,去耦电容的位置就很关键,需要它们放在电压的最大值处以便更好地减少平面间的反弹。

三、消费类产品电源设计

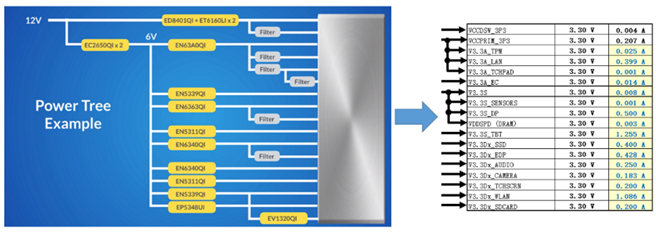

下图为消费类产品设计电源部分的实际情况图:

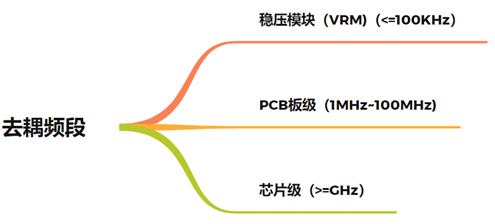

板级电源分配网络设计的频率范围约从 1MHz 到 100 MHz,其实根本到不了100M,这个频率范围电路板平面和多层陶瓷贴片电容器( MLCC) 发挥作用的频率范围 。这也是PCB板级电源仿真时需要重点关注的。

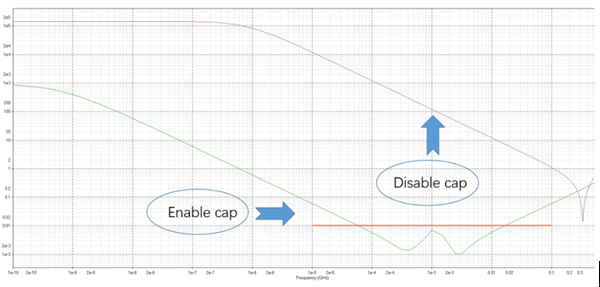

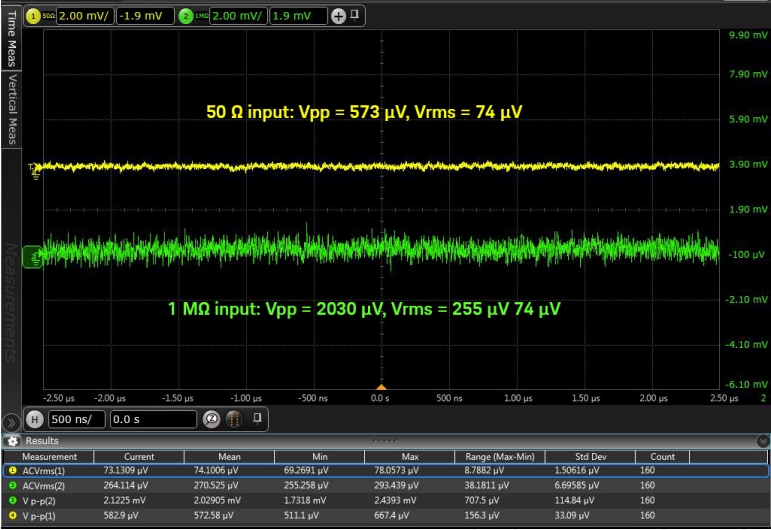

PDN设计一般就是指在PCB板级上给电源提供低阻抗路径。这里面还有电容摆放位置、电容不同容值&个数、反谐振等方面,到仿真这一边,就是交流部分:PDN阻抗提取和直流部分:IR Drop压降。下图说明,是否使能电容对PDN阻抗的影响很大。

四、电源路径规划怎么做?

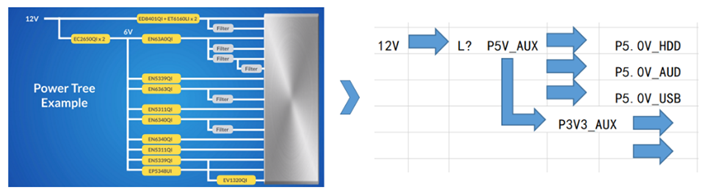

先期评估,确认各个电所需层面和路径的时候,我们会预先根据相关规范或标准,制定一个电源树(Power tree)。个人觉得电源树的概念提的特别好。一个主干道有很多分支,分支上再有分叉,一直到末端。

电源分配网络可以有很多分支,也就是说路径上可以挂很多设备,比如5V电源下挂HDD,USB设备等。比如12 V的电转出5V,5V总电分出分支,给到各种设备。5V经过LDO转换电路出3.3V电,,3.3V总电分出分支,再往下继续……

同时列出各个分支所需电流的多少,为后面路径规划(所需电源Shape大小给出标准),同时给出对应的层面及评估。

在做电源路径规划,建议先做电源树Power Tree,对所做设计的终端设备所需电压路径及所需电流大小一一评估,产品的不同,有的产品可能会使用几十种电压值。检查的时候,建议从终端往前反推,这样保证没有遗漏。

不管什么产品,电源是其最重要的部分。特别是消费类产品,在成本的管控之下,会通过各种手段降低成本,最直观的减小MLCC的使用种类和数量,电源的优化是一项很重要的工作,通过优化,来降低产品成本,这也是电源完整性的作用和职责所在。

审核编辑 :李倩

-

芯片

+关注

关注

456文章

50967浏览量

424923 -

阻抗

+关注

关注

17文章

958浏览量

46064 -

电源完整性

+关注

关注

9文章

210浏览量

20745

原文标题:电源完整性知多少?这四个要点请收藏(附电磁仿真学习包)

文章出处:【微信号:sim_ol,微信公众号:模拟在线】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

用CPU的引脚控制TAS5711的PDN引脚的电平高低,拉低PDN引脚后TAS5711输出没声的原因?

功率合成和分配网络有何特点

PDN 元件对阻抗的影响

搞定电源完整性,不如先研究PDN!

24芯M16插座电源分配功能怎样

如何使用S2SPICE来优化PDN的电感

PCB 中的电源平面谐振分析

电源分配网络(PDN)与目标阻抗的计算方法

电源分配网络(PDN)分析方向

电源分配网络(PDN)分析方向

评论