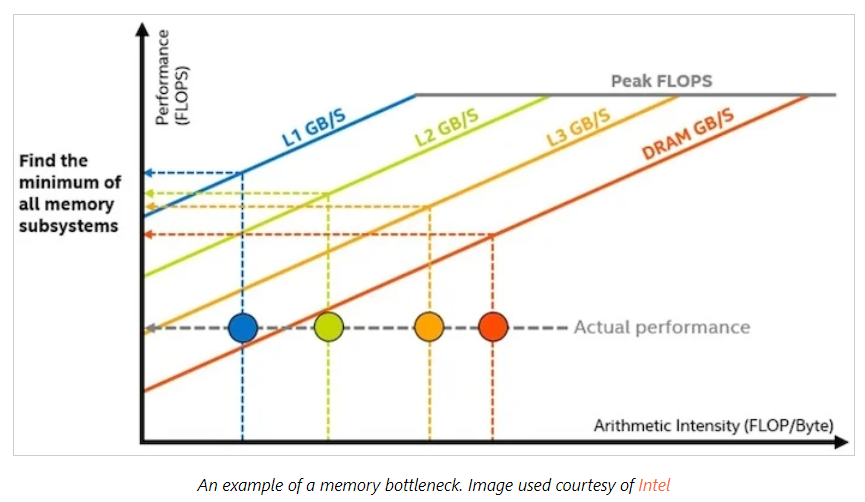

计算历史上的一个基本挑战是计算速度和内存访问之间的不匹配。在计算机架构层面,这一挑战导致了更快的内存和缓存等概念的出现,以帮助缓解这些挑战。

物联网(IoT)设备面临的挑战是显而易见的,时钟频率和非易失性内存访问读取频率之间的不匹配,导致无线(over-the-air, 简称OTA)更新和通用计算等功能出现瓶颈。

为了解决这个问题,各个公司正在寻找新的非易失性存储器作为解决方案,其中STT-MRAM是一个很有竞争力的备选方案。

最近,Renesas宣布了一项新的电路技术,在22纳米工艺上实现了高速STT-MRAM。本文将介绍MRAM、STT-MRAM和Renesas的最新公告。

MRAM基本知识

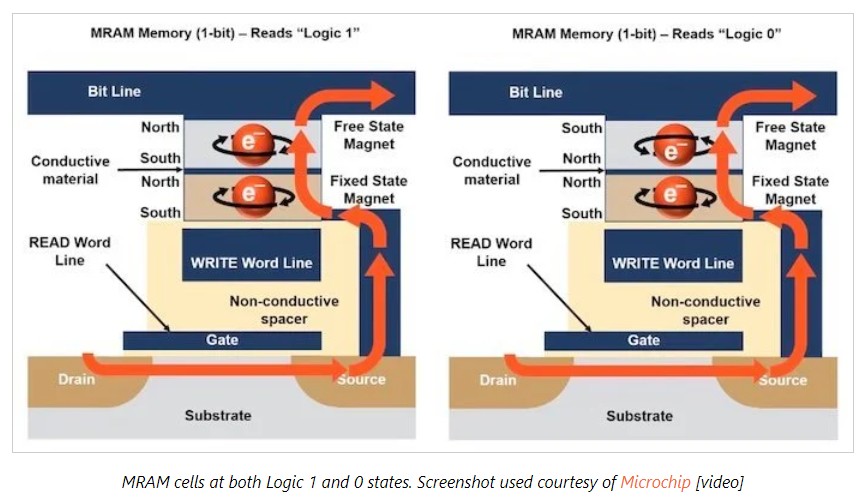

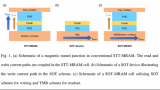

MRAM可能是非易失性存储技术的下一个大事件。该技术利用了磁性材料的相对极性和电阻之间的关系。本质上,当两个磁铁靠近时,它们的电阻会发生变化,这取决于它们的磁极相对于另一个磁极的位置。

例如,一个磁体的北极与另一个磁体的南极对齐,接合点的电阻就会很低,反之亦然。

MRAM利用这种由磁体极性控制的电阻变化,作为一种状态,设备可以使用它在内存中存储bit位。电流可以在给定的方向上影响每个磁体的极性,然后微分感测放大器就可以读出结果状态。

与其他形式的非易失性内存相比,这种类型的存储具有几个关键的优势,例如高存储密度和较低的读/写电流。

STT-MRAM是什么?

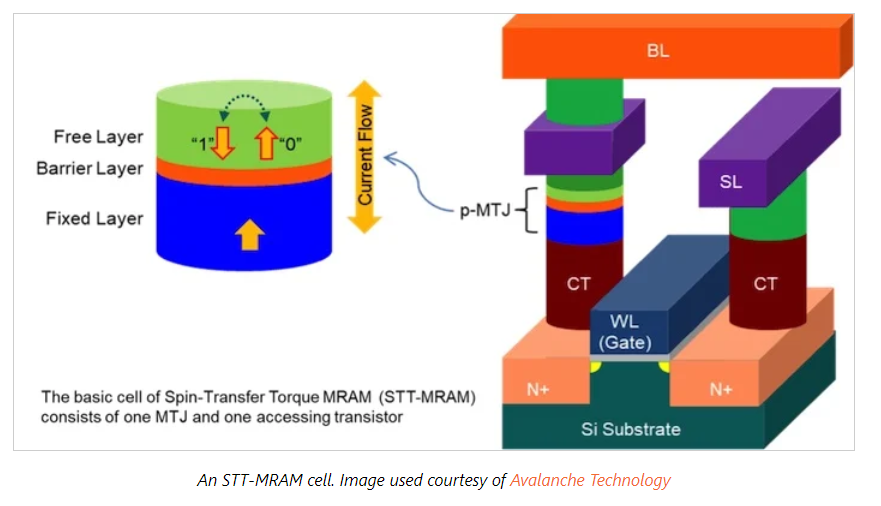

在MRAM世界中,存在着许多不同的技术。其中,STT-MRAM技术是最有前途的技术之一。

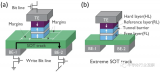

STT-MRAM是MRAM的一种变体,其附近电子的自旋会影响MTJ(magnetic tunnel junction)的极性。在这种形式的MRAM中,电子自旋是由通过一层薄磁层的极化电流控制的,将角动量转移到这一层,因此改变了电子自旋。

与其他形式的MRAM相比,STT-MRAM具有更低的功耗和进一步扩展的能力。许多人认为,STT-MRAM具有与DRAM和SRAM相当的性能,但在10纳米以下进程也可以实现,可以挑战闪存的成本,因此有可能成为领先的存储技术。

22纳米下实现更快的读/写操作

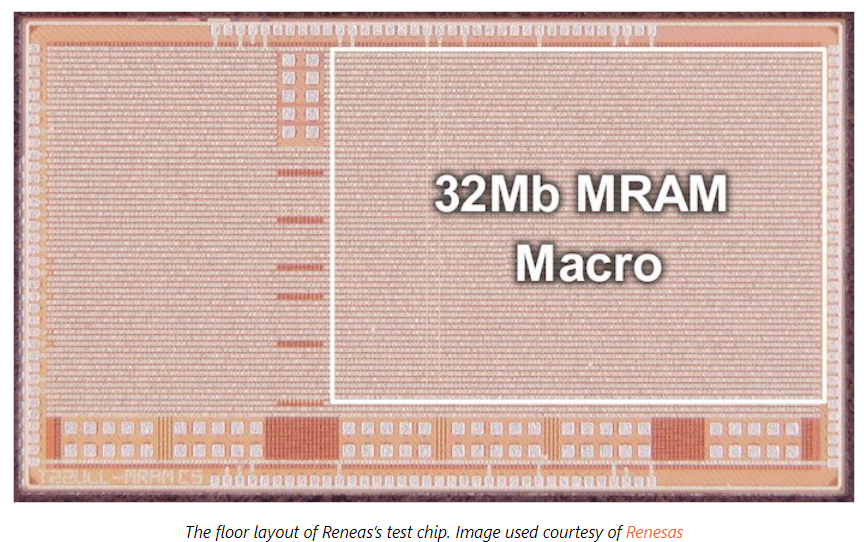

最近,Renesas宣布开发出了一种新的电路技术,可以在22nm节点上更快地进行STT-MRAM的读/写操作。

该技术的主要创新是一种解决MRAM的低不同感知电压导致读写速度慢和可靠性差(特别是在高温下)的方法。新技术利用电容耦合来提高差分放大器输入端的电压,这样STT-MRAM的状态可以在电流很低的情况下更快更可靠地读取。

使用这种技术,Renesas声称在写操作的模式转换时间上减少了30%,这提高了整体写操作的速度。

工程师在22nm制程的测试芯片上验证了这一点,芯片上包括一个32 Mbit嵌入式MRAM存储单元阵列。据报道,该测试芯片在150°C的高温下随机读访问时间为5.9 ns,写吞吐率达到8.8 MB/s。

审核编辑 :李倩

-

物联网

+关注

关注

2909文章

44700浏览量

373933 -

纳米

+关注

关注

2文章

697浏览量

37017 -

MRAM

+关注

关注

1文章

236浏览量

31735

原文标题:瑞萨在22纳米工艺上实现高速STT-MRAM

文章出处:【微信号:SSDFans,微信公众号:SSDFans】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

探索存内计算—基于 SRAM 的存内计算与基于 MRAM 的存算一体的探究

MCU制程工艺迈进28nm时代,汽车行业的创新之路

MRAM HS4MANSQ1A-DS1在汽车电子中的应用

瑞萨电子宣布已开发具有快速读写操作的测试芯片MRAM

MRAM特性优势和存储原理

台积电开发出SOT-MRAM阵列芯片,功耗极低

台积电引领新兴存储技术潮流,功耗仅为同类技术的1%

台积电开发出SOT-MRAM阵列芯片

杀手锏!台积电开发SOT-MRAM阵列芯片

台积电和ITRI成功研发SOT-MRAM,功耗仅为STT-MRAM的百分之一

MRAM(磁性只读存储器)和FRAM(铁电RAM)有何区别

深入探索MRAM的原理与技术

创纪录的SOT-MRAM有望成为替代SRAM的候选者

MRAM、STT-MRAM和Renesas的最新公告

MRAM、STT-MRAM和Renesas的最新公告

评论