2014 年,赛普拉斯推出了 HyperBus 接口,该接口利用并行和串行接口存储器的传统特性,提高了系统性能,简化了设计,并显着降低了成本。在支持 HyperBus 的解决方案中,HyperRAM 是一种新颖的技术解决方案,能够实现高达 333 MB/s 的吞吐量,在 HyperRAM 2.0 中增加到 400 MB/s。HyperRAM 2.0 是一种高速、低引脚数自刷新动态 RAM (DRAM),专为需要扩展内存的高性能嵌入式系统而设计,例如汽车、工业、消费和物联网应用。HyperRAM 2.0 提供 HyperBus 和 Octal SPI 接口,并在 DDR 模式下提供高达 400 MBps 的读/写带宽。

超内存

通过与 Cypress 的合作,华邦电子已经推出了 32Mb 到 512Mb 密度的产品。目前,车规级24BGA(6×8 mm 2)、面向消费级可穿戴市场的WLCSP(Wafer Level Chip Scale Package)、KGD(Known Good Die)等产品均已上市。

除了 Cypress 之外,其他相关的领先 MCU 制造商,如 NXP、Renesas、ST 和 TI 都已经开发了支持 HyperBus 接口的微控制器,并且他们的支持也有望在未来得到支持。同时,Cadence、Synopsys 和 Mobiveil 等领先的芯片 IP 供应商也开始提供 HyperBus 内存控制 IP,从而加快了包含该内存解决方案的产品的上市时间。

HyperRAM 可以显着提高终端设备的性能,其主要优势如下:

低功耗:此特性是通过混合睡眠模式 (HSM) 实现的,该模式仅消耗 45µW@1.8V 和 55µW@3V(与相同容量的待机模式 SDRAM 的 2000µW@3.3V 相比)

减少占用空间:低引脚数可以节省 PCB 上的宝贵空间

易于控制:使用较少的活动引脚,设计更简单,而不会影响整体系统性能。

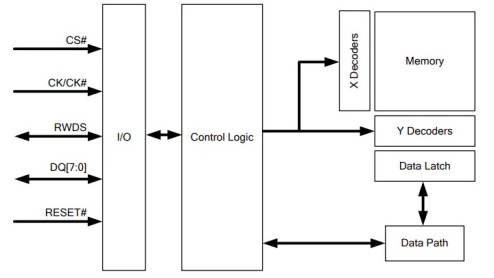

除了更高的功耗外,低功耗 SDRAM 的外形尺寸比 HyperRAM 更大,这并不使其成为应尽可能减少占用空间和 PCB 面积的理想解决方案。如图 1 所示,HyperRAM 接口仅需要 13 个引脚(DQ[7:0]、RWDS、CS#、RESET#、CK 和 CK#),大大简化了 PCB 设计和封装尺寸。反之亦然,传统的 SDRAM 解决方案在 54BGA 封装中需要 38 个引脚和 8×8 mm 2的面积,而 LP SDRAM 解决方案在 54BGA 封装中需要 41 个引脚和 9×8 mm 2的面积。因此,在产品的设计阶段,更多引脚可用于实现附加功能,从而使解决方案更具成本效益。

图 1:华邦 HyperRAM 框图

HyperRAM 的另一个相关特性是它是一个自刷新 RAM,这意味着它可以在完成读/写操作后自动返回待机模式。这可以减少系统设计和固件开发的工作量。

关于可以从该解决方案中受益的用例和行业,它们包括所有需要低功耗和高 MCU 计算能力的应用,例如汽车、工业 4.0、智能家居、可穿戴设备和物联网设备。此外,对于智能扬声器和智能电表等电池供电设备,低功耗对于实现更长的电池寿命至关重要。

华邦 HyperRAM 是嵌入式 AI 和图像处理分类的理想解决方案,其中设备应尽可能小,同时提供足够的内存空间来支持计算密集型算法,例如人脸识别、物体检测、实时图像识别和边缘计算。

“HyperRAM实际应用案例主要有两种:一种是精准图像识别,一种是语音识别,两者都支持语音或图像的AI模型”,华邦半导体DRAM市场经理Jacky Tseng在接受采访时表示。与 EEWeb。

SpiStack

SpiStack 是华邦开发的一种内存解决方案,它是通过将一个 NOR 裸片和一个 NAND 裸片堆叠到同一个封装中而形成的,例如一个 64Mb 串行 NOR 和一个 1Gb QspiNAND 裸片。该解决方案使设计人员能够灵活地将代码存储在 NOR 裸片中,并将数据存储在 NAND 裸片中。

通过堆叠同构或异构闪存模块,SpiStack 提供了具有不同密度的各种存储器,用于代码和数据存储,同时为设计人员提供最大的存储灵活性以满足其设计要求。SpiStack 存储器只需要 8 个信号管脚,而与堆叠裸片的数量无关。可以通过简单的软件芯片选择命令切换有源芯片,提供工厂分配的芯片 ID 号。该器件的时钟频率可高达 104MHz,对应于 Quad-SPI 下的 416MHz 时钟速率。此外,SpiStack (NOR+NAND) 支持并发操作,这意味着其中一个裸片可以被编程或擦除,而另一个裸片可以同时编程/擦除/读取,反之亦然。例如,应用程序可以使用 NOR 裸片(SpiFlash,它提供更好的耐用性和保持力,和快速的随机访问时间)用于存储启动代码和应用程序代码,而多个大型数据(例如嵌入式 AI 和相机图像的学习数据)可以存储在 NAND 芯片(QspiNAND)上。多个 SpiFlash 裸片,每个裸片的密度范围从 16Mb 到 2Gb,可以与 NOR 和 NAND 裸片的任意组合堆叠。

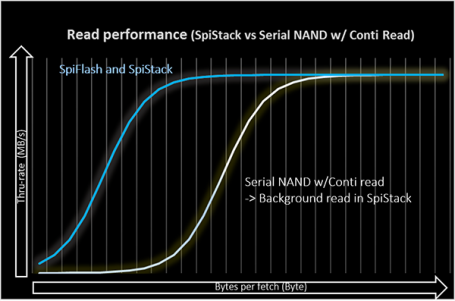

如图 2 所示,SpiStack 提供比连续读取的串行 NAND 更好的读取性能。这是因为 SpiStack 支持并发操作:在一个芯片上执行读取操作时,可以在另一个芯片上执行写入/擦除操作,而不会中断数据更新的代码执行。

图 2:SpiStack 与串行 NAND(续)。读取性能

采用 SpiStack 解决方案带来的主要好处主要有以下三个:

PCB 占用空间小:这是多个应用的强制性要求,包括物联网、可穿戴设备、消费类和医疗设备

成本效益:SpiStack 解决方案允许减少组件数量和引脚数量,简化 PCB 布局和布线

高灵活性:NOR 和 NAND die 的尺寸可以组合以满足特定的应用需求。SpiFlash NOR 闪存提供 16Mb、32Mb、64Mb、128Mb 和 256Mb 大小,而 QspiNAND 提供 512Mb、1Gb 和 2Gb 大小。

“我们解决方案的第一个好处是它可以提供更小的外形尺寸,这对于物联网等应用至关重要。第二个是成本,可以通过将两个内存芯片放在同一个芯片组中来降低成本。第三个好处是客户可以选择任何可用密度的 NOR 和 NAND 裸片”,华邦闪存营销经理 Wilson Huang 说。

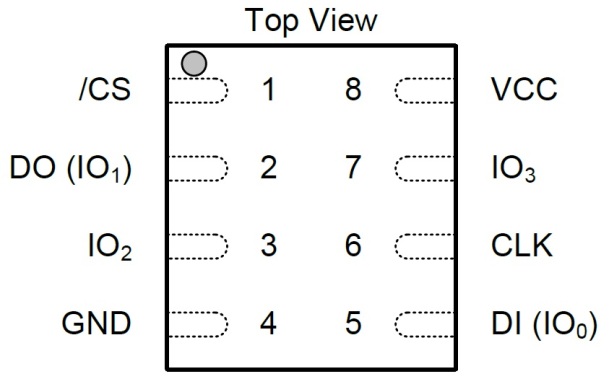

此外,通过将两个芯片集成在一个封装中可以降低制造成本,并且通过使用标准封装,即 8 焊盘 WSON 8mmx6mm 封装来保持硬件兼容性(见图 3)。

图 3:SpiStack WSON 包

“我们提供高质量的产品,因为我们只使用成熟可靠的技术(46nm NAND 和 58nm NOR)。因此,质量非常好,我们的客户不需要担心质量”,华邦的演讲者总结道。

审核编辑 黄昊宇

-

嵌入式

+关注

关注

5082文章

19126浏览量

305173 -

NAND

+关注

关注

16文章

1682浏览量

136158 -

内存

+关注

关注

8文章

3025浏览量

74045 -

HyperRAM™

+关注

关注

0文章

4浏览量

6029

发布评论请先 登录

相关推荐

嵌入式系统中的低功耗设计

基于嵌入式DSP系统的低功耗优化设计

通用AC输入70W紧凑型音频电源解决方案

嵌入式AI解决方案中内存驱动的设计介绍

嵌入式Linux的低功耗策略

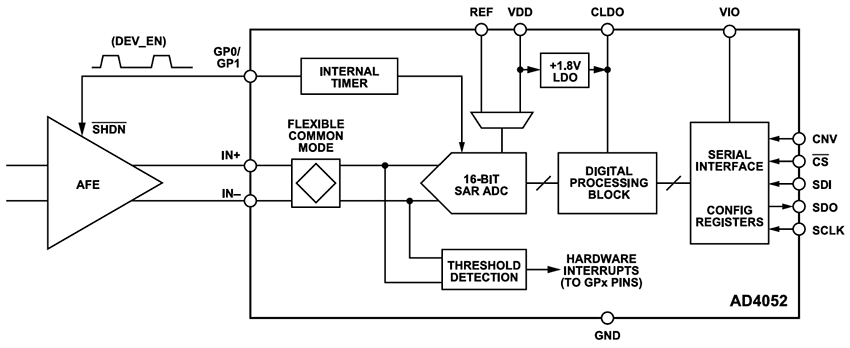

AD4052紧凑型低功耗Easy Drive SAR ADC

Neousys宸曜发布Alder Lake N紧凑型可扩展嵌入式计算平台

低功耗和紧凑型解决方案满足嵌入式系统内存要求

低功耗和紧凑型解决方案满足嵌入式系统内存要求

评论