虽然满足所有功能规范的工作设备是芯片设计项目组的首要目标,但许多设计人员醒来时满头大汗,担心芯片到货时会死机。无论使用多少覆盖率或使用多少验证工具,一个或多个错误都可能漏网。

这种高压、苛刻的工程环境需要三个独立的基于技术的功能级验证工具,以保证芯片功能无缺陷且高度可靠。验证和测试覆盖率的重叠似乎过多。许多睡眠不足的设计师认为额外的努力是值得的。

三个功能级验证步骤——功能验证、功能测试和内置自测 (BIST)——每一个都提供了对芯片设计的信心。将它们结合起来可以使芯片按照预期的功能规格工作的信心增加三倍。

功能验证是最耗费资源的步骤,因为它使用了大量可用的 EDA 工具和大量预算用于验证的时间。功能验证必须包括功能覆盖和代码覆盖。两者处理验证问题的方式不同,对于确保全面验证是必要的。

功能覆盖回答了这个问题:设计的功能行为是否符合芯片应该做的规范?有必要根据规范测试设备的行为。还不够,因为预期的功能行为几乎不能说明遇到意外状态或输入时会发生什么。

这是代码覆盖关注设计结构(代码)而不是设计规范的地方,并且可以发现功能规范中未考虑的行为。例如,可能存在在正常操作中从未预期存在的状态或输入。如果确实发生了这种意想不到的状态或输入,会发生什么?芯片如何响应?芯片可能会表现出从未预料到的行为。

通过相互补充,功能覆盖率和代码覆盖率量化了功能验证,并有助于将设计带到下一个综合、流片和最终硅片的连续步骤。实现功能和代码覆盖闭合的功能验证会清除设计的大部分或所有功能错误。当然,最终目标不是设计,而是基于设计制造的芯片。

芯片制造完成后,功能测试和 BIST 用于清除由于制造缺陷或制造过程中其他问题引起的任何错误。根据每个测试设计实施的内容,BIST 计划确定测试与执行功能测试的任何重叠,以确保所有制造的晶体管和导线无缺陷。包括 BIST 在内的深思熟虑的测试策略可以减少测试仪的时间,降低制造测试的时间和成本,并测试使用外部测试方法难以设置的芯片关键内部区域。BIST 的第二个主要优点是它可以在设备的生命周期内随时部署使用,这是某些应用程序的必要策略。

使用嵌入式 FPGA 可以简化功能设备测试,因为 FPGA 是一个预先验证的组件,可以保证按照编程的方式运行,从而最大限度地减少测试。虽然 FPGA 中的 BIST 实施会带来面积和性能开销,但使用它具有很大的好处,包括更好的测试以及一旦将设备安装到系统中就可以对其进行测试。

需要一种将功能设计验证与综合功能测试策略相结合的包容性验证策略,以降低设备到达时死机的可能性。

-

芯片设计

+关注

关注

15文章

1031浏览量

55066 -

eda

+关注

关注

71文章

2792浏览量

174073 -

代码

+关注

关注

30文章

4841浏览量

69208

发布评论请先 登录

相关推荐

芯片设计复杂度剧增,紫光芯片云 3.0 助力企业搭建专业设计环境

英诺达发布全新静态验证产品,提升芯片设计效率

复杂环境下多无人智能车辆协同调控

芯启源助力复杂数字芯片设计与验证

复杂电磁环境模拟系统设计方案

芯片测试和芯片验证的区别

工业级路由器:让你轻松应对复杂网络环境!

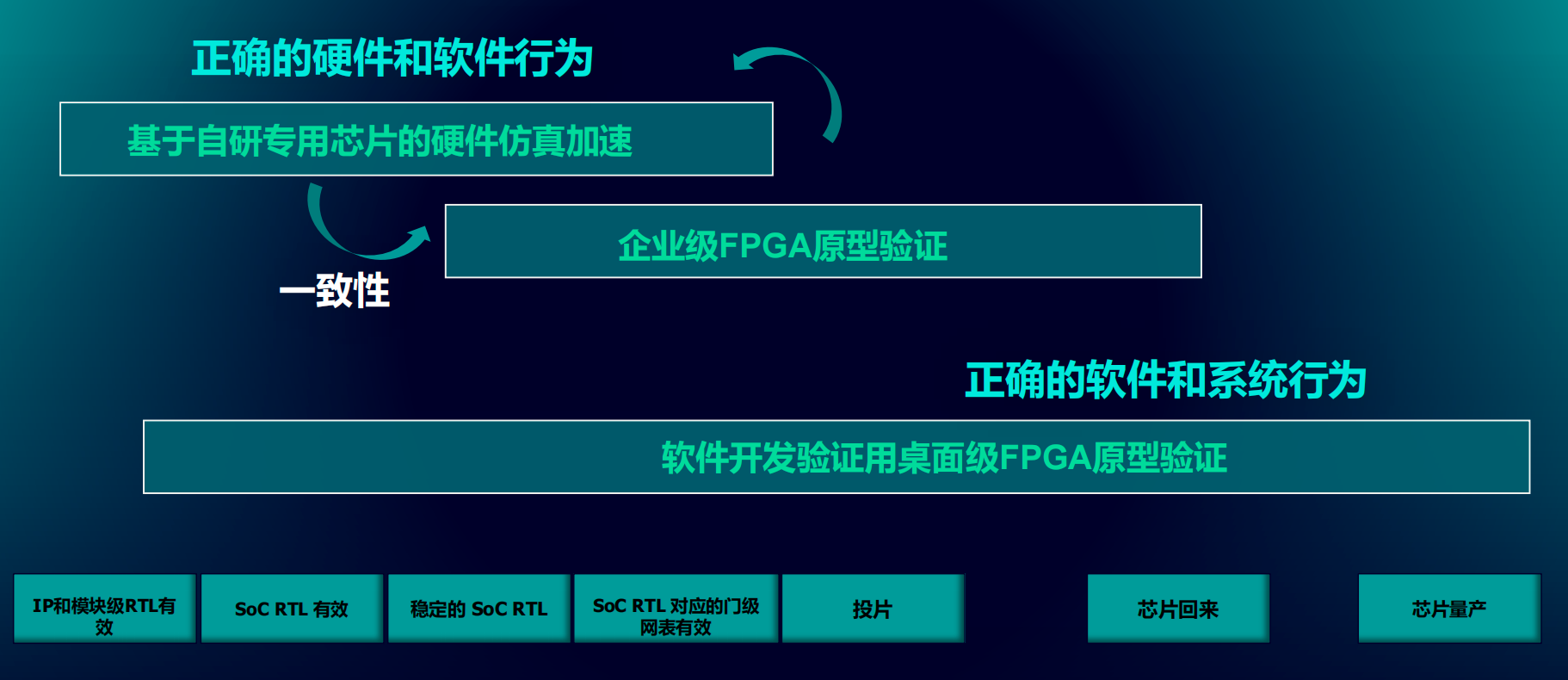

基于自研芯片+顶级AMD FPGA,西门子EDA发布“快而全”的Veloce CS

复杂的芯片设计验证环境

复杂的芯片设计验证环境

评论