芯片验证和调试,可以说是芯片开发中最具挑战性的环节,通常需要耗费开发者们大量的时间和精力。

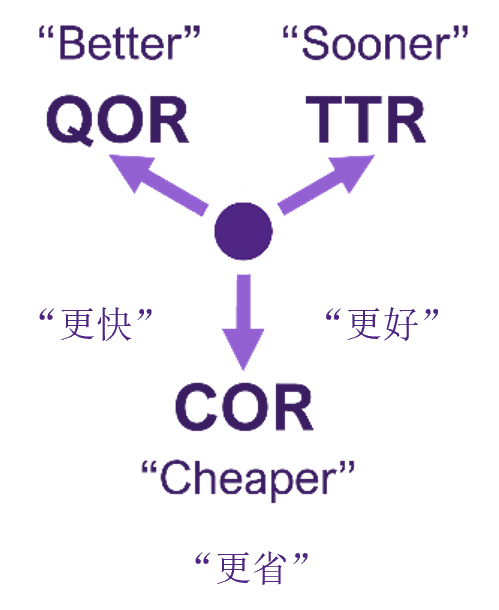

多年来,研究表明,每一代芯片上用于验证阶段的时间和资源占比均呈现不断增加的态势。总体而言,验证阶段工作的增长速度超过了芯片开发项目的其他阶段。团队要求芯片验证能够以更少的时间和资源来实现更好的结果。也就是说,验证工具和技术不仅要紧跟市场需求,同时还要考虑三个维度:设计质量(QoR)、结果完成时间(TTR)、实现成本(CoR)。

基于机器学习(ML)的人工智能(AI)技术可以显著改善芯片验证的这三个维度要求,所以说,AI是芯片验证升级过程中不可或缺的关键技术。

将AI技术用于

静态验证和形式验证

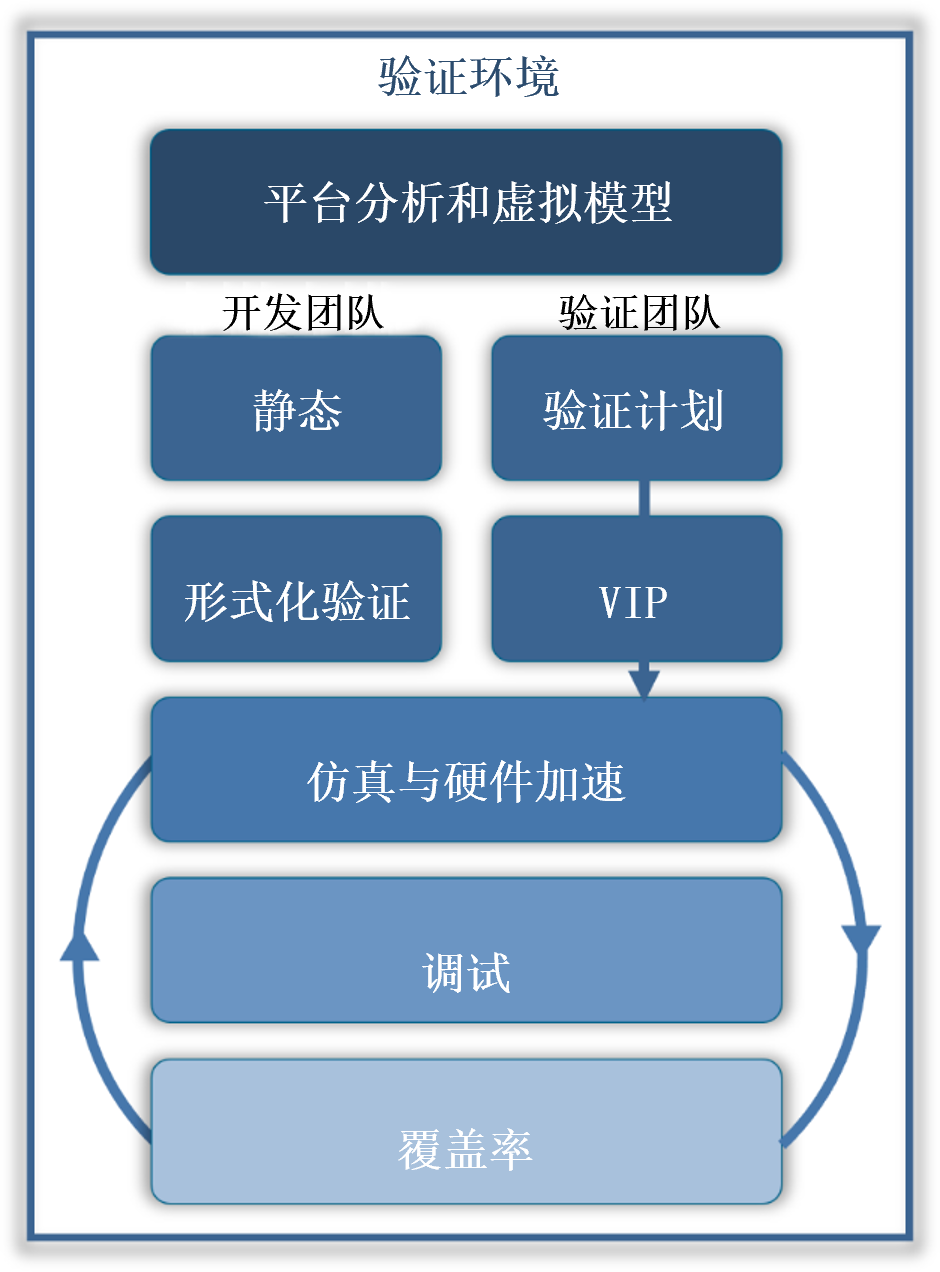

在了解AI技术如何赋能芯片验证之前,先来看看一个典型的芯片验证流程是怎样的:

首先,在开发者编写寄存器传输级(RTL)代码之前,架构团队会构建芯片的虚拟模型并分析系统性能。待做出关键决策后,设计团队将开发RTL模型,并通过使用具有强大语言校验功能的集成开发环境(IDE)来捕获编码错误,并进行修复。

修复校验错误后,开发者将运行静态验证工具来检测设计中的结构错误。

之后,开发者们通过形式验证所提供的更深入的分析,尝试证明RTL设计的关键属性。这些工具可由开发者运行,也可以与形式化验证专家合作完成。

与此同时,验证团队通常会利用现有的验证IP(VIP)开发测试平台和模型,运行一系列测试以实现验证计划的目标。此类测试主要在仿真环境中运行,但近年来使用硬件加速平台也变得越来越普遍。

覆盖率指标是衡量验证进度的主要方法。覆盖率收敛是一个高度迭代的过程,这往往也是验证计划中最耗时的部分。

▲ 芯片验证流程的高维度视图

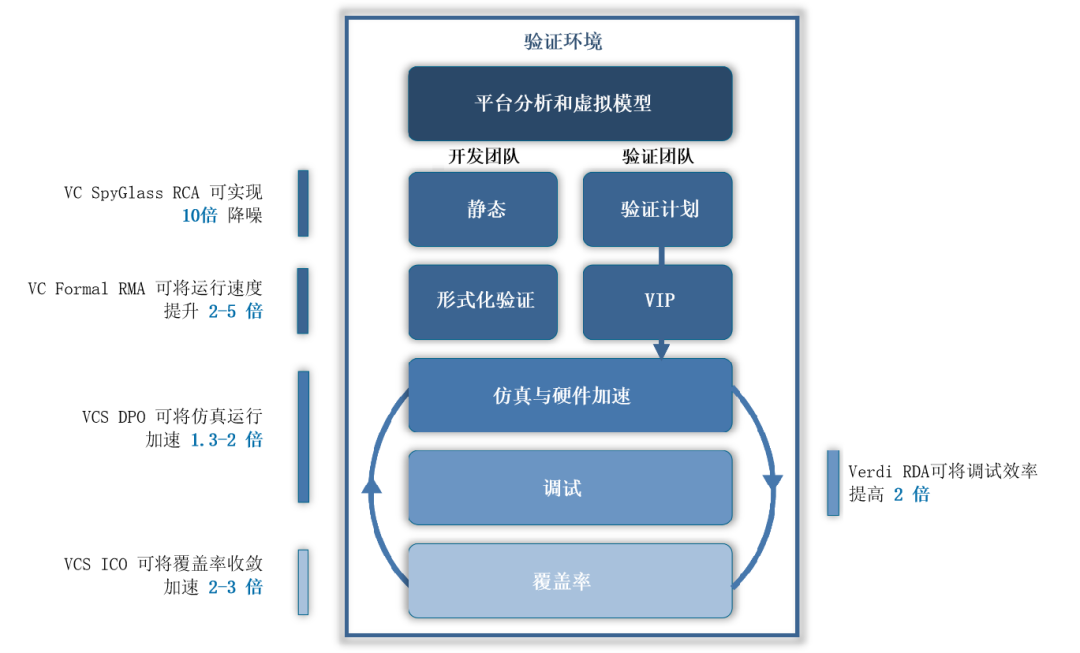

在静态验证过程中,一个错误就可能会导致数百甚至数千个违例的出现,对开发者来说是件非常头大的事情。在这一过程中引入AI/ML是非常有用的,AI/ML可以根据相似的特征将违例进行自动归类,在此基础上,开发者还可利用根本原因分析(RCA)专门识别和修复每个群组中的某一个违例行为,进而解决相应群组中的其余违规行为,这种自动化可以将调试效率提高10倍。新思科技用于静态验证的VC SpyGlass平台和用于特定低功耗静态验证的VC LP就包含了这项AI技术。

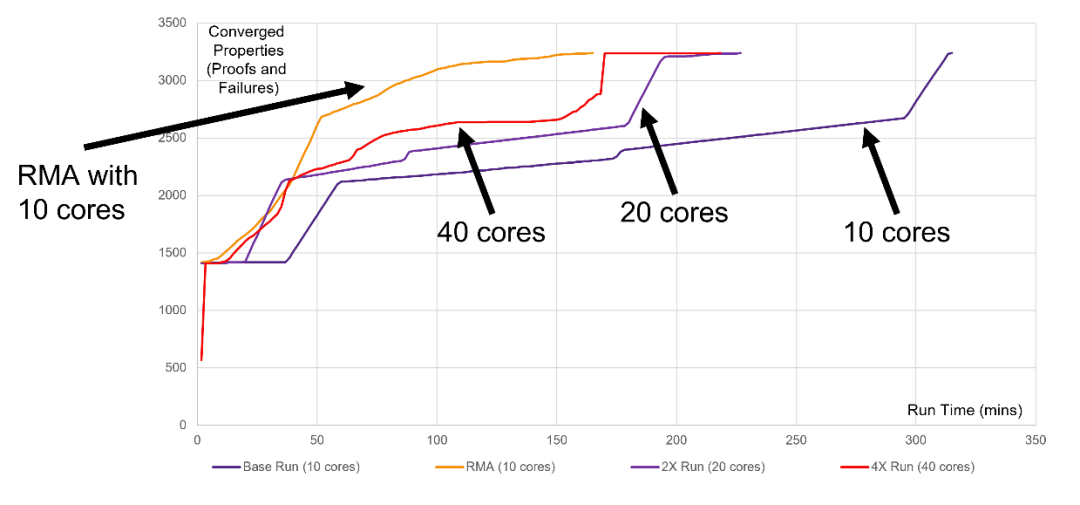

形式验证是检测设计过程中深层错误最有效的方法,这些错误在仿真测试中很可能会遗漏。为了做到全面检测,形式验证使用了大量强大的引擎来来对验证过程中所需要的成千上万的设计属性进行证明。因此最大限度地提高引擎性能,对于确保形式验证的效率至关重要。

新思科技VC Formal 是业内首个在引擎编排、回归和调试中利用ML技术的形式化验证工具。引擎编排旨在将引擎与属性正确配对,在物理计算资源和时间的限制下实现最短运行时间和最佳收敛效果。VC Formal在处理每个属性时均采用即时强化学习法,同时学习有效和无效内容,以指导下一组操作的编排,这一功能称为“智能策略选择”。此外,针对每个属性所做的决定会在运行结束时保存到数据库中,以便利用之前的学习成果优化后续运行结果,这个叫做“回归模式加速器”(RMA)。

基准数据显示,此类ML技术可将速度提升10倍以上,带来额外的收敛效果,在降低TTR和COR的同时提高QOR。

▲ 利用RMA加快属性收敛

将AI技术用于

仿真和调试

仿真是芯片验证的核心,仿真类错误约占错误发现总数的65%。

有时,为修复错误而对设计所做的更改可能无法正常工作或引入了新的问题,因此频繁的回归对于快速检测问题并保持项目的正常进行至关重要。

仿真和回归性能存在数个影响因素,而其中至少两个因素可采用AI进行改进。首先是仿真和回归运行时的设置。现代仿真器有许多选项和开关,会对性能产生重大影响。验证开发者需要时间和专业知识来优化特定设计和测试平台的仿真器设置。而随着代码的演进,可能需要调整设置以保持最佳性能。利用ML来学习并维护仿真器选项和开关这一自动化过程可以极大地提高回归性能和效率。

新思科技的VCS仿真器中的动态性能优化(DPO)技术就是利用AI来改进仿真性能,它使用ML和基于规则的AI技术从先前的回归运行中进行学习,自动调整VCS设置以获得最佳性能。这一过程将自动完成,无需用户输入。与手动进行仿真器设置相比,DPO可使仿真运行速度提高1.3-2倍。

对整体回归性能影响最大的是覆盖率收敛所需的时间。以前,验证开发者会审查仿真报告以确定未达到的覆盖率,然后修改测试或编写新测试以覆盖设计中的缺失部分。有了受约束的随机测试平台,他们通常是修改测试平台的约束条件,以便将自动刺激生成集中于未覆盖的情况,但这仍然需要手动完成。重复已经实现的覆盖会浪费大量时间。AI/ML在验证中的另一项应用可以改善这一情况,VCS仿真器的智能覆盖优化(ICO)功能可以优化受约束的随机刺激的统计质量,并提供对影响覆盖率的测试问题的分析结果。在最近的芯片项目中,ICO已经被证明可将覆盖率的收敛速度提高2-3倍。验证团队可以在更短的时间内实现更高的总覆盖率,从而缩短时间并节省资源。

调试是验证流程的最后一步,它与仿真是同时进行的。在项目期间会运行无数次仿真回归。每次回归失败时,验证团队都必须检查报告并调试失败的原因。RTL和测试平台代码会随着错误的修复以及新功能的添加和测试而不断变化,回归失败已是家常便饭。但手动处理日常的回归失败给验证工程资源造成了巨大负担。如今,AI/ML技术可以助力解决这一问题。尽管仿真测试失败的原因通常比静态违规行为要复杂得多,但自动RCA的原则仍然适用。

新思科技的Verdi自动调试系统中的回归调试自动化(RDA)功能可根据故障特征自动将故障分类,比如故障是来自设计还是测试平台,然后这些故障会被自动分箱,再通过RCA找出具体分类中故障的原因。RDA技术可以将整体调试效率提高2倍。

▲ 新思科技验证流程采用AI/ML技术带来的优势

下载白皮书

借助AI实现更快更好更高效的验证

AI和ML技术在芯片设计和验证流程中的应用与日俱增。单就验证而言,AI/ML可以加速静态验证的故障分析,提升形式化验证的性能,提高仿真效率,加速覆盖率收敛,快速轻松地完成仿真调试。图9总结了流程改进为验证团队和整个芯片项目带来的好处。新思科技的解决方案通过提供更好的QOR、更快的TTR和更省的COR来实现验证团队的目标并解决其所面临的主要挑战。如今,强大而灵活的AI/ML技术已多点开花,改进验证流程的多个方面。

新思科技发布芯片验证白皮书《借助AI实现更快、更好、更高效的验证》,更加详细的阐述了本文中提到的种种验证挑战,以及AI技术带来的改变,和新思科技EDA解决方案中一些具体功能。

审核编辑:汤梓红

-

AI

+关注

关注

87文章

30946浏览量

269190 -

新思科技

+关注

关注

5文章

798浏览量

50343 -

芯片验证

+关注

关注

5文章

34浏览量

47231

原文标题:注入AI的芯片验证有多高效?翻开这份白皮书获取答案【附下载】

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

“视网膜”重装来袭 AI技术为视频业务场景赋能

新能力上线 | 讯飞AI能力星云赋能,4项OCR技术助力“证”途!

【HarmonyOS HiSpark AI Camera】AI功能摄像机验证

机器学习如何赋能风力发电?

AI赋能“电子哨兵”推动城市的智能化和数字化进程(附“电子哨兵”方案)

英码科技精彩亮相火爆的IOTE 2023,多面赋能AIoT产业发展!

2018 AI为谁赋能 如何打造AI企业核心竞争力

AI技术正在赋能我国提升疫情治理

AI技术如何赋能智慧交通?

高通AI技术如何赋能物联网等广阔领域?

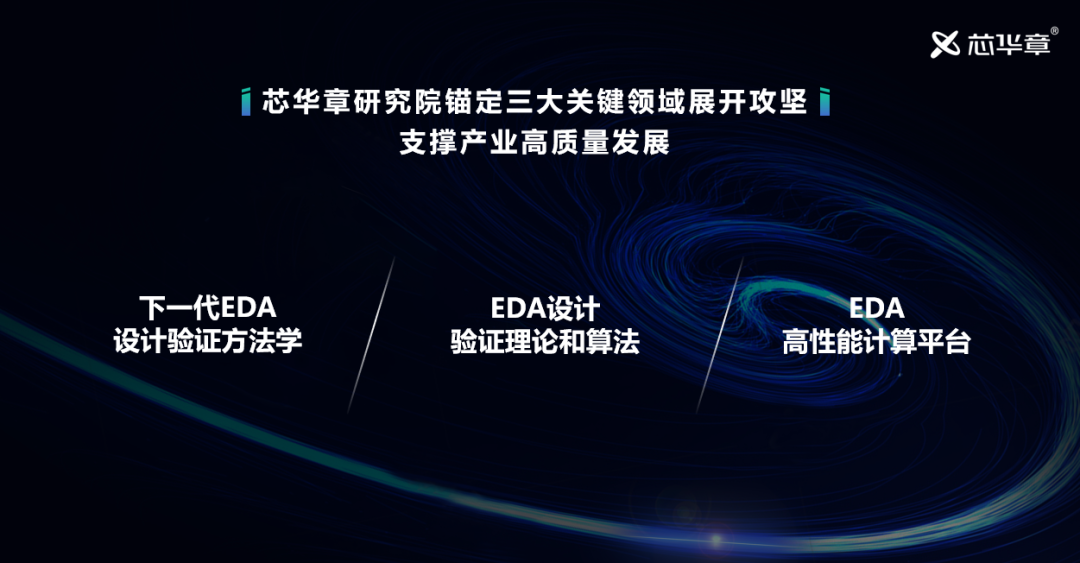

光计算赋能 芯华章研究院携手曦智科技 联合打造芯片验证黑科技

AI技术如何赋能芯片验证

AI技术如何赋能芯片验证

评论