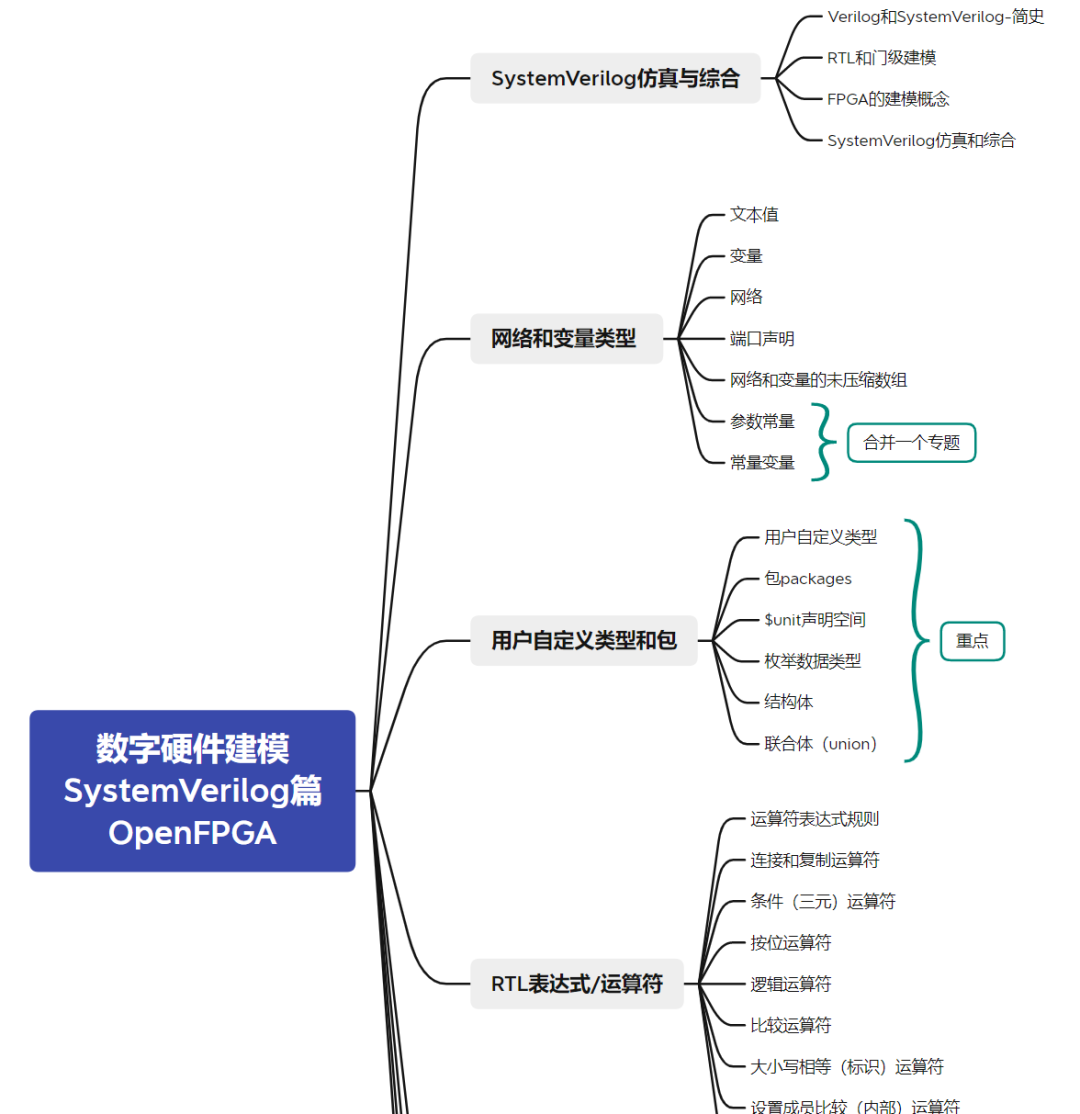

数字硬件建模SystemVerilog-连接和复制运算符

经过几周的更新,SV核心部分用户自定义类型和包内容已更新完毕,接下来就是RTL表达式和运算符。

马上HDLBits-SystemVerilog版本也开始准备了,基本这一部分完成后就开始更新~

介绍

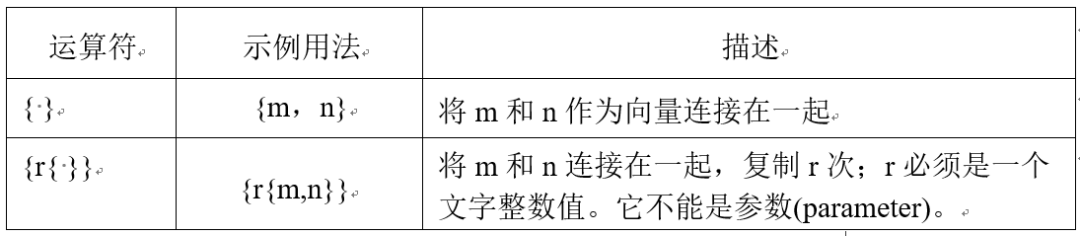

连接和复制运算符将多个表达式连接在一起,形成一个向量表达式。结果向量中的位总数是每个子表达式中所有位的总和。连接有两种形式,简单连接和复制连接。一个简单的连接将任意数量的表达式连接在一起。复制连接将表达式连接在一起,然后复制指定次数的结果。表5-3显示了连接和复制运算符的一般语法和用法:

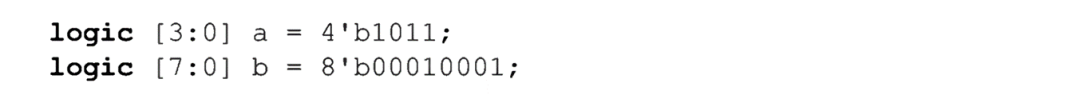

以下变量和值用于显示这些运算符的结果。

-

{a,b}结果是101100010001(二进制),一个12位的值。

-

{4’hF,a}结果是1111_1011(二进制),一个8位的值。

-

{8{2’bl0}}结果是1010101010101010(二进制),一个16位的值,2’b01重复8次。

-

{{4{a[3]}},a} 结果是11111011(二进制)一个8位的值, a的有效位重复4次,然后连接到a。

连接和复制运算符是可综合的。运算符不直接表示硬件中的任何逻辑功能。它们只是表示同时使用多个信号,将文字值附加到信号或文字值。

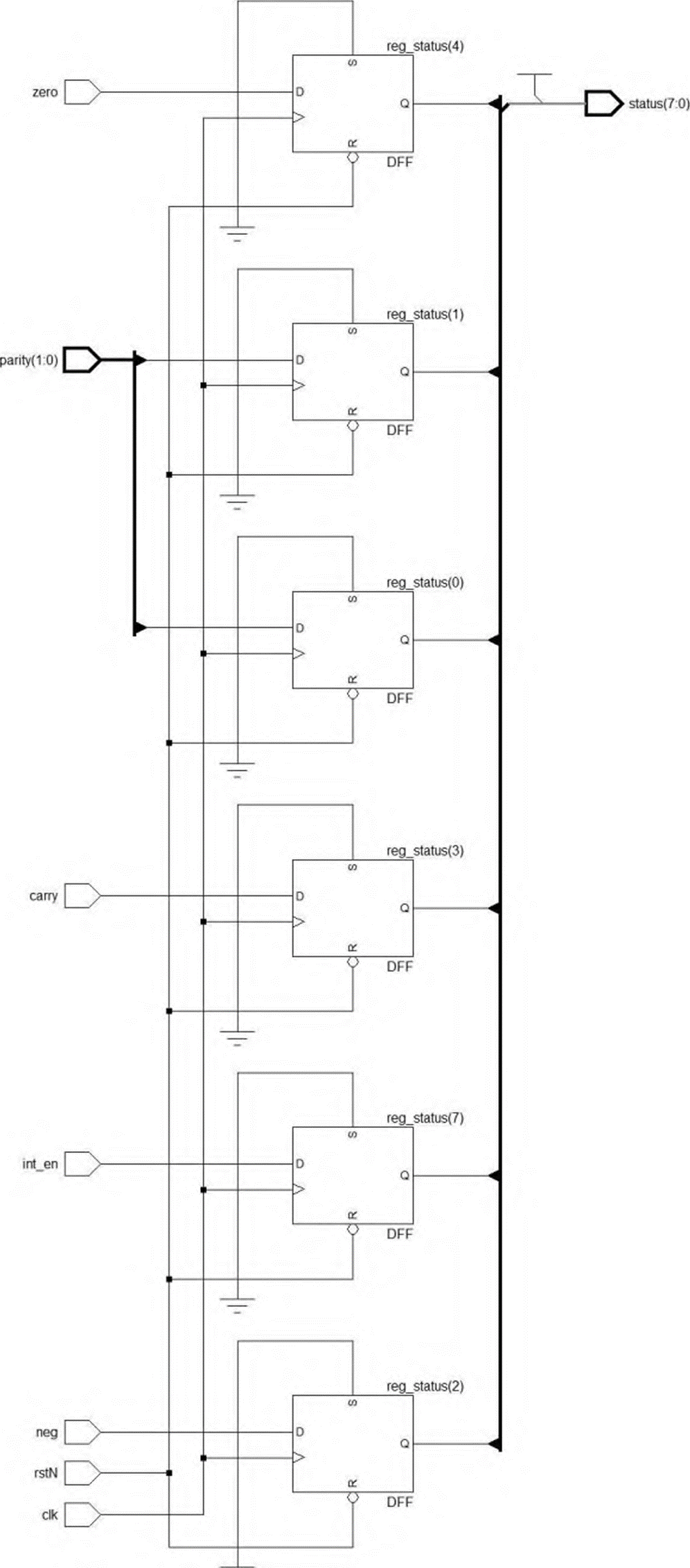

示例5-1和5-2说明了连接运算符在RTL建模中的两种常见应用:

在赋值语句的右侧或左侧将多个信号连接在一起。在每个示例之后,图5-1和5-2显示了连接运算符如何在综合生成的门级功能。然而,在RTL模型中,连接运算符是一种有用的构造,用于以简洁的方式表示硬件功能。

//`begin_keywords"1800-2012"//useSystemVerilog-2012keywords

modulestatus_reg

(inputlogicclk,//registerclk

inputlogicrstN,//active-lowreset

inputlogicint_en,//1-bitinterruptenable

inputlogiczero,//1-bitresult=0flag

inputlogiccarry,//1-bitresultoverflowflag

inputlogicneg,//1-bitnegativeresultflag

inputlogic[1:0]parity,//2-bitparitybits

outputlogic[7:0]status//8-bitstatusregisteroutput

);

timeunit1ns;timeprecision1ns;

always_ff@(posedgeclkornegedgerstN)//asyncreset

if(!rstN)//active-lowreset

status<= {1'b0,2'b11,5'b0};//reset

else

status<= {int_en,2'b11,zero,carry,neg,parity};//load

endmodule:status_reg

//`end_keywords

| 笔记 |

|---|

| 综合编译器实现运算符的方式会受到许多因素的影响,包括目标设备、与运算符一起使用的其他运算符或编程语句、使用的综合编译器,以及”指定的综合选项和约束。 |

示例5-1中的状态寄存器有两个未使用的位,它们的常量值为1,用于生成图5-1所示状态寄存器实现的综合编译器将这两个未使用的位映射到8位上拉输出上。其他综合编译器,或者指定不同的综合约束,可能会以不同的方式映射相同的RTL功能,例如通过使用预设为1值的触发器

//`begin_keywords"1800-2012"

modulertl_adder

(inputlogica,b,ci,

outputlogicsum,co

);

timeunit1ns;timeprecision1ns;

assign{co,sum}=a+b+ci;

endmodule:rtl_adder

//`end_keywords

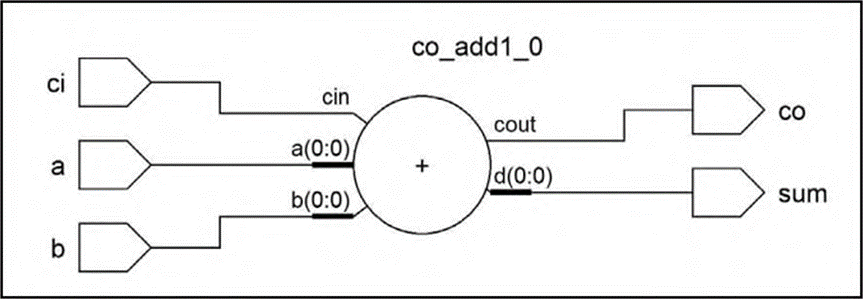

用于生成图5-2所示实现的综合编译器将RTL加法器功能映射到通用加法器块——综合的下一步将针对特定的ASIC或FPGA设备,通用加法器将在该步骤中映射到特定的加法器实现。

连接和复制运算符经常用于创建用作其他运算符操作数的表达式。这方面的例子将在本章后面的章节和后面的章节中看到。

在使用连接时,有一些重要的规则需要注意:

- 可以将任何多个表达式连接在一起,只包括一个表达式,

- 连接中的表达式必须具有固定大小。无大小的文字值不允许使用,例如数字5和’1,是不被允许的。

- 连接的结果始终是无符号的,无论连接中表达式的符号是什么。

不要将连接与赋值列表混淆。SystemVerilog有一个包含在’{and}(赋值列表)标记之间的赋值列表运算符。虽然赋值列表运算符看起来类似于连接运算符,但其功能却大不相同。赋值列表运算符将多个值连接在一起,以创建一个新的单个值。赋值列表运算符以撇号开头(’),并且用于将单个值的集合分配给数组的单个元素或结构的单个成员。

审核编辑:汤梓红

-

RTL

+关注

关注

1文章

387浏览量

60298 -

运算符

+关注

关注

0文章

172浏览量

11210

原文标题:SystemVerilog-连接和复制运算符

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

基于运算符信息的数学表达式检索技术

RTL表达式和运算符

RTL表达式和运算符

评论