本来没有在那个地方设计电容,但由于布线之间总是有互容,互容就好像是寄生在布线之间的一样,所以叫寄生电容

寄生电容:

本质上还是电容,满足i=c*du/dt。

电容是用来衡量储存电荷能力的物理量。根据Q=CU,在相同电压下,电容越大,所能储存的电荷就越多。

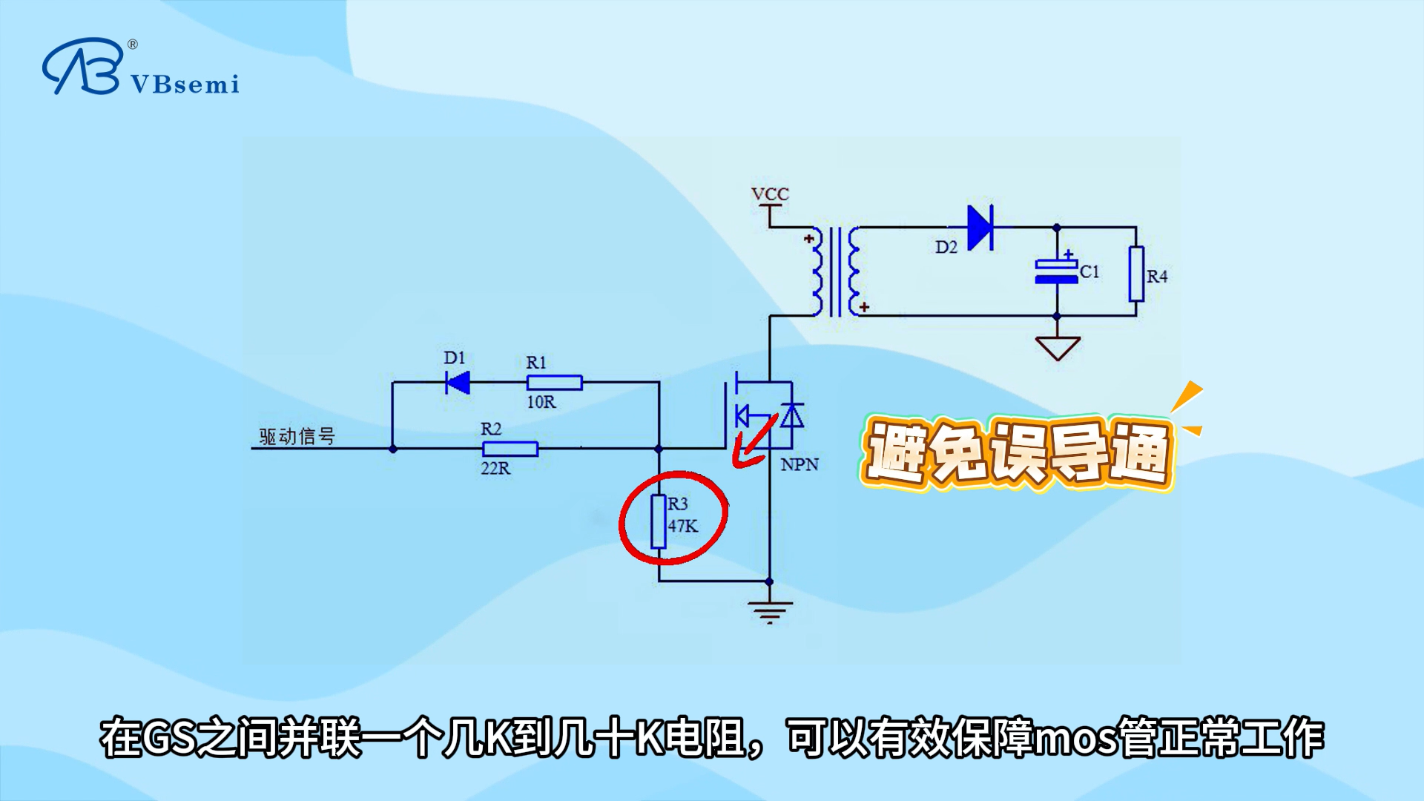

简单来讲,任何两个面之间都有寄生电容。但同样,这两个面的大小,位置关系,两个面中间的介质材料等因素都会影响寄生电容的大小。举个例子,变压器的每匝导线间,都会有寄生电容,在有些情况下,这个电容的充放电会影响变压器的特性,需要特殊设计与考虑。

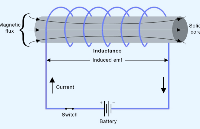

寄生电感:

本质是电感,具备电感特征,满足u=L*di/dt。

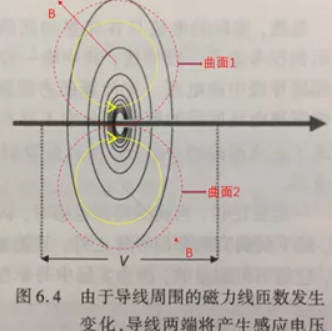

穿过线圈的磁通量发生变化时,线圈中会产生感应电势。因此用电感来衡量线圈产生电磁感应能力的强弱,电感越大,在磁通量变化时,产生的感应电压就越强。

寄生电感是指这个电感不是设计时故意设计出来的,是附加在某些东西上产生的。简单来讲,有导线的地方就有寄生电感。但不同特性的导线所携带的寄生电感是不同的。比如直导线肯定比线圈型导线的寄生电感要小。举个例子,在电源系统PCB布线中,每一条布线都会携带一定的寄生电感,一般尽量减小关键换流回路的寄生电感,这是因为,当换流回路发生电流变化时,寄生电感上产生的感应电压容易损坏元器件。

审核编辑 黄昊宇

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

电路设计

+关注

关注

6746文章

2800浏览量

220370 -

寄生电容

+关注

关注

1文章

303浏览量

20373 -

寄生电感

+关注

关注

1文章

171浏览量

15101

发布评论请先 登录

相关推荐

热点推荐

如何选择适合高频电路的贴片电感?

、频率适配性:自谐振频率(SRF)是核心门槛 贴片电感在高频下会因寄生电容产生自谐振现象,当工作频率接近或超过自谐振频率(SRF)时,电感将呈现电容性,导致阻抗骤降、损耗激增。因此,

宽带锥形电感应用场景

成为“隐形杀手”——传统电感会因寄生电容产生自谐振,完全失去功能。正是这些对“宽带、低损、低寄生、高信号完整性”的极致追求,让采用特殊结构设计的锥形电感成为高速光通信系统中不可或缺的关

发表于 03-10 11:24

TH2839阻抗分析仪在LED驱动集成电路寄生参数测试分析中的应用

随着LED照明技术的快速发展,LED驱动集成电路作为核心控制部件,其性能直接影响照明系统的效率、稳定性和寿命。在实际工程应用中,除了关注驱动IC的主功能外,寄生参数(如寄生电容、寄生电感

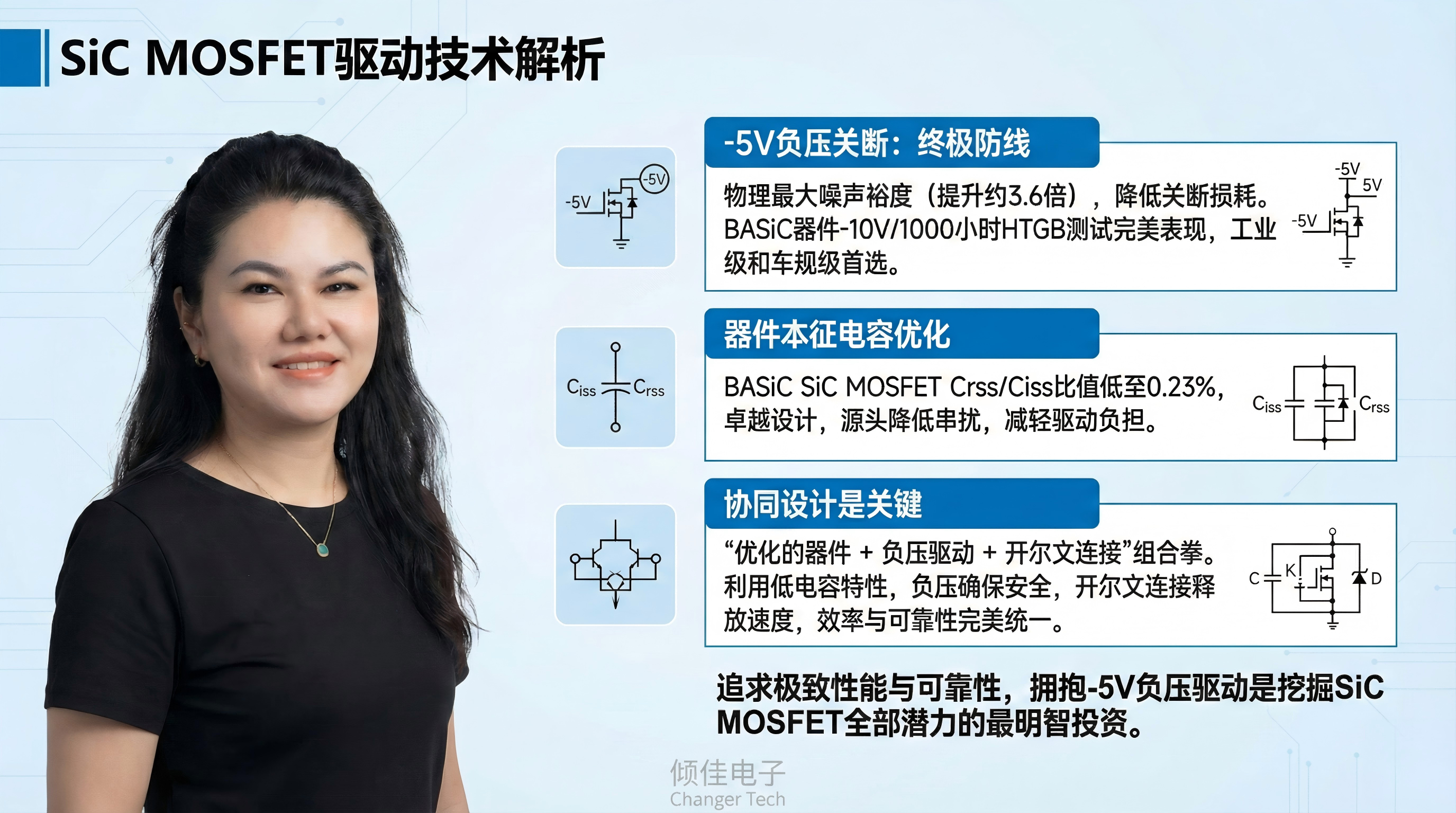

碳化硅MOSFET串扰抑制策略深度解析:负压关断与寄生电容分压的根本性优势

倾佳电子剖析SiC MOSFET串扰问题的物理机制,并对各类抑制措施进行详尽的比较分析。报告的核心论点在于:通过优化器件本征参数实现的寄生电容分压优化,以及采用-5V负压关断驱动,构成了解决串扰问题的“根本性”方案

寄生电感致电流采样失真:关键问题与解决办法

寄生电感是诱发电流采样失真的典型隐性干扰源,其主要源于PCB布线、元件引脚及外接导线等环节。在电流变化过程中,寄生电感会感应生成电动势,直接破坏采样精度。尤其在高频、大电流应用场景下,

一文带你了解线路寄生电感对开关器件的影响及解决方案

寄生电感引发的过电压、振荡和损耗问题日益突显。一、线路寄生电感在电路布局中,导线并非理想的无感导体。电流通过导线时,导线周围会产生磁场,磁场变化又会在导线中产生感

电源功率器件篇:线路寄生电感对开关器件的影响

影响,会严重影响电源系统的性能和可靠性。在实际应用中,我们需要通过优化电路布局、采用去耦电容与缓冲电路以及选择合适的开关器件等措施来有效降低线路寄生电感带来的不利影响。

森木磊石 PPEC inside

发表于 07-02 11:22

KiCad-Parasitics:KiCad 寄生参数分析插件

工具便会计算出这两点之间的直流电阻,同时还会估算出这段走线的寄生电感。 在未来的版本中,插件还将支持计算走线对地平面(ground plane)的寄生电容。 安装方式 打开插件内容管理器: 没有魔法的同学可以使用华秋国内镜像仓库

逆变器寄生电容对永磁同步电机无传感器控制的影响

摘要:逆变器非线性特性会对基于高频注人法的永磁同步电机转子位置和速度观测产生影响,不利于电机的精确控制。在分析逆变器非线性特性中寄生电容效应及其对高频载波电流响应影响的基础上,提出了一种旨在减小此

发表于 06-11 14:42

【干货分享】电源功率器件篇:变压器寄生电容对高压充电机输出功率影响

寄生电容会对充电机输出功率产生显著影响。

一、 变压器寄生电容的产生原因?

变压器的寄生电容主要包括初级与次级绕组之间的分布电容、绕组层间电容

发表于 05-30 11:31

LCR测试仪中LP(Parallel)与LS(Series)模式的区别

一、核心差异:测量模型不同 1. LP模式(并联模式) 将元件视为理想元件与寄生电阻并联的模型(如电感与寄生电容并联)。 适用于高频场景(通常>1MHz),此时元件寄生电容(如线圈分布

什么是寄生电容,什么是寄生电感

什么是寄生电容,什么是寄生电感

评论