在复杂的异构计算生态系统中,片上网络互连的发展对于片上系统技术的进步至关重要。

在复杂的异构计算生态系统中,片上网络互连的发展对于片上系统技术的进步至关重要。

计算生态系统已经完全接受了异构计算的概念——其结果是片上系统 (SoC) 的激增。现在几乎可以在市场上的所有高性能计算平台中都能找到 SoC。

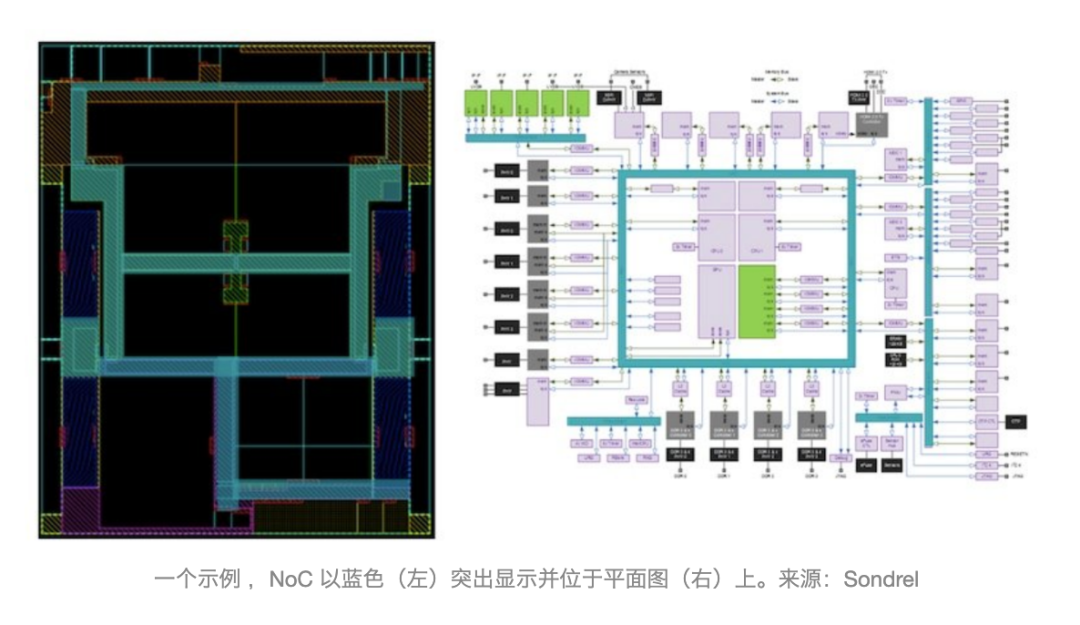

人们不太经常讨论但同样重要的技术是片上网络 (NoC)。随着 SoC继续发展,NoC 的开发也只会继续增加。最近,总部位于英国的 Sondrel 强调了 NoC 的重要性,宣布它使用 Arteris 的 FlexNoC IP 作为 Sondrel SoC 的 NoC 主干。他们认为NoC 的设计是大型高性能计算 SoC 成功的关键。Sondrel 解释说,设计人员经常忽略此数据流方面的重要性,因为负责此问题的片上网络 (NoC) 的设计很复杂,并且很难验证在所有情况下都满足性能要求,因为有很多极端案例。这导致 NoC 的次优数据传输和 SoC 无法交付。

本文将讨论异构计算的挑战、对 NoC 的需求以及FlexNoC 的一些细节。

SoC 和异构计算的挑战

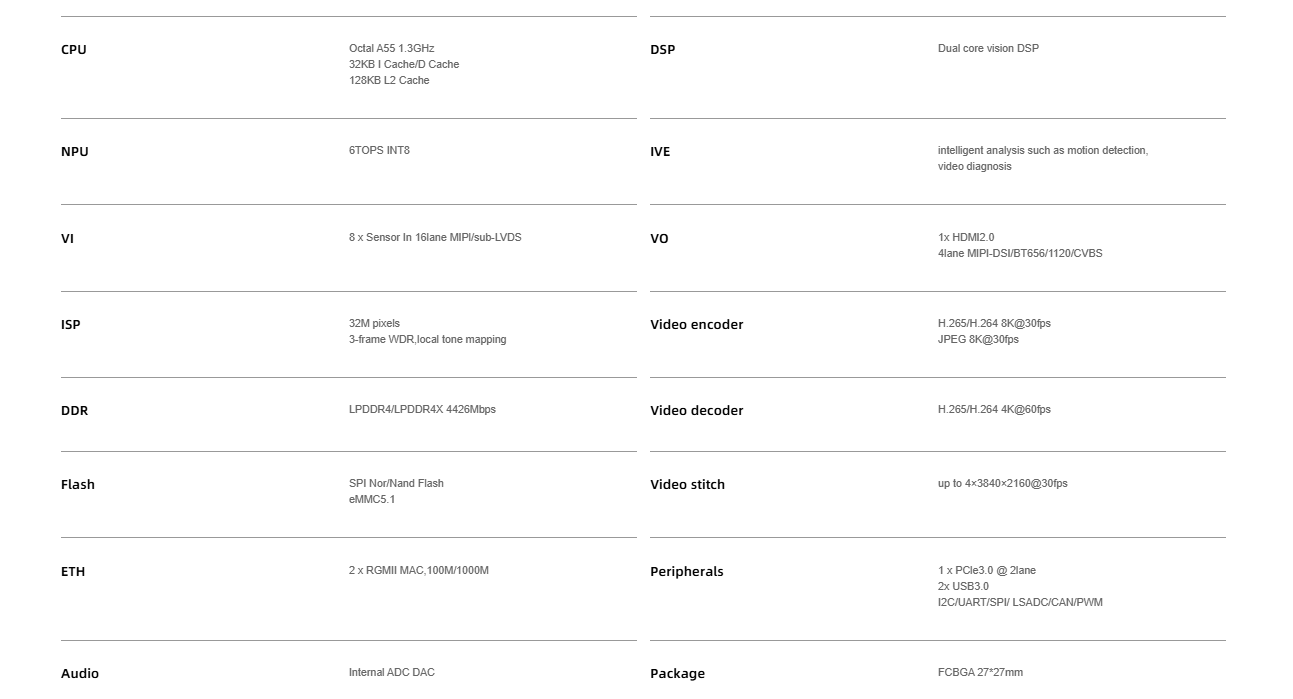

SoC 是一种单芯片解决方案,由同一芯片中的几个不同计算和功能块组成。SoC包含异构计算和硬件加速,其中有专门的计算块用于特定的计算密集型工作负载。出于这个原因,我们通常会看到一个 SoC 由一些更通用的计算模块组成,如 CPU 和 GPU,以及许多加速器模块,如神经处理单元 (NPU) 和数字信号处理器 (DSP)。

用于 SoC 的软件通常会抽象功能,以便轻松地对其进行编程和连接。SoC 的优势在于它更便宜、更小且更节能。缺点是,与全尺寸计算机不同,它们被锁定在其配置中。

虽然该方案带来了更高的性能和效率,但它有几个控制和管理问题。在数据密集型应用中,SoC 面临着如何控制、组织和管理它们预期要处理的大量数据的挑战。从布局规划的角度和系统的角度来看,控制进出内存的数据流和不同功能块的数量是一个不小的问题。

什么是 NoC?

为了解决这些与数据相关的问题,几乎每个 SoC 都依赖于NoC。

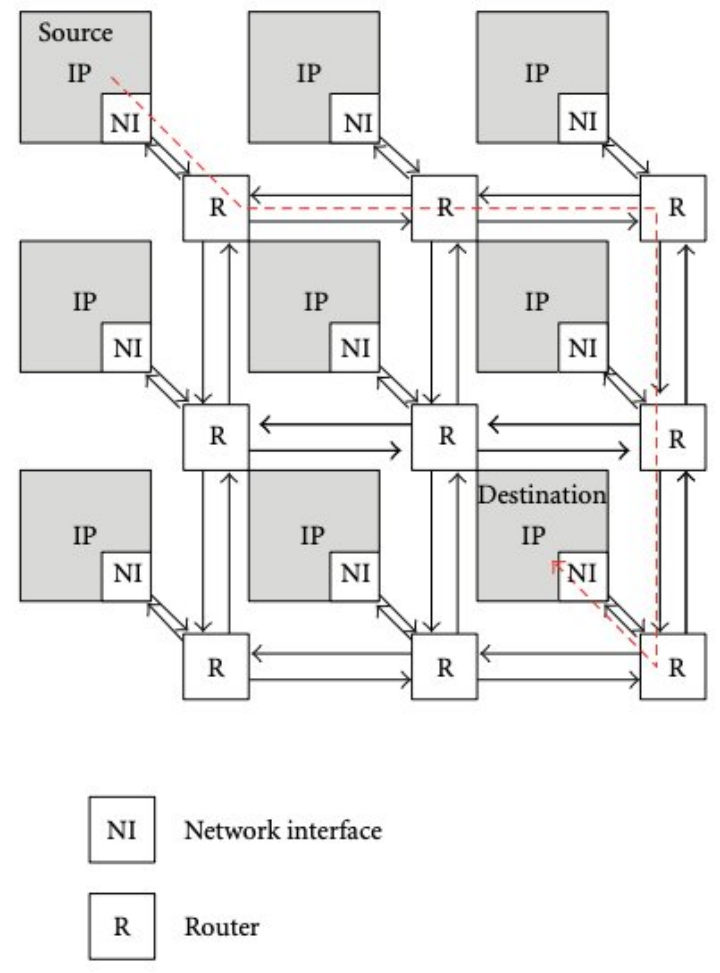

NoC 几乎互连了 SoC 的每个部分,为数据从一个块流向另一个块创建了一条清晰且定义明确的路径。通常,NoC 将由多段布线和路由器组成,这些布线和路由器的布置旨在减少寄生效应,从而避免在整个SoC中更大的损失和延迟。这通常采用类似城市布局的网格结构的形式。

网状拓扑中的 NoC。来源:ACM 数字图书馆

NoC 通过使用网络接口 (NI) 模块控制整个 SoC 中的数据流。这些模块通常用于将处理器内核生成的数据包转换为固定长度的流量控制数字。这些数字允许 NoC 内的路由器将数据适当地引导到所需的功能块。

传统上,NoC 功能可以定义为多个层之一,包括应用层、传输层、网络层、数据链路层和物理层。出于这个原因,NoC 路由器将需要硬件和软件实现,以便它可以支持给定层的功能。

通常,设计人员首先从平面图或 NoC 开始芯片设计。新的方法通过在非常早的阶段进行性能探索来稳定性能要求,从而稳定和测试架构以减少更改的可能性,从而稳定平面图和 NoC,从而避免了一些意外情况。性能探索解决了 IP 块通常被单独隔离验证的问题。但是,这并没有考虑到它们与其他 IP 块的交互。芯片上的 IP 越多,它们之间可能严重影响芯片性能的几率就可能会增加。

Sondrel 使用 FlexNoC

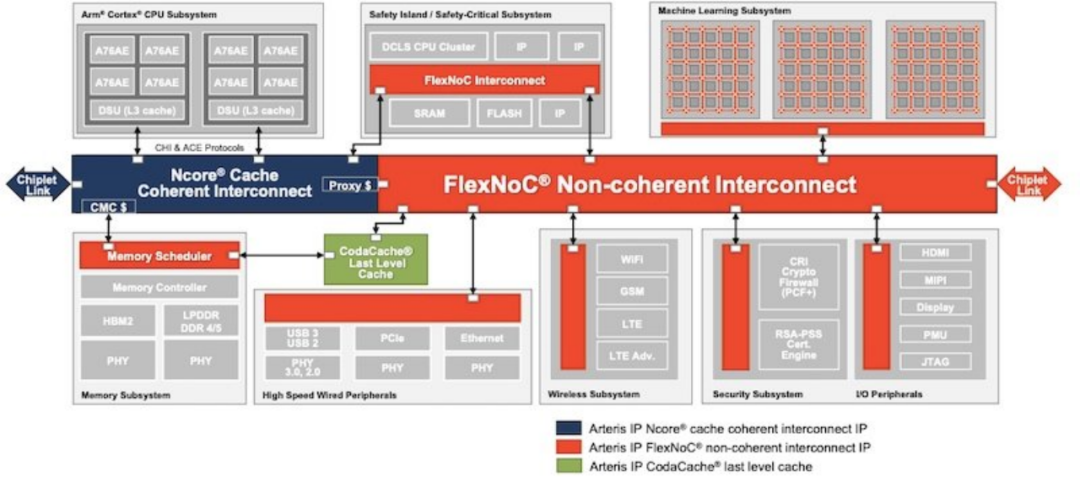

2022 年 6 月 22 日,Sondrel 透露,它使用Arteris 的 FlexNoC IP作为其所有 SoC 解决方案的 NoC 主干。

Arteris 解释说,NoC 互连构成了 SoC 架构。来源:Arteris

Sondrel认为使用 FlexNoC 互连技术的一些具体好处首先是能够减少面积和线数。这是通过利用传输层打包和序列化功能来完成的,这样 NoC 架构师可以精确控制 NoC 的哪些部分可以从减少的线路和面积中受益,而不会影响性能要求。其次,通过使用电源管理功能降低功耗,例如配置时钟域交叉和时钟门控支持的选项,以确保功耗在功耗预算范围内。另外的好处就是能够创建物理感知设计,因为设计团队能够将网表交给后端团队,保证满足时序要求,因为 NoC 设计方法从一开始就考虑了 SoC 布局规划和任何物理设计约束该设计。最后,FlexNoc 拥有先进的配置工具和出色的 UI。为生成高性能、时序清洁的互连而提供的工具套件直观且非常容易让 NoC 架构师熟悉,从而提高生产力。

与 Sondrel 一样,业内许多公司都在竞相生产最好的 NoC IP,以生产面积和功耗更低的 SoC,同时让 SoC 设计更容易实现。

审核编辑 :李倩

-

soc

+关注

关注

40文章

4638浏览量

230353 -

片上系统

+关注

关注

0文章

205浏览量

27734

原文标题:为什么 SoC 需要 NoC:片上网络和计算的未来

文章出处:【微信号:ICViews,微信公众号:半导体产业纵横】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

基于openEuler平台的CPU、GPU与FPGA异构加速实战

XC7Z020-2CLG484I 双核异构架构 全能型 SoC

美光科技与联想车计算引领车载存储新篇章

【TEC100TAI-KIT】青翼凌云科技基于JFMQL100TAI的全国产化智能异构计算平台

机器人芯片:驱动智能机器的核心技术引擎

PCIe协议分析仪能测试哪些设备?

【PZ-ZU15EG-KFB】——ZYNQ UltraScale + 异构架构下的智能边缘计算标杆

异构计算构建更智能、更高效的AI未来

基于DE1-SOC开发板的oneAPI实验教程(1)

异构计算解决方案(兼容不同硬件架构)

润和软件发布StackRUNS异构分布式推理框架

如何释放异构计算的潜能?Imagination与Baya Systems的系统架构实践启示

能效提升3倍!异构计算架构让AI跑得更快更省电

Imagination与澎峰科技携手推动GPU+AI解决方案,共拓计算生态

为旌科技VS859:国产具身智能“感算控”一体SoC,赋能边缘多模态智能场景

SoC和异构计算的挑战

SoC和异构计算的挑战

评论