克服 5nm 节点以下未来晶体管技术的挑战

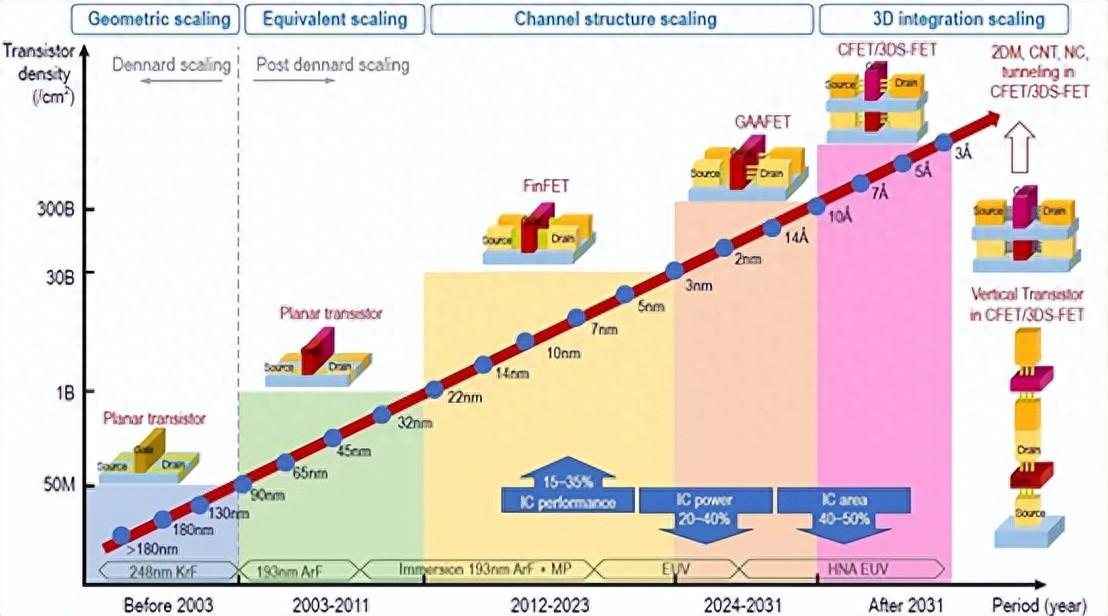

“半导体时代”始于 1960 年集成电路的发明。在集成电路中,所有有源-无源元件及其互连都集成在单个硅晶片上,在便携性、功能性、功率和性能方面具有众多优势。数十年来,VLSI 行业一直遵循摩尔定律,即“芯片上的晶体管数量大约每两年翻一番”。为了获得缩小晶体管的好处,VLSI 行业正在不断改进晶体管结构和材料、制造技术以及设计 IC 的工具。迄今为止,晶体管已采用各种技术,包括高 K 电介质、金属栅极、应变硅、双图案化、从多侧控制沟道、绝缘体上硅等技术。其中一些技术在“关于 CMOS、SOI 和 FinFET 技术的评论论文”中进行了讨论。 [1]

如今,物联网、自动驾驶汽车、机器学习、人工智能和互联网流量的需求呈指数级增长,这成为将晶体管缩小到现有 7nm 节点以下以获得更高性能的驱动力。然而,缩小晶体管尺寸存在若干挑战。

亚微米技术的问题

每次我们缩小晶体管尺寸时,都会产生一个新的技术节点。我们已经看到了诸如 28nm、16nm 等晶体管尺寸。缩小晶体管尺寸可以实现更快的开关、更高的密度、低功耗、更低的每个晶体管成本以及许多其他收益。 CMOS(互补金属氧化物半导体)晶体管基础 IC 技术在 28nm 节点上表现良好。然而,如果我们将 CMOS 晶体管缩小到 28 nm 以下,短沟道效应将变得无法控制。在该节点下方,由漏源电源产生的水平电场试图控制通道。结果,栅极无法控制远离栅极的泄漏路径。

16nm/7nm晶体管技术:FinFet和FD-SOI

VLSI 行业已将 FinFET 和 SOI 晶体管用于 16nm 和 7nm 节点,因为这两种结构都能够防止这些节点的泄漏问题。这两种结构的主要目标是最大化栅极到沟道的电容并最小化漏极到沟道的电容[1]。在这两种晶体管结构中,都引入了沟道厚度缩放作为新的缩放参数。随着沟道厚度的减小,没有远离栅极区域的路径。因此,门对通道有很好的控制,从而消除了短通道效应。

在绝缘体上硅 (SOI) 晶体管中,使用了掩埋氧化物层,它将主体与图 1a 所示的衬底隔离开来。由于 BOX 层,降低了漏源寄生结电容,从而加快了开关速度。 SOI 晶体管的主要挑战是难以在晶圆上制造薄硅层。

碳纳米管的带隙可以通过其手性和直径来改变,因此可以使碳纳米管表现得像半导体。半导体 CNT 可以成为用于沟道材料的纳米级晶体管器件的有利候选者,因为它提供了优于传统硅 MOSFET 的众多优势。碳纳米管传导热量类似于钻石或蓝宝石。此外,与基于硅的设备相比,它们的切换更可靠且功耗更低。 [5]

此外,CNFETS 的跨导是其对应物的四倍。 CNT 可以与 High-K 材料集成,从而对通道提供良好的栅极控制。由于迁移率增加,CNFET 的载流子速度是 MOSFET 的两倍。 N型和P型CNFET的载流子迁移率在提供相同晶体管尺寸方面的优势方面是相似的。在 CMOS 中,由于迁移率值不同,PMOS(P 型金属氧化物半导体)晶体管的尺寸大约是 NMOS(N 型金属氧化物半导体)晶体管的 2.5 倍。

CNTFET 的制造过程是一项非常具有挑战性的任务,因为它需要方法的精度和准确性。在这里,我们讨论了顶栅 CNTFET 制造方法。

该技术的第一步从将碳纳米管放置到氧化硅衬底上开始。然后隔离各个管。源极和漏极触点使用先进的光刻技术进行定义和图案化。然后通过细化触点和CNT之间的连接来降低接触电阻。通过蒸发技术在纳米管上沉积薄的顶栅电介质。最后,为了完成该工艺,栅极触点沉积在栅极电介质上。 [6]

审核编辑:汤梓红

-

半导体

+关注

关注

334文章

27515浏览量

219795 -

晶体管

+关注

关注

77文章

9706浏览量

138485

发布评论请先 登录

相关推荐

IBM与Rapidus在多阈值电压GAA晶体管技术的新突破

晶体管与场效应管的区别 晶体管的封装类型及其特点

雪崩晶体管的定义和工作原理

PMOS晶体管的饱和状态

CMOS晶体管的尺寸规则

NMOS晶体管和PMOS晶体管的区别

CMOS晶体管和MOSFET晶体管的区别

晶体管的主要材料有哪些

GaN晶体管的应用场景有哪些

GaN晶体管和SiC晶体管有什么不同

PNP晶体管符号和结构 晶体管测试仪电路图

微电子所在《中国科学:国家科学评论》发表关于先进CMOS集成电路新结构晶体管的综述论文

台积电扩增3nm产能,部分5nm产能转向该节点

什么是达林顿晶体管?达林顿晶体管的基本电路

克服5nm节点以下未来晶体管技术的挑战(上)

克服5nm节点以下未来晶体管技术的挑战(上)

评论