TLB就是Translation Lookaside Buffer ,很多文章翻译成“旁路转换缓冲”

老实说,不知所云,不如不去翻译,就当个专有名词,理解它的含义就好了。

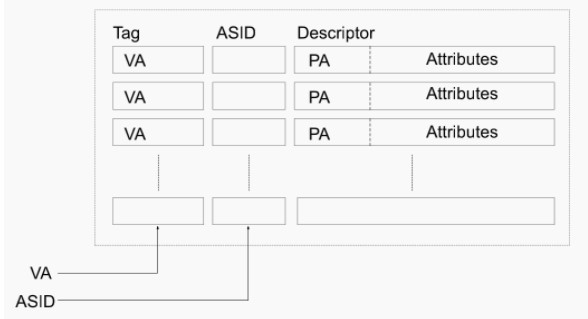

Translation Lookaside Buffer (TLB) 是 MMU 中的cache,其缓存的内容就是页表项(某个VA-PA的映射关系)。

在内存需要进行VA-PA转换时,MMU首先会在TLB中检查是否有页表项被缓存。如果TLB hit,那么TLB就能立即完成VA-PA的转换。如果TLB miss,即TLB中没有该VA对应的VA-PA映射关系,所以就需要到外部主存获取这个VA-PA转换关系,并将这个转换关系缓存到TLB中以加速下一次VA-PA转换。

micro-TLB

类似于L1 cache和L2 cache的层次结构,一般还有micro-TLB和TLB。如果页表访问在micro-TLB中hit,那么就不需要访问外面的内存。但是,micro-TLB能够缓存的页表映射有限,所以其后级往往有一个更大的main TLB。

TLB与其他cache类似,只不过其他cache缓存的是指令或者数据,而TLB缓存的是VA-PA映射关系,当TLB hit即可完成VA-PA转换。

软件异常

一般TLB只会缓存有效的VA-PA映射关系,如果这个映射关系是无效的,就需要上报异常让软件处理。

TLB一致性 & invalid

TLB一致性,同样类似于cache的一致性。

当操作系统更改页表时,TLB中就可能包含旧的无效映射关系。操作系统必须采取措施invalid TLB中的缓存的页表项。

不同的结构实现可能会专门地去invalid特性的cacheline,比如特定ASID或者特定VA。

审核编辑:刘清

-

操作系统

+关注

关注

37文章

6818浏览量

123325 -

MMU

+关注

关注

0文章

91浏览量

18287

发布评论请先 登录

相关推荐

TLB是什么?有何作用

TLB是什么?有何作用

评论