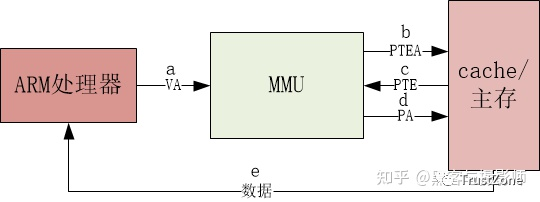

处理器中的MMU可以让我们能够构建具有多个VA-PA映射表的数字系统。

不同程序操作同一个VA,这个VA被不同的页表映射到不同的PA。

操作系统内核将每个应用程序的指令和数据放在物理内存中,但是应用程序并不是直接通过物理地址读写这些指令和数据。简单来说,就是通过MMU进行VA-PA转换,这让程序设计变得简单很多。

所有的程序员都应该了解和感谢虚拟地址,它让你的工作没那么dirty。因为这个dirty的工作被操作系统和硬件完成了。

页表

在处理器中这种VA-PA的映射关系称为页表,页表中的每一个页表项都完成了某个VA-PA的映射对应。页表格式其实还比较复杂,除了VA-PA的映射关系,还有其他的一些内存属性和访问权限定义。

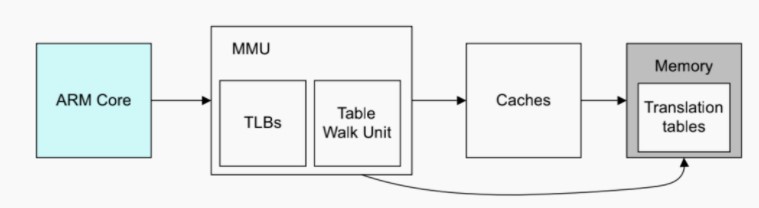

处理器内核生成的地址都是虚拟地址,然后在访问实际物理内存空间之前通过MMU映射成了物理地址。但是,基于不同的页表粒度大小,比如说4KB,实际的VA-PA的映射只是将高比特做了替换。

在早期这个VA-PA的映射过程并不是由硬件完成的,后来才由硬件完成这个VA-PA转换,形象点来说称为translation table walking。

审核编辑:刘清

-

处理器

+关注

关注

68文章

19313浏览量

230068 -

MMU

+关注

关注

0文章

91浏览量

18313

发布评论请先 登录

相关推荐

大疆嵌入式笔试题及参考,处理器读取内存的过程

通过处理器创建MC9S08DZ60芯片

ARM处理器有哪些性能呢

MMU存储管理单元的工作原理是什么?如何实现其流程呢

求助,寻找支持MMU的处理器

ARM CoreLink MMU-400系统内存管理单元技术参考手册

Arm CoreLink MMU‑700系统内存管理单元技术参考手册

ARM CORELINK™MMU-600AE系统内存管理单元技术参考手册

S3C2410内存管理单元MMU基础实验

鸿蒙轻内核源码分析:MMU 协处理器

通过处理器中的MMU进行VA-PA转换

通过处理器中的MMU进行VA-PA转换

评论