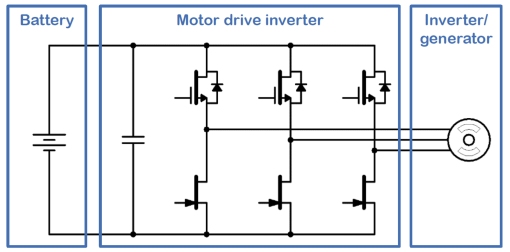

牵引应用中使用的半导体开关是实现高效率的关键部件。最新的半导体技术允许高开关频率,并且在大多数其他功率转换应用中,这会带来更小的磁性元件的好处,并与一些额外的开关损耗进行权衡。然而,在驱动逆变器中,磁性元件是电机,其尺寸适合扭矩和功率。低开关频率的更高效率通常比其他因素更重要。因此,开关频率约为 10 kHz 的IGBT已被广泛使用,它们具有坚固性、低传导损耗和相当低的动态损耗的良好记录。

从 IGBT 继续前进

效率目标变得越来越严格,这是可以理解的——每一个百分点的增长都构成了更小的尺寸、重量和成本以及更长的续驶里程的良性循环的一部分。使用 IGBT 实现的 98% 左右的数字是可信的,但存在进一步改进的压力。残余开关损耗可以通过使用硅或碳化硅 MOSFET 来降低,但从历史上看,它们在高功率水平下比 IGBT 具有更高的传导损耗。这源于它们的导通电阻、与电流平方成比例的耗散功率。IGBT 具有相对固定的饱和电压,因此在高功率时存在一个交叉点,此时 IGBT 仍占优势。客观地说,在 500 A 时,MOSFET 在工作结温下需要大约 3 mΩ 的导通电阻,以实现与 IGBT 相当的传导损耗。在 EV 牵引应用中,器件需要 650 至 750 V 的额定电压,而在这些电压下,使用单个 Si 或 SiC MOSFET 器件尚未实现导通电阻。并联 MOSFET 是一种解决方案,但随后成本和复杂性呈螺旋式上升。

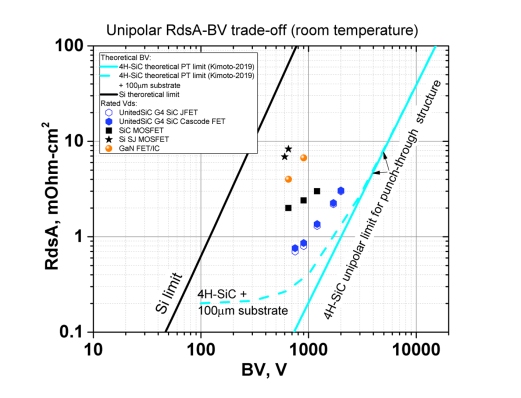

为了实现最低的传导损耗,可以考虑使用 UnitedSiC FET — SiC JFET 和 Si MOSFET 的级联组合。鉴于传导损耗在电机驱动器中占主导地位,并且功率半导体的价格通常与总芯片面积成正比,开关性能的一个有用的比较衡量标准是品质因数R DS × A。这是特定电压等级的导通电阻和芯片面积的乘积。UnitedSiC FET 具有最佳R DS × A跨越当前技术,包括宽带隙类型。与 UnitedSiC MOSFET 或氮化镓 FET 一样,本征二极管的低反向恢复能量消除了对基于 IGBT 的电机驱动器的外部反并联二极管的需求,从而进一步节省了成本。UnitedSiC FET 还可以与超结 Si MOSFET、SiC MOSFET 和 GaN HEMT 竞争,如图 1所示,该图比较了R DS × A与额定击穿电压。

图 1:开关技术的品质因数 R DS × A 与额定电压 的比较

如图所示,从历史上看,硅器件具有性能限制,而超结技术可以克服这一限制。图表中 4H-SiC 的限制在未来很可能会被类似的技术超越。如今,UnitedSiC 提供的“第 4 代”级联 FET 明显领先于竞争技术,即使在制造方面取得进步,这一领先地位仍将保持,因为 UnitedSiC FET 是基于 JFET 的,在 SiC 上没有 MOS 栅极,这是主要的R DS × A优势的原因。低R DS × A的好处降低了成本和开关损耗。UnitedSiC FET 的优势继续体现在雪崩和短路耐受额定值上,这在许多牵引应用中至关重要。SiC 上没有 MOS 栅极消除了参数随温度和电压以及高反向电流的变化。

现实生活中的结果

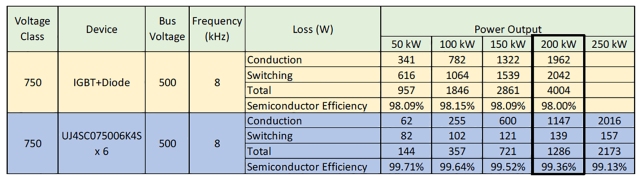

为了展示 UnitedSiC FET 与 IGBT 相比的优势,表 1显示了具有 500 VDC 总线的 200 kW、两电平电压源牵引逆变器的半导体损耗。两种器件类型的频率均为 8 kHz,总器件占位面积大致相同,采用 IGBT 加二极管模块与采用 TO-247 封装的八个并联 UnitedSiC FET 相比。在满载时,UnitedSiC FET 的总损耗为 1.3 kW,与 4 kW 的 IGBT 相比,降低了 3.1 倍。在 EV 运行常见的较轻负载下,降低幅度更大,为 5 倍至 6 倍。此外,UnitedSiC FET 栅极驱动损耗低于 IGBT,进一步提高了轻负载效率。

表 1:200 kW 牵引逆变器中 IGBT 和 UnitedSiC FET 损耗的比较

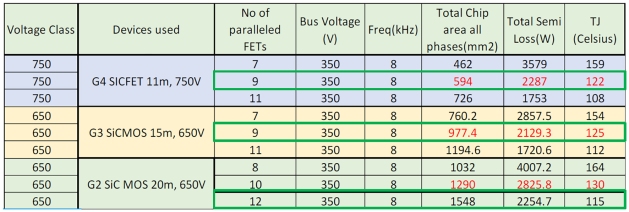

在比较 SiC MOSFET 和 UnitedSiC Gen4 FET 时,一个明显的优势是后者的 750V 额定值与更常见的 650V 额定值 SiC MOSFET 形成对比,在高电池组电压下保留了重要的设计余量。表 2将 UnitedSiC Gen4 11-mΩ FET 与竞争的 Gen2 和 Gen3 SiC MOSFET 在具有 350-VDC 总线的 200-kW 牵引逆变器中进行比较。开关频率相同,并且在三种技术中选择了并联器件的数量,以提供大致相同的损耗和结温升高。在这些条件下,UnitedSiC FET 只需要 Gen2 SiC MOSFET 解决方案总芯片面积的 60% 左右,不到 Gen3 SiC MOSFET 的 50%,从而带来成本和外形尺寸优势。或者,对于给定的芯片面积,UnitedSiC FET 具有更低的损耗。

表 2:UnitedSiC FET 和 SiC MOSFET 在 200 kW 牵引逆变器中的比较

SiC JFET 也可以发挥作用

通常选择UnitedSiC场效应管是因为共源共栅排列提供了熟悉的正常“关”特性。然而,通常“开启”的SiC JFET可用于逆变器的低压侧(或高压侧)开关位置。

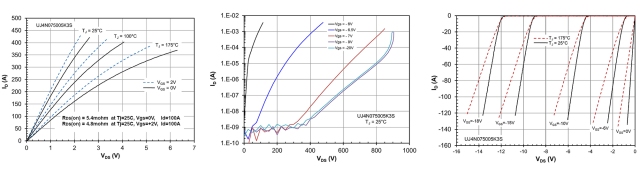

JFET的基本特性如图2所示,取自5-mΩ750-V部件的UnitedSiC数据。由于省略了串联低压硅MOSFET,导通电阻低于等效的UnitedSiC FET。左侧显示了与温度相关的正向特性,器件在VGS=0和2时导通 五、 增加JFET VG进一步增强JFET沟道并降低导通电阻。如果不超过栅源p-n结“拐点”电压,则少数载流子注入可以忽略不计,在25 马进了大门,范围从2.5到2.0左右 对于UnitedSiC Gen4 750-V JFET,分别在25˚C至175˚C下。VGS=2时 五、 与VGS=0相比,RDS(on)提高了约10% 五、

图2中的中间图像显示了设备阻塞VG≈ –10 V,泄漏电流最小。右图显示了反向传导的第三象限“换向”操作,显示了依赖于负VGS值的压降。通道应使用VG增强 = ≥最小死区时间后为0,以最小化反向电流流动的传导损耗。

图2:SiC JFET的特性(UnitedSiC UJ4N075005K3S)

SiC JFET 的导通电阻比具有相同 JFET 的级联电阻低约 9%,这是一个明显的优势。在低侧开关位置(图 3),通常“导通”的 JFET 特性也可以带来好处。如果控制电源发生故障,所有低侧开关自然打开,使电机绕组短路,从而为感应电机创造故障安全条件。电机不能向电池组产生不受控制的扭矩和功率。使用通常“关闭”的高边开关可防止击穿。

图 3:作为电机驱动器中低侧开关的 SiC JFET

另一个可能的好处是使用 JFET 栅源 pn 结作为温度敏感参数。如果使用固定的正偏置电流(例如 10 mA)驱动 SiC JFET 栅极,则生成的栅极-源极电压会随芯片温度线性变化。这可用于快速反应过热检测和性能监控。

UnitedSiC FET 和 JFET 可实现所需的效率提升

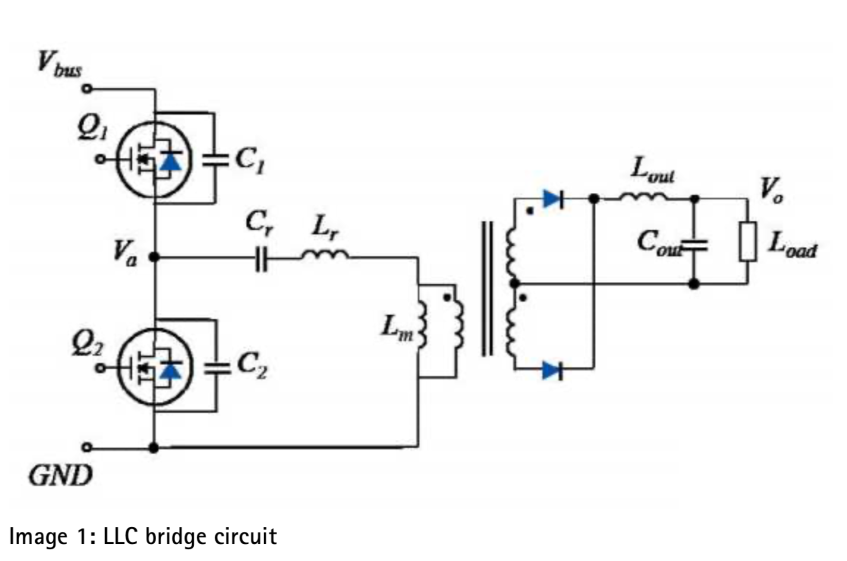

牵引逆变器驱动器中的 UnitedSiC FET 可显着提高效率,如果将 SiC JFET 用于低侧开关位置,则可进一步提高效率。这还提供了故障安全操作和简单的温度监控等宝贵的附带好处。UnitedSiC(现为 Qorvo)可以提供一系列具有导通电阻和封装选项的部件,以实现最佳的成本效益解决方案。其在线 FET-Jet Calculator 工具可以轻松选择适用于一系列 AC/DC 和 DC/DC 拓扑的器件,并针对所选散热器性能即时计算效率、损耗和温升。

审核编辑:郭婷

-

驱动器

+关注

关注

53文章

8256浏览量

146594 -

半导体

+关注

关注

334文章

27502浏览量

219733 -

逆变器

+关注

关注

285文章

4731浏览量

207134

发布评论请先 登录

相关推荐

明德扬视频分享点拨FPGA课程--第二十章 提高效率技巧

如何使用UCC28056优化过渡模式PFC设计来提高效率和待机功耗?

keil5提高效率的技巧

卡套管的使用有助于提高效率并达到更合格的标准

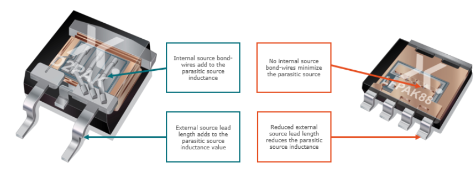

LFPAK88是提高效率的捷径

NIKKEI逻辑整合Brocade SAN以提高效率和安全性

提高效率的DC电源模块设计技巧

使用SiC器件在牵引应用中提高效率

使用SiC器件在牵引应用中提高效率

评论