碳化硅 (SiC) 行业正在快速发展,为21世纪的众多应用提供高效且紧凑的电力电子解决方案。电动汽车( EV) 市场是一个关键应用,首先是特斯拉,现在其他公司在其动力传动系统逆变器中采用了 SiC。市场上销售的 600 至 1,700 V 的 SiC 器件范围已广为人知,并为传统的硅 (Si) 功率器件提供了一种快速开关、宽带隙的替代方案。

虽然包括开关速度和高温能力在内的技术优势现已广为人知,但成本仍然是一个争论点。PGC Consultancy 分析了 SiC 裸片成本,在本文和未来的文章中,他们将解释高成本背后的原因以及可以采取哪些措施来降低价格。他们还提供了关于到本世纪末电动汽车销售可能会主导汽车行业的成本的长期观点。

碳化硅的成本

根据 PGC 咨询公司的数据,2021 年 9 月,100-A 分立式 SiC MOSFET(650 V 和 1,200 V)的零售价几乎是等效 Si IGBT 价格的 3 倍。尽管 SiC 器件的占用率要低 3 到 4 倍加工晶片上的区域。

造成这种成本的原因有几个: 主要贡献者是 SiC 衬底,可以肯定的是,这种情况将持续一段时间。这是因为使用 Czochralski 工艺生产高质量的硅晶片,在该工艺中,从 1,500˚C 的熔融硅池中提取一米长的硅晶锭。生产 SiC 的升华过程需要大量能量才能达到 2,200˚C,而最终可用的晶锭长度不超过 25 毫米,并且生长时间非常长。其结果是与 Si 相比,SiC 晶片的成本增加了 30 到 50 倍。与 SiC 衬底成本相比,外延(在衬底表面上生长 SiC 器件的高质量层)和制造成本等其他成本较低。然而,

正如 PGC 咨询公司指出的那样,另一个需要考虑的事实是制造各个阶段的效率,我们在这里也进行了讨论。良率与从晶锭中取出的不可用晶片的数量以及外延和制造后不可用的管芯数量有关。制造后影响芯片良率的一个主要因素是材料的质量,其中包括导致器件无法制造的一系列缺陷以及影响可靠性的其他不太明显的缺陷。正如 PGC Consultancy 指出的那样,制造中的另一个问题是 MOSFET 栅极氧化物的可靠性。

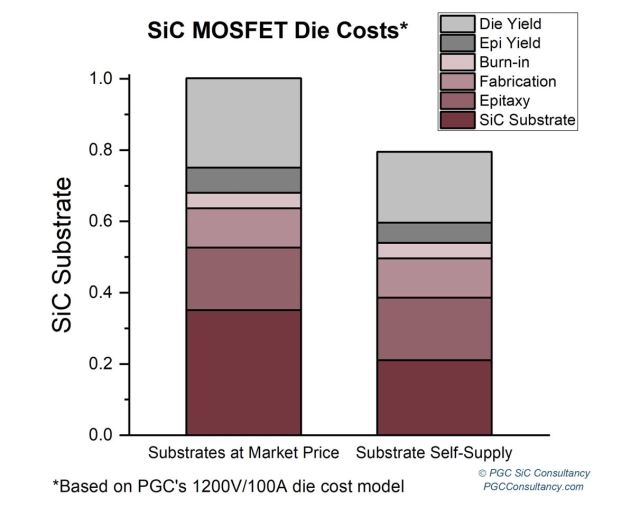

图 1:SiC MOSFET 裸片的成本细分,基于在 150 毫米基板上制造的同类最佳 2021 1,200-V/100-A 器件

图 1 显示了 SiC MOSFET 裸片的成本细分,产量来自于 2021 年同类最佳 1,200-V/100-A 商用器件,在 150-mm 衬底上生产。这两个堆栈近似于两种基板供应模式,将大多数以市场价格购买基板的公司与垂直整合的公司进行比较,因此可以以成本自供基板。所有其他费用都被认为是相等的。

折旧成本因公司而异,需要单独分析,但是,随着公司投资实现 200 毫米产能,这一比例将会增加。如果需要,设备的包装是应考虑的额外成本;然而,这个成本与基于硅的设备没有什么不同。

降低 SiC 成本

让我们看看 PGC Consultancy 详细介绍的未来十年成本降低的贡献者。如今,SiC 器件主要在 150 毫米直径的基板上开发。Wolfspeed 和 GT Advanced Technologies(在被 onsemi 收购之前)宣布了在 2022 年将尺寸升级到 200 毫米的提议。这将使单次制造运行中可以生产大约 1.8 倍以上的设备,从而降低制造成本。然而,PGC Consultancy 并不认为此次升级会显着降低芯片成本中的衬底部分。正如之前从 100 毫米到 150 毫米的过渡中所看到的,成本可能会与面积成正比,但随着技术的成熟和竞争的加剧,成本将稳步下降。

至少在开发的早期阶段,从 200 毫米晶圆上取出的芯片的成本可能比 150 毫米晶圆的成本略高,但是,晶圆良率、外延良率和芯片良率的优化将很快发生。经过短暂的发展,200毫米晶圆的缺陷密度可能会降低,制造成本也会降低;这可能会导致早期这些晶圆直径之间的锥形过渡。

如Wolfspeed的Mohawk Valley晶圆厂计划所示,200 mm晶圆的加工并不简单,需要高度自动化的专业工具。然而,从长远来看,这项投资将偿还成本,因为只要有可能,就让人们远离加工,降低成本,预计将对产量产生积极影响。最后,在基板方面,越来越多的公司希望在“垂直整合”的公司内自行供应基板,以了解这对成本的影响(见图1)。由于很少有芯片制造商能够完全自主供应,这给那些能够自主供应的制造商带来了竞争优势。

除基板外,PGC咨询公司认为,器件设计的进步在降低每一代SiC MOSFET的电阻和成本方面同样重要。欧姆定律规定,单位面积电阻的任何降低都会导致电流密度的增加。这意味着可以减少芯片面积,同时保持给定的额定电流。然而,从较小芯片中去除废热的问题意味着不能忽略热阻的变化,因此芯片面积与其电阻和热阻的平方根成比例。因此,电阻降低50%将导致芯片的有源区减少29%。较小的芯片尺寸不仅增加了每个晶片的生产数量,而且还提高了成品率。

PGC Consultancy 的 SiC 成本预测模型基于 2021 年同类最佳 1,200-V/100-A 器件,如图 2 所示。模型的三个输入如上图所示;基于这些假设的预计费用如下所示。所有数据都标准化为 2022 年 150 毫米芯片成本的已知值或估计值。最佳和最坏情况由上限和下限表示。在 2022 年和 2027 年,预计会出现两代(第 4 代和第 5 代),预计每代都会带来 45% 的阻力降低,最坏情况下降低到 40%,最好情况下降低到 50% 。 如前所述,由于面积根据电阻的平方根而减小,因此电阻减少 40% 到 50% 会导致有源器件面积减少 23% 到 29%。初始裸片尺寸基于同类最佳 1、200V/100A MOSFET(截至 2021 年 9 月)。显示的输出是 200-mm 和 150-mm 衬底的 1,200-V/100-A MOSFET 裸片的预期成本,显示了基本、最佳情况和最差情况。

图 2:PGC Consultancy SiC 成本预测模型,基于 2021 年同类最佳 1,200-V/100-A 器件。以上是模型中使用的三个输入;以下是预计的模具成本。所有数据都标准化为 2022 年已知或估计的 150 毫米值。上限和下限代表最佳/最坏情况。

根据这些假设,到 2030 年,在 200-mm 基板上制造的 1,200-V/100-A MOSFET 芯片的成本与今天基于 150-mm 基板的成本相比可能降低 54%。

总之,PGC Consultancy 的模型表明,改用 200 毫米基板不太可能立即降低芯片成本。然而,一旦推出 200mm 基板,基板质量的持续改进,加上器件设计的持续增量收益,将使 SiC 在未来变得更具成本竞争力。

审核编辑:郭婷

-

芯片

+关注

关注

454文章

50686浏览量

423011 -

半导体

+关注

关注

334文章

27252浏览量

217919 -

SiC

+关注

关注

29文章

2797浏览量

62587

发布评论请先 登录

相关推荐

中国AI企业创新降低成本打造竞争力模型

什么是SiC功率器件?它有哪些应用?

使用SiC技术应对能源基础设施的挑战

150度无压烧结银用于功率器件,提升效率降低成本

工业触摸显示屏在提升生产效率、降低成本等方面具有显著优势

全面的SiC功率器件行业概览

一文解析SiC功率器件互连技术

ZR机械手:提高生产效率,降低成本的有效途径-速程精密

SiC功率器件降低成本以推动采用

SiC功率器件降低成本以推动采用

评论