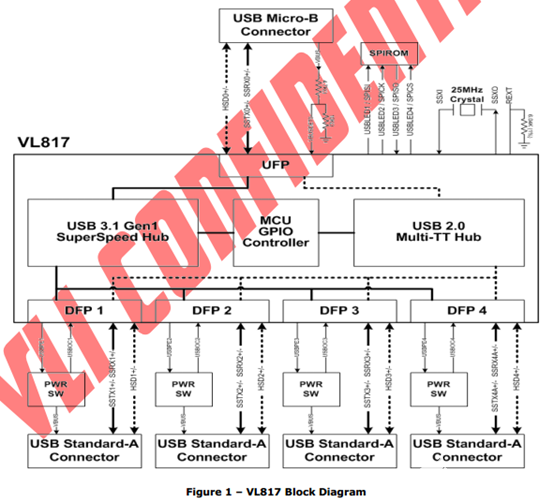

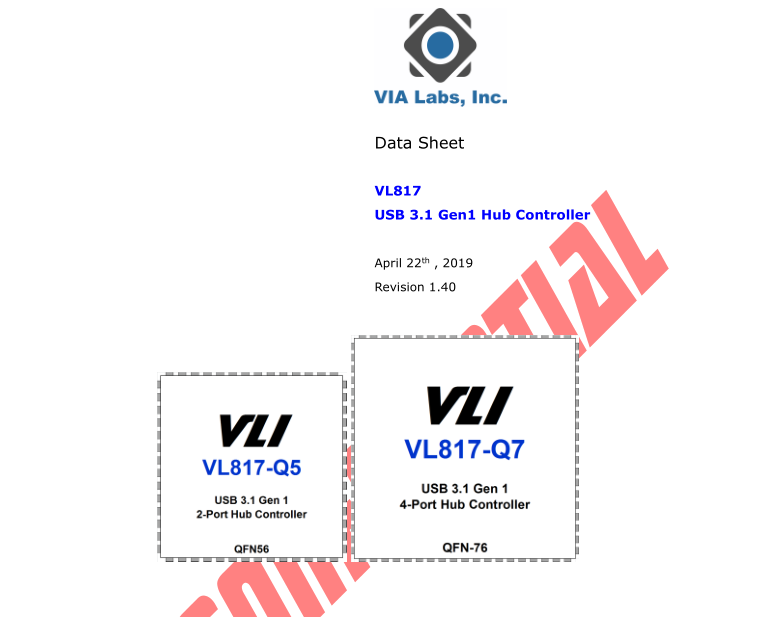

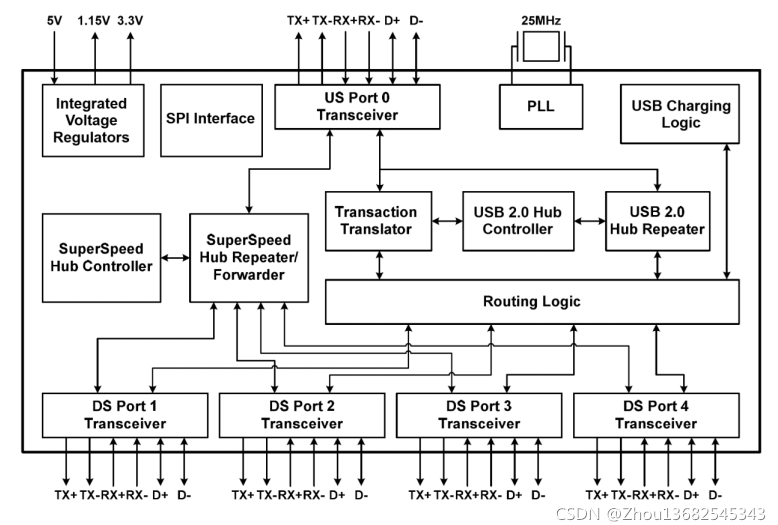

本文着重讲解市面上常见的USB3.0集线器驱动芯片威盛VL817-Q7C0的layout布局处理以及注意事项。可分为三小节。本文着重讲解第一小节:PCB布局的重点说明。

一:LATOUT 布局重点说明:

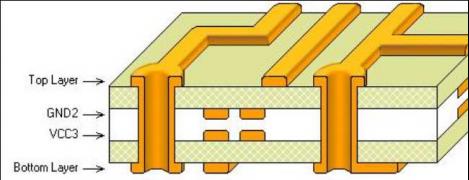

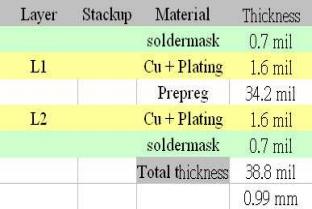

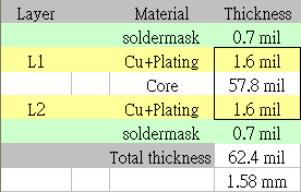

1:首先是PCB板线路的阻抗事宜,在此举例两层板阻抗注意事项,

<1>双层板:

USB:90Ω+/- 10 % W-S-W → 11-5-11 mils

SATA: 100Ω+/- 10 % W-S-W →6-5-6 mils

板厚:1.6mm

USB : 90 Ω +/- 10 % W-S-W = 12-5-12 mils

SATA: 100 Ω +/- 10 % W-S-W =7-5-7 mils

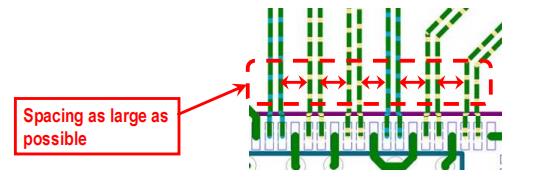

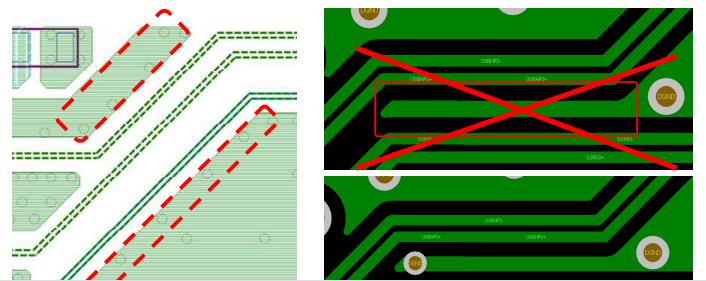

<2>,其次是线路的间距规格

所有阻抗线彼此的间距尽可能越大越好,理想值大于5倍的线宽(5W)

阻抗线与GND shape,VIA以及其他零件的间距应当大于宽(3w),可以的话4倍线宽以上更好。

其次是Diff pair走线时需要将GND铜箔空间也做出来

<3>.Vias on GND走线形状

靠近阻抗线的GND shape旁边应该有一连串GND vias,并且GND vias彼此之间的间距至少要少于200mils,且间距越小越好。

注:应避免先例有凸起,细长且末端没有GND via的GND shape。

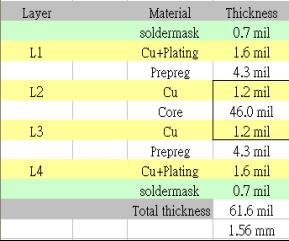

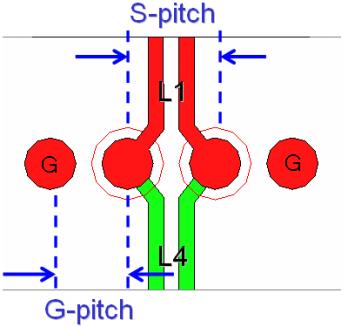

2:90ohm阻抗线的Via

Diff. Pair:W-S-W = 6-6-6 mils

Via spec.:drill = 12 mil,pad = 20 mil,antipad = 28 mil

Trace angle:45 degree

一般换层

S-pitch = 54 mil , G-pitch = 34 mil

错线

S-pitch = 55 mil , G-pitch = 30 mil

Minimum via to trace spacing V2T = 6 mil

Diff pari 走線設定

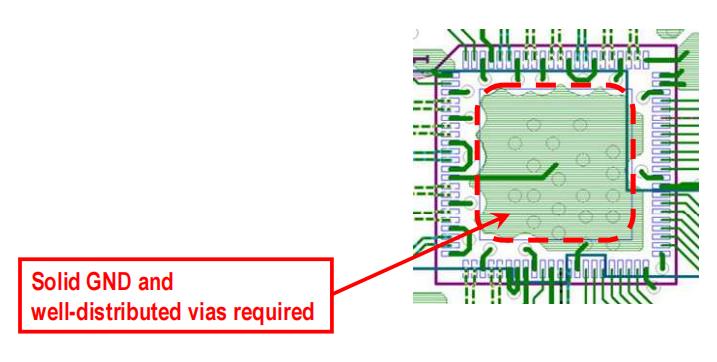

<1>Chip E-Pad

GND vias越多越好,且平均分佈(但是須注意power plane的完整性)

De-caps 的 GND via 最好在 E-PAD 上

注:GND铺铜请不要+字铺铜

4.:Power Plane

De-caps的拜访要越靠近chip越好

所有的电源最好用讴歌power plane的设计,且与其他层连接的via要越多越好。

电源部分的vias要比后端的要多,Power源头。

5.:USB3.0连接器

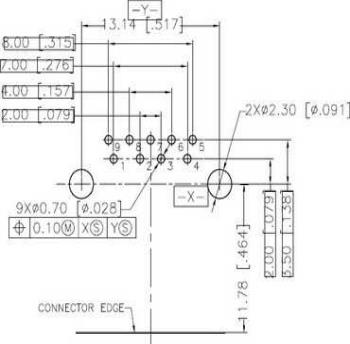

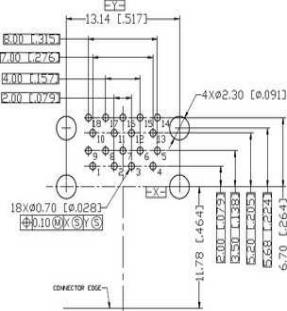

<1>USB 3.0 Std A, Stack A, and Std B Connectors

DIP Via for TX/RX pins:

Drill = 28 mil, Pad = 43 mil, Antipad (L2 and L3) = 80 mil

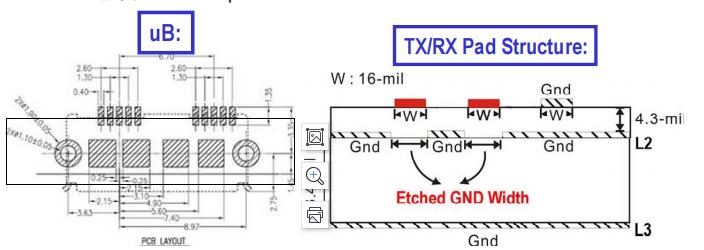

<2>Miceo usb

TX/RX pads:

Pad Width = 20 mil

Etched GND width on L2 = 23 mil

L3 应该 要是 GND shape

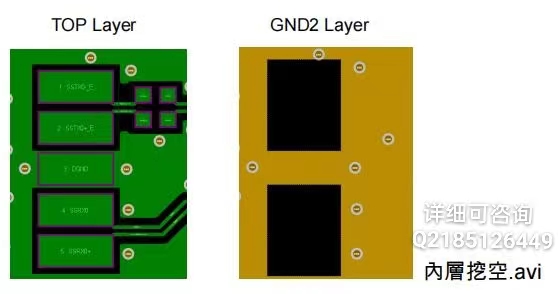

<3>SMD焊点

Pad Width = 50 mil

PAD picth=66.93mil

Etched GND width on L2 = 146.93 mil

L3 should still be GND

以上就是VL817的layout的布局说明,由于篇幅有限,文本有些细节并未仔细说明。

第二节的PCBLAYOUT的检查以及第三节VLI Chip layout的布局说明将于不久尽快整理并且发布。咨询第一小节详情可联系博主,共同谈论交流。

审核编辑:汤梓红

-

pcb

+关注

关注

4417文章

23967浏览量

426185 -

usb

+关注

关注

60文章

8476浏览量

285878 -

Layout

+关注

关注

15文章

424浏览量

75432

发布评论请先 登录

USB3.0:VL817Q7-C0的LAYOUT指南

USB3.0 HUB方案之VL813

USB3.0 HUB方案之VL817-Q7

基于VL813芯片的USB3.0 HUB方案

VL813 VL817 VL820是USB 3.0集线器芯片

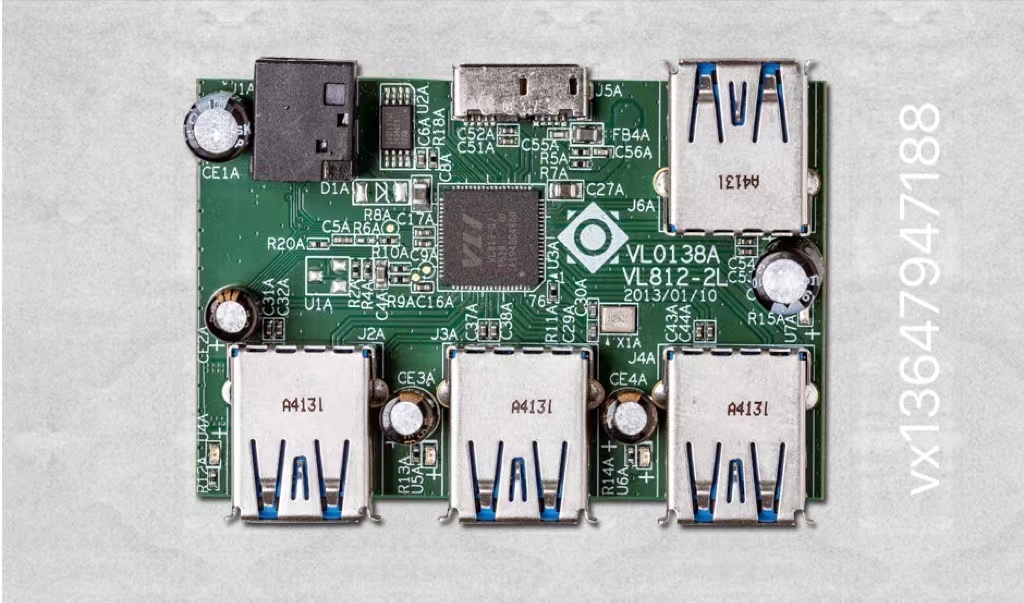

国产USB 3.0 HUB一扩四,可替换VL817/GL3510/RTS5411

国产首款USB3.0HUB芯片成功进入商用可兼容RTS5411、VL817、GL3510

USB3.0 HUB芯片《VL817-Q7S》威锋HUB芯片

USB3.0:VL817Q7-C0的LAYOUT指南(一)

USB3.0:VL817Q7-C0的LAYOUT指南(一)

评论