在很多Vivado的高速接口的IP中,比如Ethernet、PCIe、SRIO的设置中,都会有个Shared Logic的页面:

可能很多同学并没有很关注这个页面,直接默认设置就完事了。

但其实这个页面的内容也是非常有用的,我们可以看到页面中有两个选择:

- Include Shared Logic in core

- Include Shared logic in example design

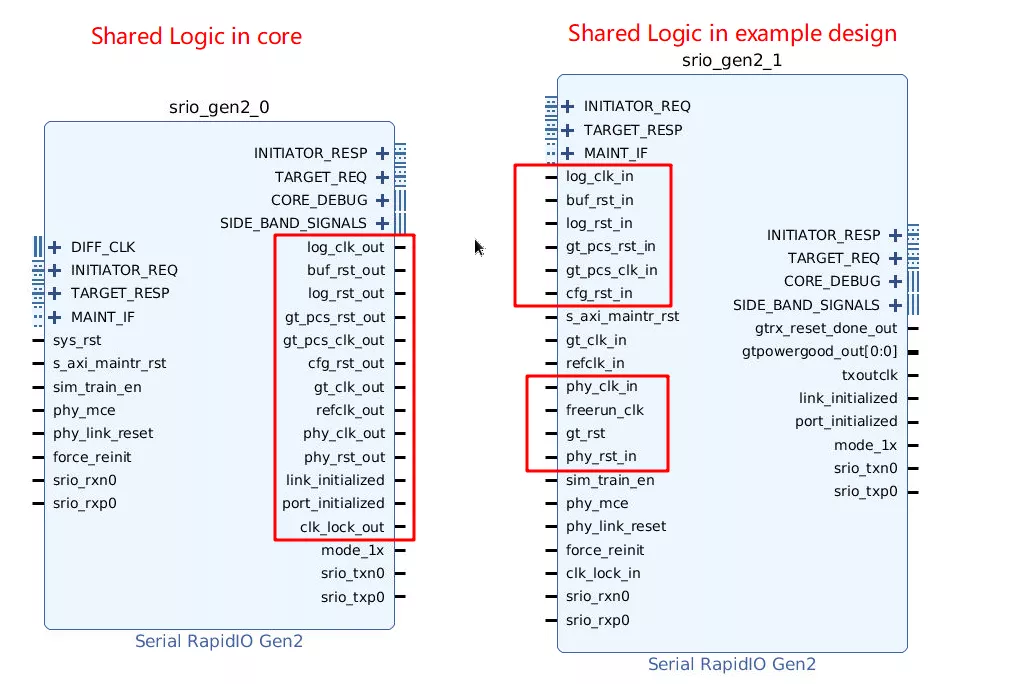

首先,什么是Shared Logic?字面意思很好理解,就是共享逻辑,主要包括时钟、复位等逻辑。当选择Shared Logic in core时,这些共享的逻辑就会被集成到IP的内部,也就是说这些逻辑是不能被修改的。当选择Shared Logic in example design时,这些共享逻辑就会出现在IP的接口上,我们可以根据自己的需求进行控制,那为什么叫in example design呢?因为Vivado的IP都会提供一个example,在shared logic在example中就相当于是这些逻辑是对外开放的。

我们以SRIO IP Core为例,下图显示了Shared Logic in core和Shared Logic in example design接口上的区别,可以看到,Shared Logic in core的输入接口是比较少的,因为这些时钟和复位的逻辑都被集成到了内部,但这些IP提供了这些逻辑的输出接口,我们在外面可以监测这些逻辑是否正确;Shared Logic in example design的输入接口明显要多一些,这些时钟、复位接口都需要我们自己提供,灵活性更强,当然我们可以直接参考example中的控制方式。

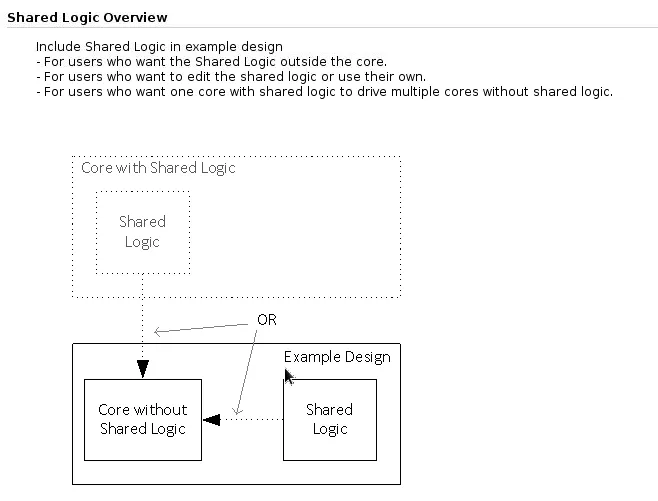

看懂上面这些,我们也就理解IP设置页面中下面这个图的含义了。

-

IP

+关注

关注

5文章

1738浏览量

150357 -

Logic

+关注

关注

1文章

97浏览量

46858 -

Vivado

+关注

关注

19文章

819浏览量

67219

发布评论请先 登录

相关推荐

在vivado中是否有像Logic Lock这样的功能

Northwest Logic支持Xilinx IP集成器工具流

Vivado IP中的Shared Logic到底是干嘛的

Vivado IP中的Shared Logic到底是干嘛的

评论