如今,BittWare的SmartNIC Shell的解析器组件是使用Xilinx HLS C++开发环境构建的。但BittWare的SmartNIC Shell的早期版本虽然使用Xilinx SDNet工具,但使用了P4语言。

使用P4的一个原因是,它是一种新兴的标准,受到在商品英特尔服务器上拥抱软件定义网络(SDN)的人们的欢迎。然而,Xilinx后来限制了SDNet的可用性。我们对P4的使用是专门针对SmartNIC Shell的终端用户的,所以这种限制使我们不得不寻找更开放的解决方案。在我们使用HLS成功实现RSS之后,我们被激励使用同样的HLS方法(特别是Xilinx HLS C++环境)重新实现SmartNIC Shell解析器。

什么是“Tuple”?

在网络中,tuple是指从网络数据包中提取的字段,并组合在一起。最常见的是“5-tuple”,它结合了源和目的IP地址、源和目的IP端口(如果IP协议有这些端口的话)以及IP协议号。

SmartNIC产品中的BittWare解析器会检查数据包,并在可用的情况下提取最多4个数据包。它将这些数据放入添加到数据包元数据的96位字段中。该字段宽度为IPv4源和目标地址以及源和目标端口提供了足够的位数。我们的解析器为数据包中不可用的字段提供零。如果一个数据包不包括任何IP有效载荷,那么完整的96位元组字段为零。

一个完整的5-tuple需要额外的8位来适应协议号。使用BittWare解析器的HLS用户只需稍加修改源代码就能轻松适应这一变化。

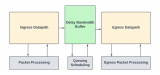

BittWare的RSS是一个可能在数据包流水线中跟随解析器并消耗96位元组数据的块的例子。在我们的应用笔记中阅读关于该块的内容,比较RTL和HLS C++。

在 BittWare 的 Loopback 示例中,Parser 的使用方式有所不同。Loopback 使用了 Parser 的三个副本,而不是扩展元数据的一个副本。之所以采取这种方法,是因为Parser实际上相当小。

在基本上创建了两个版本的数据包解析器后,我们注意到使用P4与HLS C++的一些差异。总的来说,HLS流的抽象性不如P4,但工具却远比P4成熟。

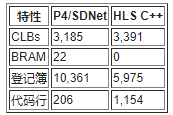

资源使用情况详见下表。

你可以看到,在所有的FPGA资源中,HLS不是相似就是更好。虽然源代码确实需要更多的行数,但其中一部分是受注释和格式的影响。然而,HLS的C++实现确实总是要比P4需要更多的代码行数。但这是针对数据包解析器/分类器而言的,属于 P4 所能描述的范围,而 HLS C++ 可以做得更多。HLS是非常通用的,几乎可以做任何事情。P4是非常专业的。

更妙的是,既然有了HLS的实现,那么后续修改它以消化以太网协议的变化就和用P4语言修改差不多了。这是因为我们的HLS C++实现的结构是对我们创建的低级解析函数的调用序列。这种方法类似于直接操作位于P4语言下的运行时。

如前所述,回环实例的源代码,包括它的解析器块,可以通过BittWare开发者网站免费提供给Ultrascale++的用户。它很好地说明了如何在HLS C++代码中使用AXI接口。想看但没有BittWare FPGA卡?请与我们联系,了解哪里可以购买。

什么是数据包解析器?

在以太网上使用的协议对硬件来说是一个挑战,要利用这些协议。这种挑战的存在是因为协议有许多可选字段。例如,这些选项使查找IP头的开始变得很复杂。 为什么这么说呢?在IP头的情况下,前面可以有零、一个或两个VLAN标签。 也可以有MPLS标签。因此硬件需要了解协议,刚好可以找到IP头。硬件需要IP头才能找到IP地址,而IP地址经常被用于硬件过滤器和表。类似的问题在下一级也存在,因为IP头本身有可选的字段。

BittWare的HLS C++包解析器可以处理。

0至2个VLAN标签(旧的SDNet代码允许0或1)。

0到5个MPLS标签(BittWare的旧SDNet代码不识别MPLS)。

IP碎片

IPv4头文件(不是IPv6

它假设在这些IP协议中找到端口ID。TCP、UDP、DCCP和STCP。

P4会不会成为FPGA硬件的通用?

P4语言是为了使用软件定义“包转发数据平面”(或网络交换机)而创建的。该语言尤其与硬件厂商Barefoot Networks有关。P4语言与谷歌帮助推广的名为“P4 Runtime”的东西不同。P4 Runtime提出了一个标准的运行时API,可以操纵由P4编译的解决方案的控制平面。

P4确实可以很容易的为一个新协议定义一个数据包分类器/解析器。P4还指定了一套完整的表查找功能,它可以重写流过的数据包,例如消除VLAN标签。

这是否意味着P4的灵活性将导致FPGA的采用?我们认为有几个理由反对这种情况发生。

在FPGA硬件上提供P4子集的商业选项是存在的,但是它们目前的范围有限。此外,如前所述,由于商业条款的限制,BittWare很难利用这些条款来创建一个我们可以随产品免费提供的示例程序。

需要注意的是,没有任何真实世界的FPGA应用可以完全用P4编写。例如,在一些例子中,跟随我们的解析器的接收端缩放(RSS)块不能用P4编写。然而,HLS C++可以用来编写任何一个块,甚至是结合两个功能的单个块。

另外,P4表查询函数基本上是用RTL或HLS C++编写的硬件专用运行库的封装器。程序员可以直接从HLS C++中调用这样的运行库,而不会受到任何惩罚。

最重要的是,在使用P4和HLS C++两种方法实现解析器后,我们实际上更倾向于HLS C++的方法。目前还不清楚FPGA上对P4的需求是否会增长到足以支持一个成熟的工具。HLS C++可以做得更多,也更成熟。

HLS的便携性和结论

我们希望对FPGA上的两个数据包解析器的实现进行解释,一个是用P4语言,另一个是用HLS C++,希望对你评估正确的方法有所帮助。

最后一点是关于我们FPGA卡之间的可移植性。在基于Xilinx FPGA的卡之间,HLS提供了一个简单的方法,几乎不需要任何改变。如果要移植到基于英特尔的卡上,比如我们的520N-MX,则需要修改源代码,特别是在兼容器的实用性方面。然而,基本概念是相同的。在这两种情况下,我们都是基于我们对FPGA翻译挑战的了解来构建C++。任意的C++代码在FPGA内运行效果会很差。然而,经过结构化并涂抹了实用程序的C++代码却能很好地运行。Xilinx或Intel所需要的改变非常相似,只是表达方式有些不同。

作为BittWare的SmartNIC Shell的一部分,我们的Parser可以帮助团队快速上手,在我们的FPGA卡上构建网络数据包处理应用。了解更多关于我们的卡的SmartNIC的信息,或与我们联系,讨论您的应用需求。

BittWare的Loopback例子重新部署了我们可以免费提供的SmartNIC shell的一个子集。这个子集包括我们的Parser库。

审核编辑:郭婷

-

Xilinx

+关注

关注

71文章

2173浏览量

122711 -

服务器

+关注

关注

12文章

9406浏览量

86435 -

C++

+关注

关注

22文章

2114浏览量

74102

发布评论请先 登录

相关推荐

I2C总线数据包结构详解

mtu配置步骤详解 mtu与数据包丢失的关系

华纳云:服务器平均响应时间和数据包大小之间的影响

esp8266怎么做才能每秒发送更多的数据包呢?

使用AT SAVETRANSLINK时UDP数据包丢失怎么解决?

在Iphone4上运行UDP接收器,数据包丢失怎么解决?

能否在ESP结束之前通过串行端口停止传入的UDP数据包的传输以解析下一个UDP数据包?

请问如何使用AT CIPSEND或AT CIPSENDBUF发送多个数据包?

NONOS如何检查是否实际发送了UDP数据包?

如何在AIROC GUI上获取良好数据包和总数据包?

请问高端网络芯片如何处理数据包呢?

构建BittWare的数据包解析器

构建BittWare的数据包解析器

评论