1. 为什么选择SRIO

随着PCIe接口、以太网接口的飞速发展,以及SOC芯片的层出不穷,芯片间的数据交互带宽大大提升并且正在向片内交互转变;SRIO接口的应用市场在缩小,但是由于DSP和PowerPC中集成了SRIO接口,因此在使用DSP/Power PC + FPGA的使用场景中仍然占有一席之地。

同时,由于SRIO接口一些独特的特性,使得SRIO接口在一些应用中仍然不可替代:

A. 不同的数据包类型,支持使用SRIO传输不同的数据类型;

B. 支持数据包优先级;

C. 支持响应机制;

D. 支持重传机制;

E. 支持带目的地址的路由;

F. 方便研发工程师定义灵活的硬件结构和变化的负荷分担;

2. XilinxSRIO IP特性

Xilinx SRIO IO具有如下特性:

A. 支持RapidIO互连Rev2.2协议;

B. 支持1x、2x、4x,并且可以从x4、x2向下train down;

C. 每条lane支持的线速率为1.25Gbs、2.5Gbs、3.125Gbs、5.0Gbs和6.25Gbs;

D. 支持同时发生的Initiator和Target接口操作;

E. 支持Doorbell传输和Message传输;

F. 专有的Maintenance传输端口;

G. 使用标准的AXI4-Lite和AXI4-Stream接口实现简单的握手机制和数据流控制;

H. 所有发送数据包支持source ID可配置;

I. 针对复杂的互连系统,支持16bit device ID配置;

J. TXbuffer和RX buffer深度独立可配置,可配置深度分别为8包、16包和32包;

K. 支持TX flow control和RX flow control;

L. 支持multi-cast传输;

3. Xilinx SRIO IP架构

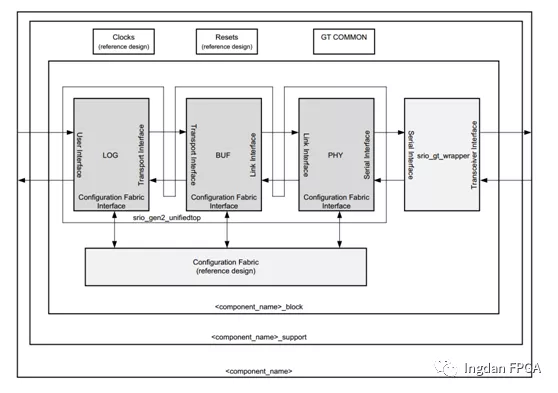

Xilinx SRIO IP包含LOG(逻辑和传输层)、BUF(传输层)、PHY(物理层)、Clock&Reset四个组成部分,其中:

A. 逻辑和传输层定义了操作协议,包含数据组包和解包,提供用户逻辑接口、传输接口和配置接口;

B. 传输层定义了包交换、路由和寻址机制,包含发送和接收数据缓存、数据包传输和流控、优先级控制和数据包排序、跨时钟域处理和重传管理;

C. 物理层定义了电气特性、链路控制和纠错重传等,包含链路训练、初始化和协议实现、CRC和响应机制、提供和Transceiver的接口;

D. Clock&Reset部分实现SRIO时钟、复位、寄存器管理(Clock、Reset、Register Manager):该部分实现SRIO接口时钟方案、复位策略及寄存器配置和管理功能;

Xilinx SRIO IP核的结构如下图所示:

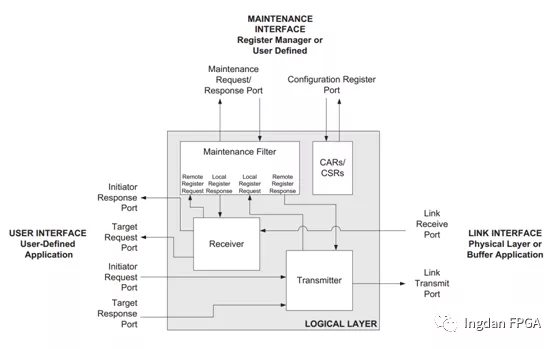

其中,逻辑层提供给用户的接口包括Initiator Request接口、Initiator Response接口、TargetRequest接口、Target Response接口、Maintenance Request接口、Maintenance Response接口和配置寄存器接口。如下图所示:

由于在SRIO IP版本升级的过程中,在Gen2 IP中引入了AXI接口,因此Xilinx SRIO IP LOG层提供给用户的接口也发生了变化。

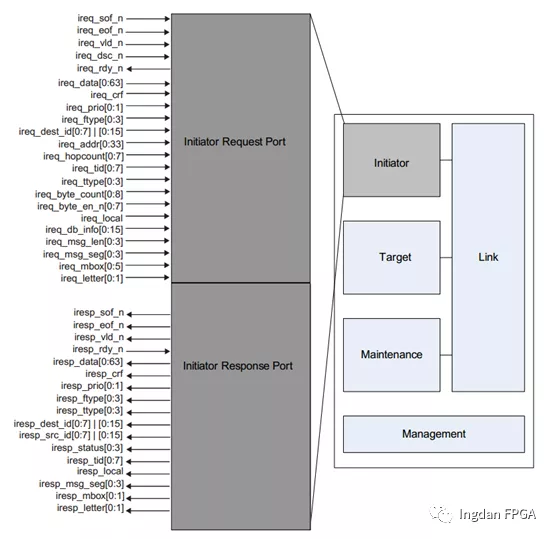

以Initiator接口为例,Xilinx SRIO IP Gen1 V5.6以前的版本提供给用户的接口信号如下图所示,Target和Maintenance接口提供给用户的接口也和Initiator接口基本类似。

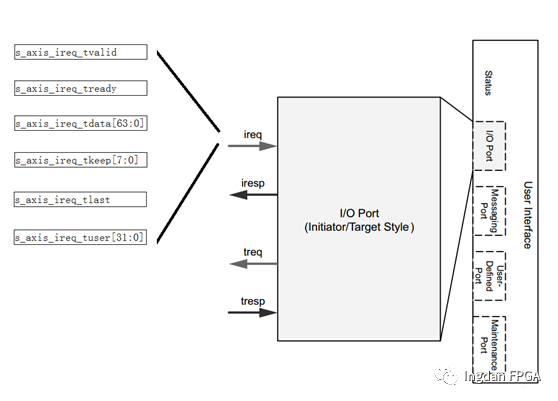

以Initiator接口为例,Xilinx SRIO IP Gen2 V1.0以后的版本提供给用户的接口信号如下图所示,变更为AXI接口,Target和Maintenance接口提供给用户的接口也和Initiator接口基本类似。

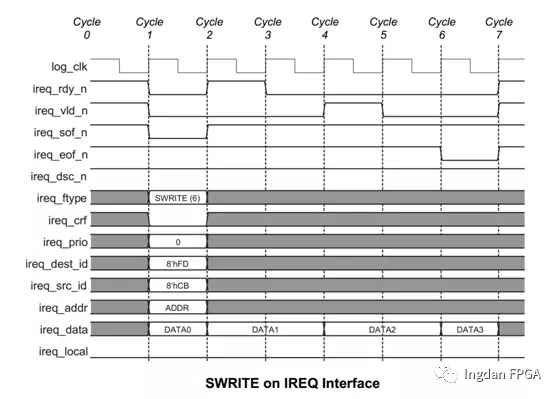

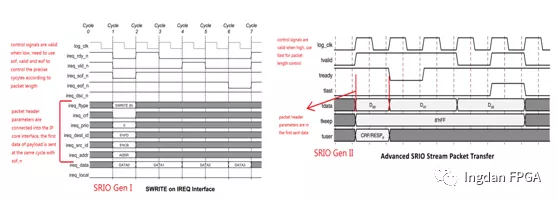

以Initiator接口为例,Xilinx SRIO IP Gen1 V5.6以前的版本提供给用户的接口时序如下图所示:

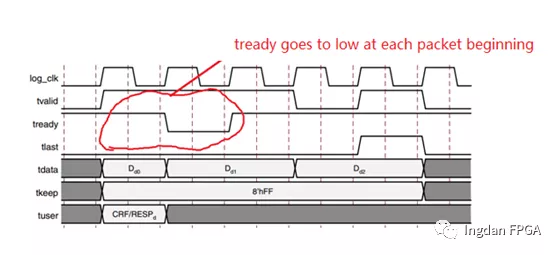

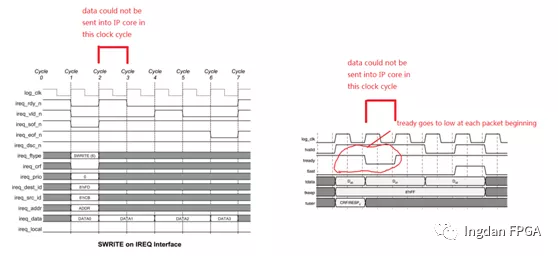

以Initiator接口为例,Xilinx SRIO IP Gen2 V1.0以后的版本提供给用户的接口时序如下图所示,这里发生了一个显著的变化是在每一包数据发送时tready会先变低一个周期,因此此处的时序要控制好,不然很容易造成SRIO IP核堵塞。

4. SRIO数据包格式

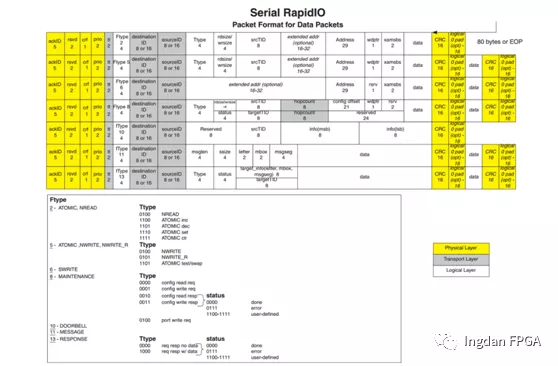

在SRIO数据包格式中,主要分为包头、数据payload、包尾三部分。包头的ackID、crf、prio、ftype、ttype、source ID、destination ID、address等信息需要用户根据数据包的类型、优先级、源地址、目的地址、读写操作地址等信息填入;data部分是我们需要操作当前数据包的payload;包尾的CRC等信息为IP核自动插入。

5. XilinxSRIO IP使用和调试中的注意事项

Xilinx SRIO IP在使用和调试的时候,我们强调如下注意事项:

A. LOG接口的时序控制必须精准,否则可能会造成SRIO IP核堵塞;以IREQ接口为例说明:

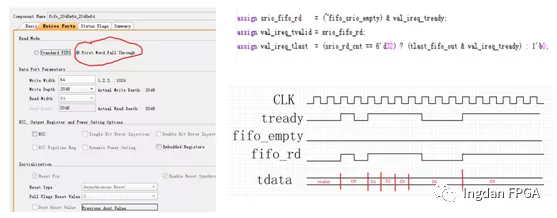

B. LOG接口使用组合逻辑来控制时序,在实际上板测试过程中要考虑tready信号 随时可能变无效的情况,通常我用一个不使能任何输出寄存器的FIFO来做组合逻辑时序控制,在Gen2 IP使用时我的一个例子如下图所示;

C. Gen1 IP和Gen2 IP的差别在于:Gen1的控制信号为低有效,Gen2的控制信号为高有效;Gen1使用sof、eof、valid来控制有效数据进入IP核,Gen2使用tvalid和tlast来控制有效数据进入IP核;Gen1的包头信息是独立的接口,sof对应的就是第一个payload数据,Gen2的包头信息是作为数据写入tdata接口;

D. 非法的数据包会造成SRIO IP核堵塞,比如数据长度和包头里的size不匹配,比如没有tlast信号等;

E. 如果一个数据包payload不足2N,经过SRIO IP核后会自动补充到2N,例如我们发送一个payload为48byte的包,到达接收端的将会是一个64byte的数据包;

F. 如果device ID错误,数据包将会被过滤;

G. 在FPGA和对端器件调试SRIO的时候,DSP和Power PC的SRIO通常也支持不同的几种环回模式,遇到链路不通的问题可以借助这些环回模式来进行定位;

H. 如果系统中接的有SRIO Switch芯片,一般IIC接口和SRIO接口的Maintenance包都可以用于配置Switch芯片;

审核编辑:汤梓红

-

Xilinx

+关注

关注

71文章

2172浏览量

122344 -

IP

+关注

关注

5文章

1724浏览量

150093 -

sRIO

+关注

关注

1文章

31浏览量

21088

发布评论请先 登录

相关推荐

FPGA优质开源模块-SRIO IP核的使用

srio_v5_6 IP核使用发生错误

Xilinx CORE生成器IP列表名称及说明详解

Xilinx FIR IP的介绍及仿真

在Vivado中使用SRIO高速串行协议的IP演示官方例程

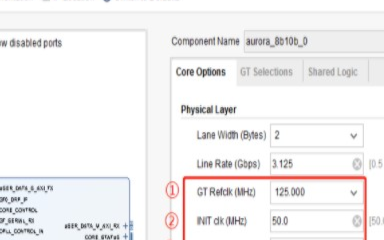

Xilinx平台Aurora IP介绍(二)时钟与复位

Xilinx FFT IP介绍与仿真测试

SRIO IP核的三层协议的作用解析

Xilinx Vivado DDS IP使用方法

基于FPGA的SRIO协议设计

srio交换芯片是什么?srio交换芯片的原理和作用

SRIO介绍及xilinx的vivado 2017.4中生成srio例程代码解释

Xilinx SRIO IP介绍和使用经验分享

Xilinx SRIO IP介绍和使用经验分享

评论