Alveo系列开发板上的平台其实是一个DFX设计的静态部分,在Vitis 统一软件平台中使用Alveo系列开发板设计加速Kernel, 最终这些Kernel的逻辑会在分布在DFX设计的动态区域。

本篇将介绍如何为Kernel的逻辑做floorplan(画Pblock),人为控制Kernel逻辑的布局。

我们以经典Example design“Vector Addition” 为例:

1. 打开Vitis 2020.2,创建新的 Application Project

File -> New -> Application project

2. 选择xilinx_u200_qdma_201910_1平台 (本篇讨论的方法不局限于某个具体平台)

3. 选择打开Example Design "Vector Addition"

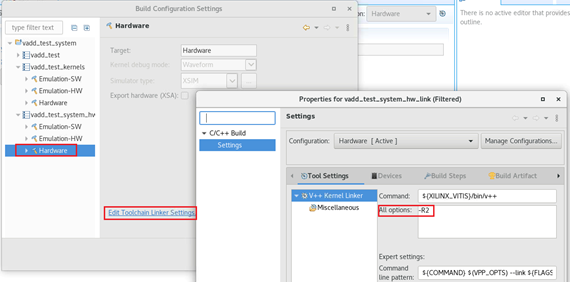

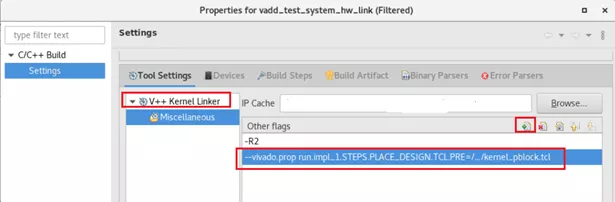

4. 对Hardware Flow 在Link阶段设置 "-R2",然后Build

此处report level 选择-R2:VPL(Vitis Platform link) 过程输出更多中间文件, 后续我们会用到画Kernel Pblock所需要的opt.dcp

5. 不用等到生成xclbin文件,VPL完成opt_design步骤之后我们就能看到XX_opt.dcp 文件.

XX_opt .dcp 所在目录及文件名:

vitis_pblock_u200/vadd_test_system_hw_link/Hardware/binary_container_1.build/link/vivado/vpl/prj/prj.runs/impl_1 pfm_top_wrapper_opt.dcp

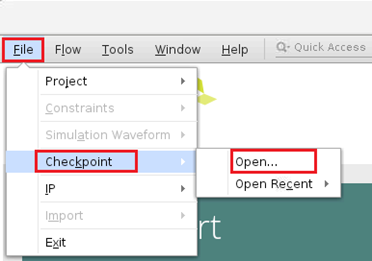

6. 把这个XX_opt.dcp拷贝到另外的目录,并用Vivado打开这个dcp 文件

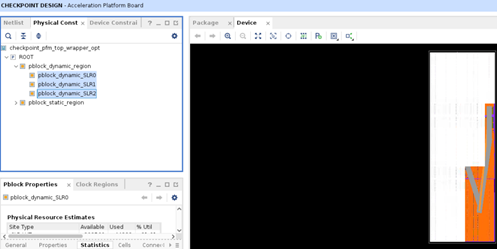

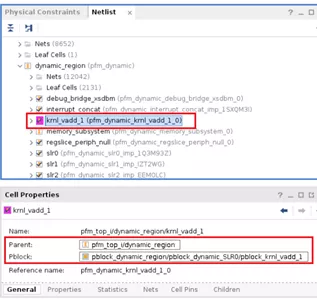

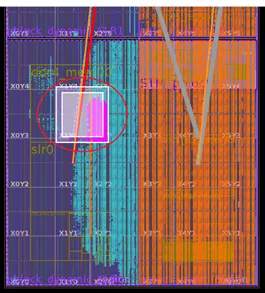

7. 查看已有的Pblock。主菜单 Window -> Physical Constraints

在这个视图可以看到平台已经为动态区域在各个SLR中设置了相应的Pblock, 而且需要注意的是,设计中已有的Pblock是有层级关系的

例如:pblock_dynamic_region 包含三个下级pblock:

pblock_dynamic_SLR0,

pblock_dynamic_SLR1,

pblock_dynamic_SLR2,

提醒:不同平台SLR的数目也可能是不同的. 不同平台中自带pblock的名字有差异是正常的. 需要用户自己观察.

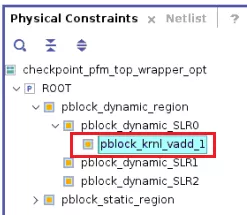

为Kernel模块生成的Pblock应该是pblock_dynamic_SLR0 这一级Pblock 的子模块, 工具支持把同一个Kernel的不同部分放置到多个SLR中,用户需要保证跨SLR路径的时序.

8. 为Kernel模块画Pblock

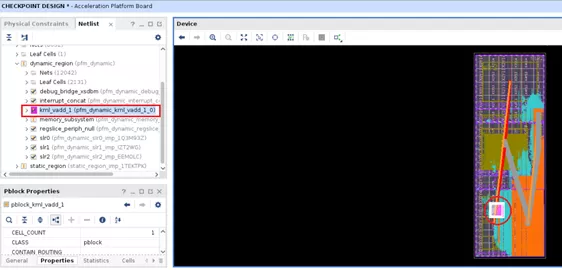

在这里尝试把Kernel 放置在pblock_dynamic_SLR0所属的中心区域

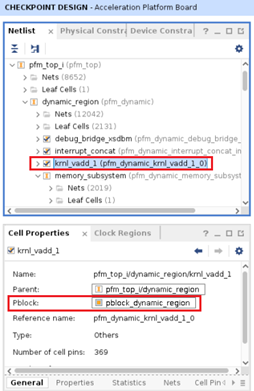

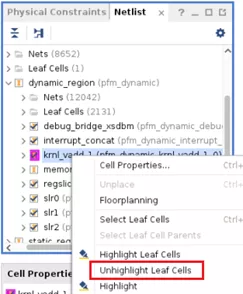

. 在Vivado的Netlist View中选中Kernel 模块

例子中的模块名是 pfm_top_i/dynamic_region/krnl_vadd_1

. 可以在Cells properties 窗口看到这个模块当前所属的Pblock是pblock_dynamic_region

. 点击Device 视图中的"Draw Pblock" 按钮, 在Device视图上原有pblock_dynamic_SLR0的范围内画一个方框,新画的Pblock所覆盖面积要被原Pblock完全包含. 画完之后还可以选中Pblock微调Pblock的边界,同时为了不影响原来Pblock的结构,在TCL CONSOLE中用以下命令把新Pblock的Parent Pblock设置成pblock_dynamic_SLR0:

set_property PARENT pblock_dynamic_SLR0 [get_pblocks pblock_krnl_vadd_1]

. 再看Kernel 模块的Pblock属性,已经变为pblock_krnl_vadd_1

在TCL CONSOLE中会打印出了画pblock相应的约束,我们可以将这些约束拷贝到一个新的tcl文件中保存.

(在这里保存到kernel_pblock.tcl)

看下更新的Pblock结构,新生成的pblock_krnl_vadd_1 是pblock_dynamic_SLR0的Child Pblock

继续在TCL CONSOLE执行 place_design 命令完成布局

理论上这一步可以跳过,如果你确信你画的Pblock没有问题的话。

完成place_design之后,可以观察一下Kernel 的资源在Device 上的实际分布情况

可以看到Kernel的逻辑全部都分布在刚才所画的Pblock 区域内

9. 在Vitis的link阶段做以下设置,使之前保存的画Pblock的命令在VPL(Vitis Platform link) 的place_design步骤执行之前生效

--vivado.prop run.impl_1.STEPS.PLACE_DESIGN.TCL.PRE=XX/kernel_pblock.tcl

10. 重新build Vitis 的Hardware flow, 之前加入的命令就会生效。

总结: 这就是一个简单的为Kernel逻辑创建面积约束(Pblock)的过程, 实际用户也可以为Kernel的子模块创建Pblock,这方面工具没有限制。

审核编辑:刘清

-

开发板

+关注

关注

25文章

5144浏览量

98436 -

Kernel

+关注

关注

0文章

48浏览量

11269

发布评论请先 登录

相关推荐

使用AMD Vitis进行嵌入式设计开发用户指南

时序约束一主时钟与生成时钟

AMD Vitis Unified Software Platform 2024.2发布

如何在TMS320C6727 DSP上创建基于延迟的音频效果

如何在Draftsman中创建PCB制造图纸

如何在引脚映射器文件中添加TC322?

linux kernel通过修改链接脚本lds文件,如何在esp32的linker.lf文件中实现?

在Windows 10上创建并运行AMD Vitis™视觉库示例

Xilinx FPGA的约束设置基础

如何在Vitis加速设计中为Kernel创建面积约束

如何在Vitis加速设计中为Kernel创建面积约束

评论