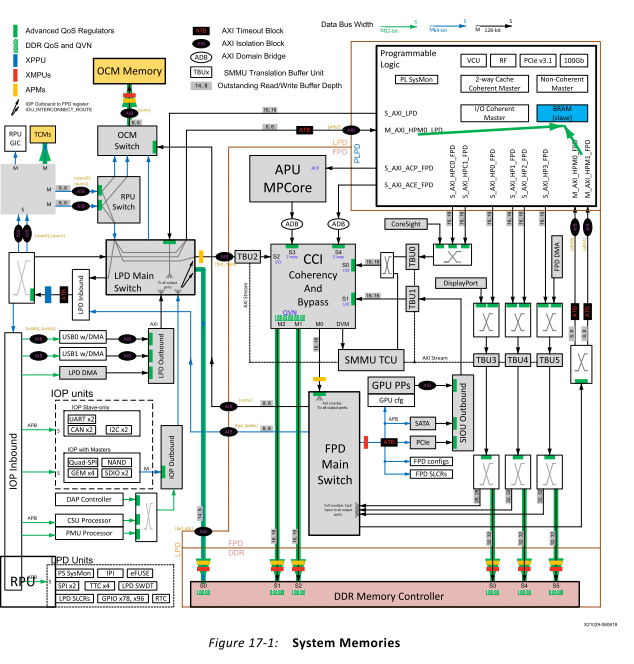

MPSoC的DDR控制器的数据通道上集成了 AXI performance monitors (APM)。具体情况,可以参考Xilinx UG1085 (v2.2)中Chapter 15的“Figure 15‐1: PS Interconnect”或者Figure 17-1。

1. APM驱动程序

对于AXI performance monitors (APM),xilinx提供的驱动程序是drivers\uio\uio_xilinx_apm.c,相关匹配字符串和主要数据结构如下:

static const struct of_device_id xapm_of_match[] = { { .compatible = "xlnx,axi-perf-monitor", }, { /* end of table*/ } }; MODULE_DEVICE_TABLE(of, xapm_of_match); static struct platform_driver xapm_driver = { .driver = { .name = "xilinx-axipmon", .of_match_table = xapm_of_match, .pm = &xapm_dev_pm_ops, }, .probe = xapm_probe, .remove = xapm_remove, };

APM驱动程序最终会注册UIO设备。

在每个单板的device tree里,会支持DDR的APM。比如,在VCU TRD里,为DDR的APM定义了下面字段。

perf-monitor@fd0b0000 {

compatible = "xlnx,axi-perf-monitor";

reg = <0x00 0xfd0b0000 0x00 0x10000> ;

interrupts = <0x00 0x7b 0x04> ;

interrupt-parent = <0x04> ;

xlnx,enable-profile = <0x00> ;

xlnx,enable-trace = <0x00> ;

xlnx,num-monitor-slots = <0x06> ;

xlnx,enable-event-count = <0x01> ;

xlnx,enable-event-log = <0x00> ;

xlnx,have-sampled-metric-cnt = <0x01> ;

xlnx,num-of-counters = <0x0a> ;

xlnx,metric-count-width = <0x20> ;

xlnx,metrics-sample-count-width = <0x20> ;

xlnx,global-count-width = <0x20> ;

xlnx,metric-count-scale = <0x01> ;

clocks = <0x03 0x1c> ;

phandle = <0x9b> ;

};

perf_monitor_ddr = "/amba/perf-monitor@fd0b0000";

OCM、CCI等模块也有APM。

perf_monitor_ocm = "/amba/perf-monitor@ffa00000";

perf_monitor_cci = "/amba/perf-monitor@fd490000";

perf_monitor_lpd = "/amba/perf-monitor@ffa10000";

单板Linux启动后,能查询到对应的UIO设备。

root@vcu_trd:~# ls /dev/uio* /dev/uio0 /dev/uio1 /dev/uio2 /dev/uio3 /dev/uio4

2. APM用户态程序

对于AXI performance monitors (APM),xilinx也提供了用户态程序,是apm_main.elf。使用apm_main.elf,可以查询APM监视到的DDR带宽利用情况。

root@vcu_trd:~# chmod +x apm_main.elf root@vcu_trd:~# ./apm_main.elf -d /dev/uio0 AXI PMON is in Advanced Mode port 1 read: 0 0.00 MBps port 1 write: 0 0.00 MBps port 2 read: 0 0.00 MBps port 2 write: 0 0.00 MBps port 4 read: 0 0.00 MBps port 4 write: 0 0.00 MBps port 5 read: 0 0.00 MBps port 5 write: 0 0.00 MBps root@vcu_trd:~# root@vcu_trd:~# ./apm_main.elf -d /dev/uio1 AXI PMON is in Advanced Mode port 1 read: 12523440 12.52 MBps port 1 write: 7564856 7.56 MBps port 2 read: 13290992 13.29 MBps port 2 write: 7493209 7.49 MBps port 4 read: 0 0.00 MBps port 4 write: 331253760 331.25 MBps port 5 read: 667254864 667.25 MBps port 5 write: 320656878 320.66 MBps root@vcu_trd:~# ./apm_main.elf -d /dev/uio2 AXI PMON is in Advanced Mode port 1 read: 0 0.00 MBps port 1 write: 0 0.00 MBps port 2 read: 0 0.00 MBps port 2 write: 0 0.00 MBps port 4 read: 0 0.00 MBps port 4 write: 0 0.00 MBps port 5 read: 0 0.00 MBps port 5 write: 0 0.00 MBps root@vcu_trd:~# ./apm_main.elf -d /dev/uio3 AXI PMON is in Advanced Mode port 1 read: 0 0.00 MBps port 1 write: 0 0.00 MBps port 2 read: 0 0.00 MBps port 2 write: 0 0.00 MBps port 4 read: 0 0.00 MBps port 4 write: 0 0.00 MBps port 5 read: 0 0.00 MBps port 5 write: 0 0.00 MBps

上述设备“/dev/uio1”代表DDR APM1。在使用VCU TRD进行1080p编码时,port 4写带宽331.25 MBps,port 5读带宽667.25 MBps,port 5写带宽320.66 MBps。每个DDR port对应的硬件模块,请参考ug1085的Figure 17-1。port 4连接到了HP 1/HP 2。port 5连接到了HP 3。

-

APM

+关注

关注

1文章

74浏览量

13985 -

MPSoC

+关注

关注

0文章

203浏览量

25238 -

AXI

+关注

关注

1文章

145浏览量

18039

发布评论请先 登录

使用AXI4接口IP核进行DDR读写测试

使用AXI-Full接口的IP进行DDR的读写测试

使用AXI performance monitors(APM)测试MPSoC DDR访问带宽

使用AXI performance monitors(APM)测试MPSoC DDR访问带宽

评论