今日,OpenCAPI 和 CXL 将发布联合公告,表示这两个集团将联手,OpenCAPI 标准和财团的资产将转移到 CXL 财团。通过这种集成,CXL 将成为主导的 CPU 到设备互连标准,因为几乎所有主要制造商现在都支持该标准,而竞争标准已经退出竞争并被 CXL 吸收。

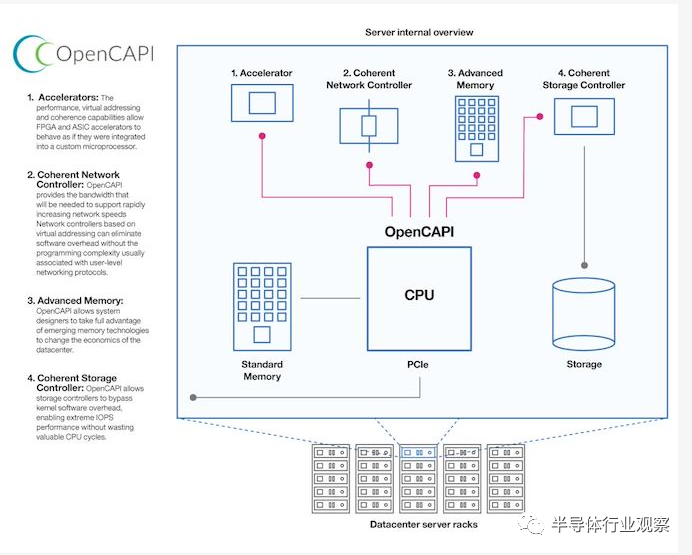

比CXL 面世还早的OpenCAPI 是缓存一致 CPU 互连的早期标准之一。该标准由 AMD、Xilinx 和 IBM 等公司提供支持,是 IBM 现有的相干加速器处理器接口 (Coherent Accelerator Processor Interface :CAPI) 技术的扩展,向业界其他公司开放,并将其控制在行业联盟之下。在过去六年中,OpenCAPI 的使用量不大,最引人注目的是在 IBM 的 POWER9 处理器系列中实现。与类似的 CPU 到设备互连标准一样,OpenCAPI 本质上是现有高速 I/O 标准之上的应用程序扩展,添加了缓存一致性和更快(更低延迟)访问模式等内容,以便 CPU 和加速器可以更多地协同工作尽管它们的物理分解很紧密。

但是,作为解决这个问题的几个竞争标准之一,OpenCAPI 从未在业界引起轰动。作为一个诞生于IBM 的标准,在推进过程中,IBM 在服务器领域的份额一直在下降,但IBM 扔起是其最大的用户。甚至像 AMD 这样的新兴联盟成员也最终跳过了这项技术,例如利用他们自己的 Infinity Fabric 架构来实现 AMD 服务器 CPU/GPU 连接。这使得 OpenCAPI 没有强大的拥护者——也没有庞大的用户群来推动事情的发展。

最终,为了制造商和客户的利益,更广泛的行业希望在单一互连标准背后进行整合,这将互连战争推向了高潮。随着 Compute Express Link (CXL) 迅速成为明显的赢家,OpenCAPI 联盟退出并被 CXL 吸收。

根据拟议交易的条款——等待必要方的批准——OpenCAPI 联盟的资产和标准将转移给 CXL 联盟。这将包括来自 OpenCAPI 的所有相关技术,以及该组织鲜为人知的开放内存接口 (OMI) 标准,该标准允许通过 OpenCAPI 的物理总线将 DRAM 连接到系统。本质上,CXL 联盟将吸收 OpenCAPI;虽然出于显而易见的原因他们不会继续开发,但转移意味着 OpenCAPI 的任何有用技术都可以集成到 CXL 的未来版本中,从而加强整个生态系统。

随着 OpenCAPI 兼并到 CXL,这使得英特尔支持的标准成为主导的互连标准——以及行业未来的事实标准。竞争的Gen-Z 标准在今年早些时候同样被 CXL 吸收,而 CCIX 标准已被抛在后面,其主要支持者近年来加入了 CXL 联盟。因此,即使第一批支持 CXL 的 CPU 还没有发货,在这一点上,CXL 已经清除了障碍,可以说,成为从加速器 I/O (CXL.io) 到内存扩展的所有方面的唯一剩余服务器 CPU 互连标准通过 PCIe 总线。

在发布新闻稿中,双方表示,计算行业正在经历重大变革。特定于应用程序的硬件加速正变得司空见惯,新的内存技术正在影响计算的经济性。为了满足对开放架构的需求,以允许全行业参与,OpenCAPI 联盟 (OCC) 成立于 2016 年。定义的架构允许任何微处理器连接到一致的用户级加速器、高级存储器,并且与处理器架构。2021 年,OCC 宣布了开放内存接口 (OMI)。OMI 是基于 OpenCAPI 的串行连接近存储器接口,可为主存储器提供低延迟和高带宽连接。

2019 年,Compute Express Link (CXL) 联盟成立,旨在为处理器、内存扩展和加速器提供行业支持的高速缓存一致性互连。2020 年,CXL 和 Gen-Z 联盟宣布了在各自技术之间实施互操作性的计划,并在 2022 年初,Gen-Z 将其规范和资产转让给了 CXL 联盟。

秉承这一精神,OpenCAPI 宣布,OCC和CXL正在达成协议,如果各方批准并同意,将把 OpenCAPI 和 OMI 规范以及 OpenCAPI 联盟资产转让给 CXL 联盟。

“我们很高兴看到业界围绕一个推动开放式创新并利用 OpenCAPI 和开放式内存接口提供一致互连和低延迟、接近内存接口的价值的组织聚集在一起。我们预计这将为行业带来最佳的业务成果,因为一个整体和财团的成员。”OpenCAPI 联盟主席Bob Szabo指出。

“我们很高兴有机会将行业重点放在一个组织下的规范上。这是我们共同成员共同努力推进标准高速相干互连/结构以造福行业的正确时机。 OCC 资产的分配将允许 CXL 联盟自由使用 OCC 已经通过 OpenCAPI/OMI 开发的内容。”CXL 联盟主席 Siamak Tavallaei补充说。

前情提要:CXL 吸收 GEN-Z

在2021年11月,CXL 宣布,将吸收GEN-Z标准共同发展。

在 IT 行业中,相互竞争的团体为了共同利益和各地系统的改进而共同努力,这是一个司空见惯的事情,CXL 联盟吸收了 Gen-Z 联盟也是如此。

资料显示,制造商 AMD、架构设计公司ARM、两家服务器供应商戴尔和 HPE、内存制造商美光和 FPGA 专家赛灵思自 2016 年以来一直在开发 Gen-Z,以便通过协议处理器、PCI- Express 内存和加速器进行通信。

然而,Gen-Z 联盟缺少两个重要的名字:英特尔和英伟达。虽然英伟达最终在 2020 年 8 月加入该联盟。但英特尔推出了相互竞争的互连 Compute Express Link (CXL),改联盟的支持者有阿里巴巴、思科、戴尔 EMC、Facebook、谷歌、HPE、华为和微软。

当 AMD、ARM、IBM、Nvidia 和 Xilinx 于 2019 年夏末加入Gen-Z联盟时,我们能明显察觉到它们将面临困难时期。两个财团随后相互合作——但自 2020 年 5 月以来没有发布任何新闻稿,Gen-Z也沉默了。现在,Gen-Z 想要完全停止自己的开发,将这个领域留给 CXL。

从CXL支持者提供的消息可以看到,GenZ的做法是希望将所有规格和资产转移到CXL联盟,但这仍需要各方的同意。值得一提的是,在CXL吸收Gen-Z的时候,行业内仍有 CCIX 和 OpenCAPI与之竞争,但行业正在朝着 CXL 方向发展。现在吸收了OpenCAPI之后,只剩下CCIX最后一个在坚持。

AMD 的 Infinity Fabric 专门用于将其自己的 Eypc 处理器与 Instinct 加速器耦合,就像 Nvidia 的 NV-Link 与 IBM 的 Power CPU 及其自己的 GPU 加速器(如 A100)一样。

英特尔即将推出的用于服务器的处理器系列 Sapphire Rapids 是第一代能够处理 CXL,它在第一次迭代中基于 PCI Express 5.0,但希望快速切换到 PCIe 6.0 以获得更高的传输速率。AMD 紧随其后的是 CPU 系列 Epyc 7004,别名 Genoa。三星已经宣布 CXL 内存扩展器为 PCIe DRAM。

从某种角度看,再现上世纪80年代末和90年代初的总线大战会很有趣。供应商之间为争夺他们所控制的标准而进行的斗争最终导致了PCI-X和PCI-Express总线的创建,这些总线以及分支InfiniBand interconnect在服务器领域占据了20年的主导地位,以及分支InfiniBand interconnect,它最初是作为一个通用的交换结构来连接高带宽和低延迟的所有东西。这可能要比其他情况下花费更长的时间——改写历史是很困难的。

CXL 将如何改变数据中心

据The Register报道,Compute Express Link (CXL) 有可能从根本上改变系统和数据中心的构建和运营方式。经过 190 多家公司的多年联合开发,开放标准几乎已准备好迎接黄金时间。

对于那些不熟悉的人,CXL 定义了一个通用的、缓存一致的接口,用于连接 CPU、内存、加速器和其他外围设备。在接受The Register采访的时候,CXL 董事长兼英特尔技术计划总监 Jim Pappas表示,该标准对数据中心的影响是广泛的。

因此,第一批 CXL 兼容系统预计将在今年晚些时候与英特尔的 Sapphire Rapids Xeon Scalables 和 AMD 的 Genoa 第四代 Epycs 一起推出,我们询问了Pappas,问他预计 CXL 将如何在短期内改变行业。

根据 Pappas 的说法,CXL 的首批实现之一可能涉及系统内存。他解释说,到目前为止,只有两种方法可以将更多内存附加到加速器上。要么添加更多 DDR 内存通道以支持更多模块,要么必须将其直接集成到加速器或 CPU 封装中。

“你不能将内存放在 PCIe 总线上,”但使用 CXL,你可以,Pappas 说。“CXL 是为加速器设计的,但它也被设计为具有内存接口。我们从一开始就知道这可以用作内存的不同端口。”

无需使用更多或更大的内存模块填充系统,而是可以通过使用 PCIe 和 CXL 通用接口的卡安装额外的内存。并且由于 CXL 2.0 规范中引入的简单交换系统,包括内存在内的资源可以被多个系统同时池化和访问。

重要的是要注意,在这种配置中,只有资源本身而不是内存的内容在主机之间共享,Pappas 强调。“每个内存区域最多属于一个相干域。我们不是要共享内存;这变得更加复杂。”

另一个用例涉及分层内存架构,其中系统利用封装上的高带宽内存、直接连接到 CPU 的相当大的快速 DDR5 内存池,以及通过 CXL 模块连接的更大的慢速内存池。

根据 Pappas 的说法,内存池和分层内存对数据中心和云运营商有影响。“云客户面临的最大问题是他们的第一大支出是内存。他们大约 50%的设备支出用于内存,”他说。

通过池化这些内存,Pappas 认为运营商可以通过减少闲置的内存量来实现巨大的成本节约。Pappas 说,由于池化或分层内存的行为与连接到 CPU 的系统内存没有任何不同,因此无需修改应用程序即可利用这些技术。如果应用程序“要求更多内存,那么现在基本上是无限供应”。

这项技术也不是理论上的。内存池和分层内存是 CXL 初创公司 Tanzanite Silicon Solutions 在今年五月被 Marvell Technologies 收购之前正在研究的几项技术之一。Marvell 认为,该技术将证明对实现真正可组合的基础设施至关重要,而到目前为止,这些基础设施在很大程度上仅限于计算和存储。

Pappas 还希望 CXL 通过在 CPU、AI 加速器和/或 GPU 之间建立比目前通过 PCIe 实现的更密切的关系,从而使 AI/ML 工作负载受益。

在基本层面上,CPU 与外围设备(如 GPU)交互的方式是通过 PCIe 总线来回发送加载/存储指令。CXL 消除了这个瓶颈,使指令能够在加速器和主机之间进行流式传输。

“这与双处理器系统中发生的情况非常相似,其中高速缓存在处理器之间保持一致。我们正在将其扩展到加速器,”Pappas说。

将这种缓存一致性扩展到 CPU 以外的加速器绝非易事或新想法。

他告诉我们,英特尔和其他公司过去曾尝试过为加速器开发标准化互连,但都失败了。部分问题是与这些互连相关的复杂性在组件之间共享,这使得将它们扩展到第三方非常困难。“当我们在英特尔尝试这样做时,它非常复杂,几乎没有人,基本上没有人能够真正让它发挥作用,”Pappas透露。他认为,对于 CXL,基本上所有的复杂性都包含在主机 CPU 中。

这种不对称的复杂性并非没有权衡,但 Pappas 认为它们非常值得。这些以应用程序亲和性的形式出现,特别是哪个加速器获得对缓存或内存的优先访问权,哪个必须扮演次要角色。

Pappas 声称,这在一定程度上得到了缓解,因为客户通常会知道加速器将访问哪些内存区域与主机访问的内存区域。用户将能够通过在 BIOS 中设置偏差来适应。

CXL 标准还没有完成。CXL 联盟预计将在今年晚些时候发布 3.0 规范。

该更新包括从每秒 32 千兆传输到 64 的提升,符合计划向 PCIe 6.0 的迁移,以及对许多新的内存使用模型的支持,Pappas 表示。该规范还介绍了一种以非对称方式实施 CXL 互连技术的途径。此功能将允许 GPU 或 NIC 等设备直接与其他 CXL 设备交互,从而完全消除 CPU 作为瓶颈。

“这将非常重要,因为您可以获得多个需要持续运行的加速器,”他说。

最后,该规范暗示了引入多级交换的 CXL 结构。

CXL 网络结构将是将技术扩展到机架级别之外的关键。并且有理由相信这可能会出现在 Gen-Z之后的 3.0 版本中——他们在去年底将其相干记忆结构资产捐赠给 CXL 联盟。

尽管 CXL 对于数据中心的未来可能令人兴奋,但不要指望它会在一夜之间取得成功。该技术还处于起步阶段,预计将在今年晚些时候推出第一代兼容系统。

Pappas 预计配备 CXL 的系统将分阶段推出,分层内存和内存池可能是第一个主流用例。

“明年,第一轮系统将主要用于概念验证,”他说。“说实话,没有人会采用从未尝试过的新技术。”

在概念验证之后,Pappas 预计在该技术最终开始在生产环境中出现之前,至少还要进行一年的实验性部署。

关于CXL的一些基础知识

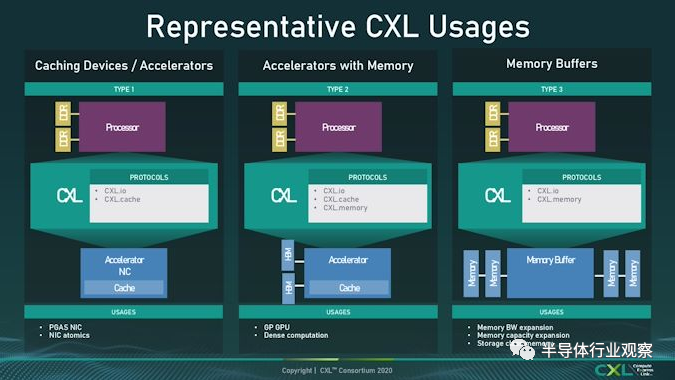

作为一种开放式互连新标准,CXL面向 CPU 和专用加速器的密集型工作负载,这些负载都需要在主机和设备之间实现高效稳定的存储器访问。

PCI Express (PCIe) 已经存在多年,最近完成的 PCIe 基础规范 5.0 版本现在能够以高达 32GT/s 的速度实现 CPU 和外设的互连。然而,在具有大型共享内存池和许多需要高带宽设备的环境中,PCIe 受到了一些限制。PCIe 没有指定支持一致性的机制,并且不能高效地管理隔离的内存池,因为每个 PCIe 层级都要共享一个 64 位地址空间。此外,PCIe 链路的延迟可能过高,无法高效管理系统中多个设备的共享内存。

CXL 标准通过提供利用 PCIe 5.0 物理层和电气元件的接口来消除其中一些限制,同时提供极低延迟路径,用于主机处理器和需要共享内存资源的设备(如加速器和内存扩展器)之间进行内存访问和一致缓存。支持的 CXL 标准模式主要围绕采用 x16 通道配置并以 32GT/s 运行的 PCIe 5.0 PHY(表 1)。x8 和 x4 通道配置也支持 32GT/s,以支持分叉。任何比 x4 通道窄或比 32GT/s 慢的模式都被称为降级模式,这类模式在目标应用中显然不常见。虽然 CXL 可以为许多应用带来立竿见影的性能优势,但是某些设备不需要与主机进行密切交互,而是主要需要在处理大型数据对象或连续流时发出工作提交和完成事件的信号。对于此类设备,在加速接口使用 PCIe 就很合适,而 CXL 没有明显优势。

CXL 标准定义了 3 个协议,这些协议在通过标准 PCIe 5.0 PHY 以 32 GT/s 传输之前一起动态复用:

CXL.io 协议本质上是经过一定改进的 PCIe 5.0 协议,用于初始化、链接、设备发现和列举以及寄存器访问。它为 I/O 设备提供了非一致的加载/存储接口。

CXL.cache 协议定义了主机和设备之间的交互,允许连接的 CXL 设备使用请求和响应方法以极低的延迟高效地缓存主机内存。

CXL.mem 协议提供了主机处理器,可以使用加载和存储命令访问设备连接的内存,此时主机 CPU 充当主设备,CXL 设备充当从属设备,并且可以支持易失性和持久性存储器架构。

三个协议产生的数据都通过仲裁和多路复用 (ARB/MUX) 模块一起动态复用,然后被移交到 PCIe 5.0 PHY,进而以 32GT/s 的速度进行传输。ARB/MUX 在 CXL 链路层(CXL.io 和 CXL.cache/mem)发出的请求之间进行仲裁,并根据仲裁结果复用数据,仲裁结果使用加权循环仲裁,权重由主机设置。ARB/MUX 还处理链路层发出的功耗状态转换请求,向物理层创建实现有序降耗操作的单个请求。

CXL 通过固定宽度的 528 位微片传输数据,该微片由四个 16 字节时隙组成,并添加了两个字节 CRC:(4 x 16 + 2 = 66 字节= 528 位)。插槽采用多种格式定义,可专用于 CXL.cache 协议或 CXL.mem 协议。片头定义了插槽格式,并携带允许事务层将数据正确路由到预期协议的信息。

由于 CXL 使用 PCIe 5.0 PHY 和电气元件,它可以有效地插入到任何可以通过 Flex Bus 使用 PCIe 5.0 的系统中。Flex Bus 是一个灵活的高速端口,可以静态配置为支持 PCIe 或 CXL。图 2 举例显示了 Flex Bus 链路。这种方法使 CXL 系统能够利用 PCIe 重定时器;但是,目前 CXL 仅定义为直连 CPU 链路,因此无法利用 PCIe 交换机。随着标准的逐步完善,交换功能可能会被添加到标准中;如果是这样,则需要创建新的 CXL 交换机。

审核编辑 :李倩

-

cpu

+关注

关注

68文章

10871浏览量

211939 -

加速器

+关注

关注

2文章

799浏览量

37898 -

服务器

+关注

关注

12文章

9191浏览量

85505

原文标题:兼并OpenCAPI ,CXL 将一统CPU 互连标准

文章出处:【微信号:芯长征科技,微信公众号:芯长征科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

CXL技术:全面升级数据中心架构

模块化机房:数据中心的未来

CXL将如何改变数据中心

CXL将如何改变数据中心

评论