各种拓扑结构中 SiC MOSFET 的出现带来了巨大的性能和效率改进。但是,如果使用不当,工程师很快就会发现自己对设备故障感到沮丧。与客户的看法形成鲜明对比,这些故障通常不是 SiC MOSFET 技术的内在弱点,而是围绕栅极环路的设计选择。尤其是对高端和低端器件之间的开启交互缺乏关注可能会导致由错误的电路选择引发的灾难性故障。在本文中,我们展示了在栅极电路环路中使用栅极源极电容器的经典阻尼效果是 SiC MOSFET 栅极的巨大危险和经常隐藏的杀手。这种抑制门上振荡的做法,为了改善开关瞬变实际上会导致栅极上的重应力。通过测量不容易看到这种应力,因为它们发生在内部栅极节点而不是外部可测量节点上,这要归功于 CGS,似乎很好地抑制了。此外,我们还讨论了必须关注 SiC MOSFET 体二极管的问题。对 SiC MOSFET 的体二极管存在许多误解,以至于即使是资深技术专家有时也认为该体二极管是无反向恢复的。事实上,我们表明 SiC MOSFET 的体二极管,尤其是平面栅极器件,可能是造成栅极损坏的罪魁祸首。

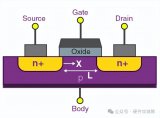

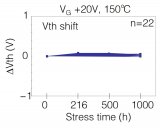

为什么需要关注 SiC MOSFET 栅极?尽管具有传统的 SiO 2栅极氧化物,但该氧化物的性能比传统 Si 基半导体中的经典 Si-SiO 2界面更差。这是由于在SiC 的 Si 终止面上生长的 SiO 2界面处的本征缺陷。这使得氧化物更容易受到过电压和其他电应力的影响,相对于基于硅的器件,V GSMax相当大。

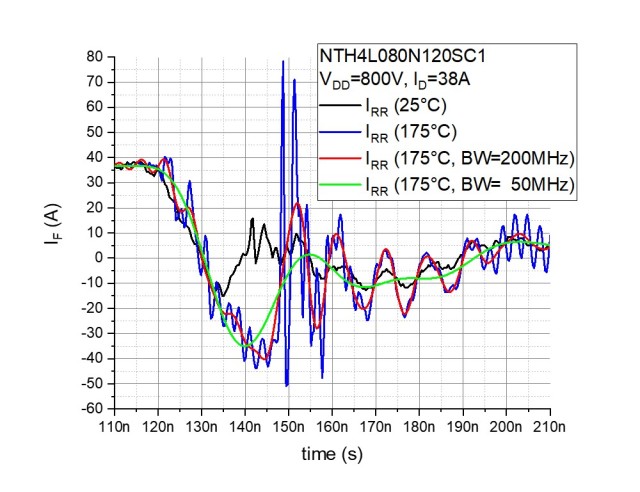

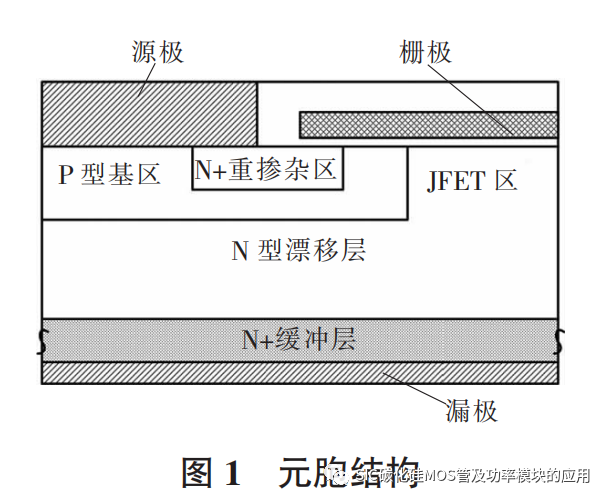

图 1 显示了 SiC MOSFE 的活泼体二极管,小 Q RR和短 t rr可能难以测量,并且经常与测试系统寄生电容混淆。然而,在 I RR返回支路中可能出现>40 A/ns 的 di/dt 。这种超快 IRR 事件可以将设备本身的 V GS拉高超过伏特,并在每个开启周期中造成严重的过应力。产生的超调量与 I RR速度成正比;最终,这种持续的压力将导致灾难性的失败。

图 1:反向恢复电流 SiC MOSFET

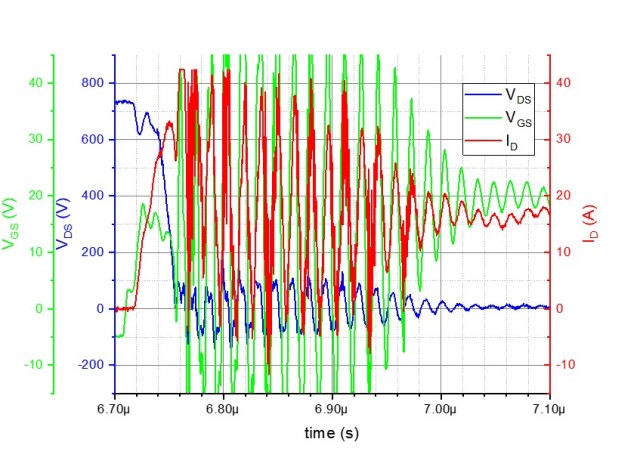

除了启用门上的过应力外,禁用的门也会受到影响。如果V GS >V th,I D开始流入禁用设备。直通电流将导致谐振回路的进一步激励,并且可能发生具有直通电流的自持振荡。如图 2 所示。

图2:在碳化硅MOSFET的开关瞬态:V DD = 720V,我d = 20A,T c ^ = 175℃,R G ^ =10Ω,C GS = 10nF的

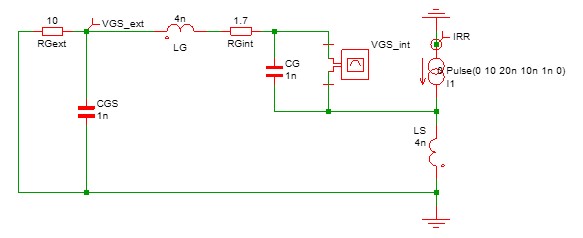

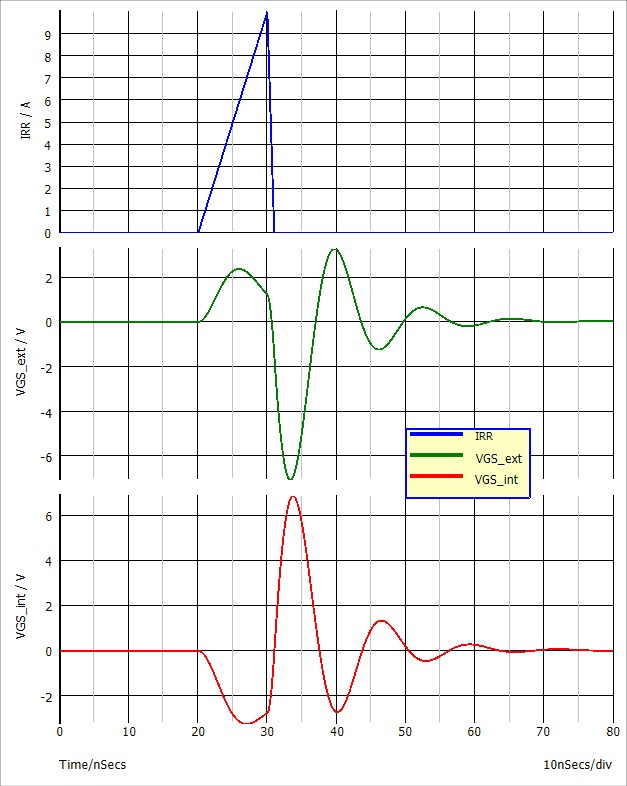

通常,设计人员会尝试通过添加外部 C GS电容器来减轻这些振荡影响(影响见图 2)。这个电容器可以方便地抑制振荡,似乎解决了这个问题,或者看起来是这样。所监督的是这样一个事实,即阻尼和由此产生的干净的示波器图像类似于真实门外的事件,设计师在现实中所做的事情正在恶化对真实门的影响。外部 C GS建立了一个额外的谐振槽,并恶化了快速 I RR瞬变(回弹)对栅极的影响。使用物理的、可扩展的 SPICE 模型,人们可以研究这些难以探测的效应,并且很快就会注意到 C GS电容器。图 3 显示了仿真原理图,图 4 显示了结果结果,显示了由快速 IRR 和添加的阻尼电容器的相互作用导致的 V GS上的 7 V 过应力。

图 3:仿真示意图

图 4:仿真分析

使用 SiC MOSFET 成功实现高速开关的关键是适当调整栅极电路和所用器件的驱动条件,仔细阅读数据表将很快发现当前器件内部 RG 的快速范围。此外,移除外部 C GS电容器,设置正确的外部栅极电阻 R G,并使用具有源极检测的封装(TO-247-4L、D 2 PAK-7L 或类似),搭配正确的栅极回路设计将产生最好的切换。提供超过 120 V/ns 和 6 A/ns 的瞬变(采用同类最佳的 MOSFET),前提是回路的其余部分寄生电感得到处理。

审核编辑:刘清

-

电容器

+关注

关注

64文章

6222浏览量

99615 -

二极管

+关注

关注

147文章

9637浏览量

166449 -

MOSFET

+关注

关注

147文章

7162浏览量

213255 -

SiC

+关注

关注

29文章

2811浏览量

62635

发布评论请先 登录

相关推荐

业界首款用于SiC MOSFET栅极保护的非对称瞬态抑制二极管系列

SiC MOSFET和SiC SBD的区别

新型OptiMOS 7 MOSFET改进汽车应用中的导通电阻、设计稳健性和开关效率

Littelfuse发布IX4352NE低侧SiC MOSFET和IGBT栅极驱动器

Littelfuse宣布推出IX4352NE低侧SiC MOSFET和IGBT栅极驱动器

碳化硅模块(SiC模块/MODULE)大电流下的驱动器研究

MOSFET栅极驱动电路设计方案

SiC功率元器件中浪涌抑制电路设计

3300V SiC MOSFET栅氧可靠性研究

如何消除SiC MOSFET——栅极电路设计中的错误及其对稳健性的影响

如何消除SiC MOSFET——栅极电路设计中的错误及其对稳健性的影响

评论