电子发烧友网报道(文/吴子鹏)后摩尔定律时代,如何在不依赖价格昂贵的先进制程的情况下显著提升芯片的性能,成为行业共同关注的话题。此时,封装在整个产业中的战略地位凸显出来,从传统的倒装和晶圆级封装,逐渐扩充到了扇出型封装、3D封装、SiP(系统级封装)等方式,后面几种都是先进封装的代表性技术。

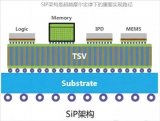

SiP封装的全称为System In a Package系统级封装,将多种功能芯片,包括处理器、存储器等功能芯片集成在一个封装内,从而实现一个基本完整的功能。SiP和SoC虽然都是集成,但是两者有着明显的差别,后者是从芯片设计角度出发,是摩尔定律的延续,SiP则是从封装角度出发,是超越摩尔定律的重要路径。按照从属关系,SoC是SiP的一部分。我们都知道,苹果公司的Apple Watch和AirPods都是SiP封装技术的受益者。

随着SiP封装的作用越来越被认可,目前布局的厂商维度也变得更加多元化,比如消费电子产业链中的代工厂和组装厂,汽车产业链中的Tier 1级供应商,传统的半导体封装企业等等。那么厂商如何看待和布局SiP封装技术?而SiP封装和热门技术Chiplet又有怎样的关系?在由博闻创意主办的第六届中国系统级封装大会-苏州站上,相关专家对于SiP封装技术的发展发表了自己的观点。

SiP封装技术的定位和效果

苹果公司在初代Apple Watch便开始使用SiP封装技术,并取得了积极的效果。据悉,在Apple Watch中,共包含了大概900多个电子元器件,通过SiP封装技术,苹果将CPU、记忆体、音频、触控、电源管理、WiFi、NFC等独立的功能器件综合在一起。在Apple Watch Series 6 中,苹果通过 SiP 封装技术集成了一颗苹果 A13 应用处理器和一些其他功能的处理器。

那么,到底什么样的应用应该采用SiP封装技术?或者说SiP封装技术可以应用的方向有哪些?紫光展锐(上海)科技有限公司封装系统架构部部长陈思谈到了SiP封装技术的定位。

紫光展锐(上海)科技有限公司封装系统架构部部长陈思

“SiP封装技术最好的特点是灵活性,可以根据需求来设计产品。SiP封装技术是集成电路其中的一个发展方向,它是通过先进封装的技术达到性能、尺寸和功耗等方面的平衡。和SoC相比,SoC由于将数模元件都集成到一个die上,其集成度和电性能都会更高,但成本随着工艺精进越来越高。且随着单一die的尺寸变大,SoC的良率也是一个极大的挑战。” 陈思表示,“而SoC面临的两大挑战,恰恰是SiP封装的优点。SiP封装能够将数模分开,可以在数字逻辑部分选择使用先进制程,在模拟部分使用成熟制程,系统成本更低,上市周期更短。”

通过紫光展锐SiP封装产品和普通模组产品的对比,陈思讲到了一些SiP封装的应用效果,其中SiP封装的优势为:

·更灵活的系统设计;

·更高的空间利用率;

·更简洁的系统;

·更快的上市时间;

·更高的性能;

·更高的可靠性。

采用SiP封装之后达到的效果为:

·产品多样性;

·减小45%的模组面积;

·产品设计环节极大减少;

·提前4个月上市;

·RF性能提高;

·可靠性提高。

陈思指出,SiP封装发展需要三大支撑,也就是业务开展的“铁三角”,分别是多样化的客户、全面的技术和大量的人才。

先进封装之hybrid bonding技术

刚刚已经提到目前全球很多公司都在布局SiP封装技术,不过大家入局的角度不同,比如很有代表性的是,台积电推出的是先进封装解决方案,其中的代表技术为3DFabric技术,由前端和后端技术组成,包括TSMC-SoIC、CoWoS和InFO。

为什么在晶圆代工方面独领风骚的台积电还要入局先进封装呢?这项技术到底有什么好处呢?我们能够从国际半导体产业协会(SEMI)高级总监张文达的分享中找到部分答案。

国际半导体产业协会(SEMI)高级总监张文达

他表示,“封装近几年是一个异军突起的状态。从2D封装逐步进化到3D封装的过程中,引脚的密度越来越高,作为摩尔定律的延伸,先进封装的关注点已经从摩尔定律时单位面积的晶体管数量转变为现在的单位面积上的连接点数量。”

张文达指出,目前SEMI先进封装方面比较关注hybrid bonding这样技术,中文释义为混合键合技术。很多从业者都知道英特尔也在密切关注这项技术的发展,2021年6月,英特尔院士、封装研究与系统解决方案总监Johanna Swan在解读英特尔封装技术路线图时专门提到,“从标准封装到嵌入式桥接时,凸点间距从100微米变为55-36微米。到Foveros封装时,英特尔将芯片堆叠在一起,实现横向和纵向的互连,凸点间距大概是50微米。未来,英特尔将通过采用Hybrid Bonding技术,计划实现小于10微米的凸点间距。”很明显,这是和张文达上面的解读是不谋而合的。

“Hybrid Bonding技术让器件之间的数据交互不再需要通过内部的总线和外部的总线走很大一圈,可以实现‘楼上’与‘楼下’的快速通信,使得片内的带宽得到巨量的提升;其次,Hybrid Bonding技术能够支持芯片在很高的频率下运行;还有一点是Hybrid Bonding技术让芯片不再使用有机材料,散热能力得到了大幅提升。” 张文达在此提到。

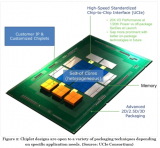

Chiplet需要全新的EDA工具

在先进封装的概念下,有两个分支概念的发展是格外受到重视的,一个是上述提到的SiP封装,另一个则是Chiplet。目前,Chiplet的未来发展路线还在规划中,但是作为先进封装的一种延伸,Chiplet在部分从业者眼中,也被认为是一种SiP技术。当然,在技术高速筑基和发展阶段,为其定调还为时过早。不过,目前Chiplet的一些技术优势已经显露出来。

芯和半导体科技(上海)有限公司联合创始人、高级副总裁代文亮表示,Chiplet是模块化SoC的兴起,主要的优势包括能够使用更小的芯片获得更高的良率,超越光罩的限制;在相关芯片的最佳节点上能够混合和匹配小芯片;Chiplet具有可重用性和更低的成本,能够达到更佳的性能。

芯和半导体科技(上海)有限公司联合创始人、高级副总裁代文亮

基于以上的优势和特点,他指出,Chiplet需要一个全新的EDA设计工具,这个EDA工具要能够实现几方面的功能。

首先是在架构方面,适用于Chiplet的EDA工具需要能够实现系统级连接,可以做到堆栈管理,支持层次化设计。

其次是在物理实现方面,适用于Chiplet的EDA工具需要有协同设计环境,可以实现跨领域的工程变更,支持多芯片3D布局规划和布线,拥有一个统一的数据库。

第三是在分析方面,适用于Chiplet的EDA工具可以完成片上、封装电磁分析,支持芯片封装联合仿真,可以进行多物理分析,能够与布局布线工具无缝集成。

最后是在验证方面,适用于Chiplet的EDA工具支持芯片工艺约束、封装制造设计规则、芯片3D封装约束和芯片数据通信协议等。

深圳市奇普乐芯片技术有限公司CEO许荣峰谈到了Chiplet应用落地的可行性探索,他也是认可Chiplet技术其实就是一种SiP技术,是SiP技术的再发展。他认为,2.5D和3D封装技术是Chiplet技术的集大成者,目前相关工艺已经成熟。相较于过往SiP技术更加强调载板,Chiplet技术的关键是中介层,针对不同的应用,方案设计只需要更新中介层即可。

深圳市奇普乐芯片技术有限公司CEO许荣峰

今年上半年,芯片制造商英特尔、台积电、三星联合日月光、AMD、ARM、高通、谷歌、微软、Meta(Facebook)等十家行业巨头共同宣布,成立小芯片(Chiplet)联盟,并推出一个全新的通用芯片互联标准——Ucle。许荣峰也特别提到了这个联盟,并认为未来的20年将会是Chiplet发展的“黄金二十年”。他指出,“Chiplet并不是先进制程的延续,很多功能单元会停留在最适合它的工艺节点上,Chiplet要做的就是根据相关协议标准将不同公司的芯片裸die封装起来,形成一个新的多功能芯片,这是Chiplet给市场带来的改变,给半导体行业带来了一个新的设计芯片的方法论。”

“Chiplet将原来芯片产业从设计、制造、封装到客户这样的产业链改变为从客户的需求到封装,再到制造这样一个全新的产业链。在Ucle联盟中有谷歌、微软、Meta三家公司,他们是站在客户的角度思考Chiplet应该如何被利用。当前我们看到的是Chiplet 1.0,只是SoC的一种延续,而Chiplet 2.0会利用小芯片从软件到硬件去设计芯片,让芯片更加接近市场,让客户定制他们所需要的芯片。” 许荣峰讲到。

同时,他也强调,Chiplet需要全新的EDA设计工具。

写在最后

目前正处于芯片产业的变革时代,超越摩尔的声音越来越大,SiP技术和Chiplet会越来越受到重视,会不断涌现出更新的技术来支持先进封装的发展,并不断形成全行业的标准体系,让芯片产业进入一个新的阶段。

SiP封装的全称为System In a Package系统级封装,将多种功能芯片,包括处理器、存储器等功能芯片集成在一个封装内,从而实现一个基本完整的功能。SiP和SoC虽然都是集成,但是两者有着明显的差别,后者是从芯片设计角度出发,是摩尔定律的延续,SiP则是从封装角度出发,是超越摩尔定律的重要路径。按照从属关系,SoC是SiP的一部分。我们都知道,苹果公司的Apple Watch和AirPods都是SiP封装技术的受益者。

随着SiP封装的作用越来越被认可,目前布局的厂商维度也变得更加多元化,比如消费电子产业链中的代工厂和组装厂,汽车产业链中的Tier 1级供应商,传统的半导体封装企业等等。那么厂商如何看待和布局SiP封装技术?而SiP封装和热门技术Chiplet又有怎样的关系?在由博闻创意主办的第六届中国系统级封装大会-苏州站上,相关专家对于SiP封装技术的发展发表了自己的观点。

SiP封装技术的定位和效果

苹果公司在初代Apple Watch便开始使用SiP封装技术,并取得了积极的效果。据悉,在Apple Watch中,共包含了大概900多个电子元器件,通过SiP封装技术,苹果将CPU、记忆体、音频、触控、电源管理、WiFi、NFC等独立的功能器件综合在一起。在Apple Watch Series 6 中,苹果通过 SiP 封装技术集成了一颗苹果 A13 应用处理器和一些其他功能的处理器。

那么,到底什么样的应用应该采用SiP封装技术?或者说SiP封装技术可以应用的方向有哪些?紫光展锐(上海)科技有限公司封装系统架构部部长陈思谈到了SiP封装技术的定位。

紫光展锐(上海)科技有限公司封装系统架构部部长陈思

“SiP封装技术最好的特点是灵活性,可以根据需求来设计产品。SiP封装技术是集成电路其中的一个发展方向,它是通过先进封装的技术达到性能、尺寸和功耗等方面的平衡。和SoC相比,SoC由于将数模元件都集成到一个die上,其集成度和电性能都会更高,但成本随着工艺精进越来越高。且随着单一die的尺寸变大,SoC的良率也是一个极大的挑战。” 陈思表示,“而SoC面临的两大挑战,恰恰是SiP封装的优点。SiP封装能够将数模分开,可以在数字逻辑部分选择使用先进制程,在模拟部分使用成熟制程,系统成本更低,上市周期更短。”

通过紫光展锐SiP封装产品和普通模组产品的对比,陈思讲到了一些SiP封装的应用效果,其中SiP封装的优势为:

·更灵活的系统设计;

·更高的空间利用率;

·更简洁的系统;

·更快的上市时间;

·更高的性能;

·更高的可靠性。

采用SiP封装之后达到的效果为:

·产品多样性;

·减小45%的模组面积;

·产品设计环节极大减少;

·提前4个月上市;

·RF性能提高;

·可靠性提高。

陈思指出,SiP封装发展需要三大支撑,也就是业务开展的“铁三角”,分别是多样化的客户、全面的技术和大量的人才。

先进封装之hybrid bonding技术

刚刚已经提到目前全球很多公司都在布局SiP封装技术,不过大家入局的角度不同,比如很有代表性的是,台积电推出的是先进封装解决方案,其中的代表技术为3DFabric技术,由前端和后端技术组成,包括TSMC-SoIC、CoWoS和InFO。

为什么在晶圆代工方面独领风骚的台积电还要入局先进封装呢?这项技术到底有什么好处呢?我们能够从国际半导体产业协会(SEMI)高级总监张文达的分享中找到部分答案。

国际半导体产业协会(SEMI)高级总监张文达

他表示,“封装近几年是一个异军突起的状态。从2D封装逐步进化到3D封装的过程中,引脚的密度越来越高,作为摩尔定律的延伸,先进封装的关注点已经从摩尔定律时单位面积的晶体管数量转变为现在的单位面积上的连接点数量。”

张文达指出,目前SEMI先进封装方面比较关注hybrid bonding这样技术,中文释义为混合键合技术。很多从业者都知道英特尔也在密切关注这项技术的发展,2021年6月,英特尔院士、封装研究与系统解决方案总监Johanna Swan在解读英特尔封装技术路线图时专门提到,“从标准封装到嵌入式桥接时,凸点间距从100微米变为55-36微米。到Foveros封装时,英特尔将芯片堆叠在一起,实现横向和纵向的互连,凸点间距大概是50微米。未来,英特尔将通过采用Hybrid Bonding技术,计划实现小于10微米的凸点间距。”很明显,这是和张文达上面的解读是不谋而合的。

“Hybrid Bonding技术让器件之间的数据交互不再需要通过内部的总线和外部的总线走很大一圈,可以实现‘楼上’与‘楼下’的快速通信,使得片内的带宽得到巨量的提升;其次,Hybrid Bonding技术能够支持芯片在很高的频率下运行;还有一点是Hybrid Bonding技术让芯片不再使用有机材料,散热能力得到了大幅提升。” 张文达在此提到。

Chiplet需要全新的EDA工具

在先进封装的概念下,有两个分支概念的发展是格外受到重视的,一个是上述提到的SiP封装,另一个则是Chiplet。目前,Chiplet的未来发展路线还在规划中,但是作为先进封装的一种延伸,Chiplet在部分从业者眼中,也被认为是一种SiP技术。当然,在技术高速筑基和发展阶段,为其定调还为时过早。不过,目前Chiplet的一些技术优势已经显露出来。

芯和半导体科技(上海)有限公司联合创始人、高级副总裁代文亮表示,Chiplet是模块化SoC的兴起,主要的优势包括能够使用更小的芯片获得更高的良率,超越光罩的限制;在相关芯片的最佳节点上能够混合和匹配小芯片;Chiplet具有可重用性和更低的成本,能够达到更佳的性能。

芯和半导体科技(上海)有限公司联合创始人、高级副总裁代文亮

基于以上的优势和特点,他指出,Chiplet需要一个全新的EDA设计工具,这个EDA工具要能够实现几方面的功能。

首先是在架构方面,适用于Chiplet的EDA工具需要能够实现系统级连接,可以做到堆栈管理,支持层次化设计。

其次是在物理实现方面,适用于Chiplet的EDA工具需要有协同设计环境,可以实现跨领域的工程变更,支持多芯片3D布局规划和布线,拥有一个统一的数据库。

第三是在分析方面,适用于Chiplet的EDA工具可以完成片上、封装电磁分析,支持芯片封装联合仿真,可以进行多物理分析,能够与布局布线工具无缝集成。

最后是在验证方面,适用于Chiplet的EDA工具支持芯片工艺约束、封装制造设计规则、芯片3D封装约束和芯片数据通信协议等。

深圳市奇普乐芯片技术有限公司CEO许荣峰谈到了Chiplet应用落地的可行性探索,他也是认可Chiplet技术其实就是一种SiP技术,是SiP技术的再发展。他认为,2.5D和3D封装技术是Chiplet技术的集大成者,目前相关工艺已经成熟。相较于过往SiP技术更加强调载板,Chiplet技术的关键是中介层,针对不同的应用,方案设计只需要更新中介层即可。

深圳市奇普乐芯片技术有限公司CEO许荣峰

今年上半年,芯片制造商英特尔、台积电、三星联合日月光、AMD、ARM、高通、谷歌、微软、Meta(Facebook)等十家行业巨头共同宣布,成立小芯片(Chiplet)联盟,并推出一个全新的通用芯片互联标准——Ucle。许荣峰也特别提到了这个联盟,并认为未来的20年将会是Chiplet发展的“黄金二十年”。他指出,“Chiplet并不是先进制程的延续,很多功能单元会停留在最适合它的工艺节点上,Chiplet要做的就是根据相关协议标准将不同公司的芯片裸die封装起来,形成一个新的多功能芯片,这是Chiplet给市场带来的改变,给半导体行业带来了一个新的设计芯片的方法论。”

“Chiplet将原来芯片产业从设计、制造、封装到客户这样的产业链改变为从客户的需求到封装,再到制造这样一个全新的产业链。在Ucle联盟中有谷歌、微软、Meta三家公司,他们是站在客户的角度思考Chiplet应该如何被利用。当前我们看到的是Chiplet 1.0,只是SoC的一种延续,而Chiplet 2.0会利用小芯片从软件到硬件去设计芯片,让芯片更加接近市场,让客户定制他们所需要的芯片。” 许荣峰讲到。

同时,他也强调,Chiplet需要全新的EDA设计工具。

写在最后

目前正处于芯片产业的变革时代,超越摩尔的声音越来越大,SiP技术和Chiplet会越来越受到重视,会不断涌现出更新的技术来支持先进封装的发展,并不断形成全行业的标准体系,让芯片产业进入一个新的阶段。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

SiP

+关注

关注

5文章

507浏览量

105502 -

封装

+关注

关注

127文章

8036浏览量

143543 -

chiplet

+关注

关注

6文章

436浏览量

12637

发布评论请先 登录

相关推荐

SIP封装技术:引领电子封装新革命!

在电子技术的快速发展中,封装技术作为连接芯片与外界的桥梁,其重要性日益凸显。SIP封装(System In a Package,系统级封装)作为一种将多种功能芯片集成在一个

解锁Chiplet潜力:封装技术是关键

如今,算力极限挑战正推动着芯片设计的技术边界。Chiplet的诞生不仅仅是技术的迭代,更是对未来芯片架构的革命性改变。然而,要真正解锁Chiplet技术的无限潜力, 先进封装技术 成为

Chiplet在先进封装中的重要性

Chiplet标志着半导体创新的新时代,封装是这个设计事业的内在组成部分。然而,虽然Chiplet和封装技术携手合作,重新定义了芯片集成的可能性,但这种技术合作并不是那么简单和直接。

芯和半导体将参加2024集成电路特色工艺与先进封装测试产业技术论坛

芯和半导体将于本周五(11月29日)参加在四川成都举办的“2024集成电路特色工艺与先进封装测试产业技术论坛暨四川省集成电路博士后学术交流活动”。作为国内Chiplet

Sip技术是什么?Sip封装技术优缺点

SiP(System in Package)技术是一种先进的封装技术,SiP技术允许将多个集成电路(IC)或者电子组件集成到一个单一的封装中

发表于 02-19 15:22

•4172次阅读

先进封装概念火热,SiP与Chiplet成“左膀右臂”

先进封装概念火热,SiP与Chiplet成“左膀右臂”

评论