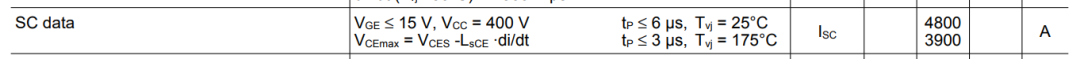

短路耐受时间(tsc)对于功率半导体器件来说是一个比较重要的参数,这也是为什么它会成为目前SiC推广和应用中被多次提及的原因。从目前来看,SiC的短路能力相对于先进的Si基IGBT来讲是低的。有的人就会说了,SiC宣传得如此强大的材料特性,为什么如此,短路能力这么不够看呢?当然了,万物皆不可十全十美,有强有弱才是推动发展的驱动力。

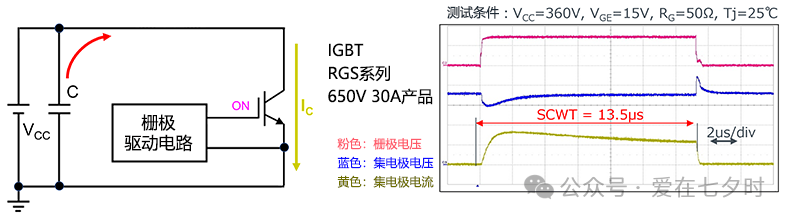

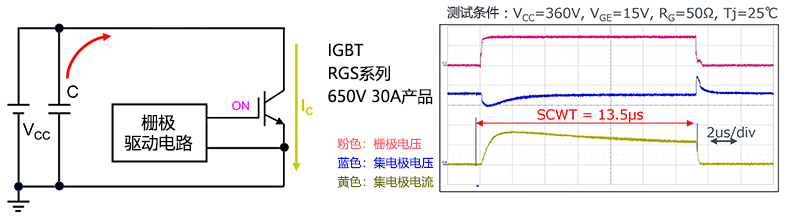

我们都知道,IGBT发生短路时,需要在10us或者更短的时间内关闭IGBT,在相同的短路能耗下可以由其他参数来进行调节,如栅极电压VGE,母线电压等,但最终都是为了保证IGBT不会因为过热而失效。而SiC MOSFET的固有短路能力较小,根本原因也是因为热,是在于短路事件前后的温度分布不合理!

温度分布

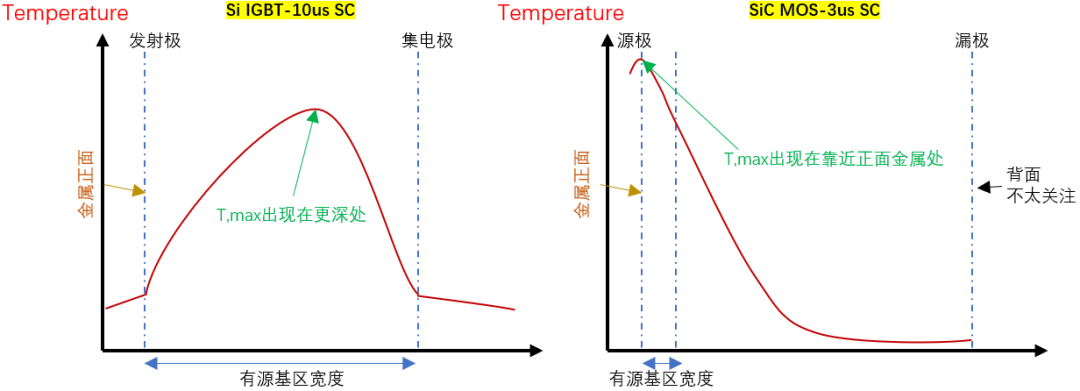

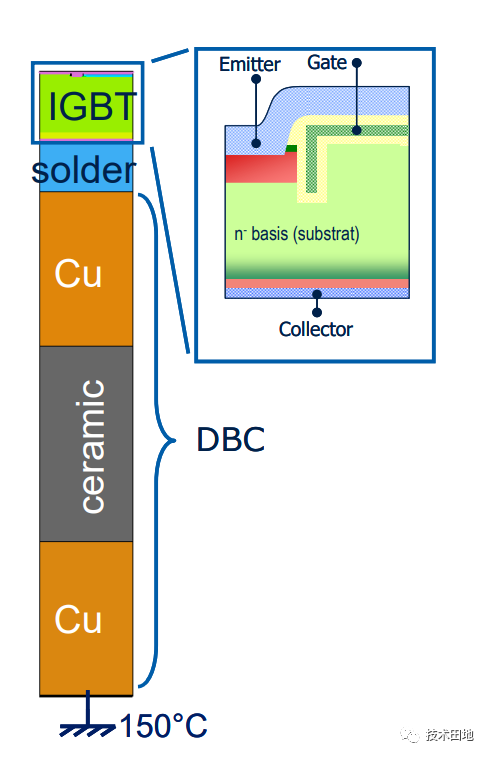

我们来看一下在一定短路时间前后Si IGBT和SiC MOSFET的温度分布,

可以看出,SiC MOS在3us短路前后,整个器件结构的温度分布情况,几乎整个短路能量都在整个结构的前端便面附近产生和消耗。而对于1200V SiC MOSFET,这个有源基区仅仅在10um的范围内。短路产生的能耗主要产生在这个区域前端,导致前端区域温度升高,尤其在前端的金属层、栅极氧化物和其他前端部分造成很大的热应力。而这个较大的温度梯度使得背面的温度几乎没有变化。而Si IGBT的温度在整个器件结构上分布的更为均匀,最高温度出现在整个厚度的2/3处。

因此,★为了提高SiC MOSFET的短路耐受性,特别是正面附近相关的互连结构必须进行热优化。

当然,从SiC MOSFET的内部特性也可以调整其短路特性(这无可厚非,内部权衡是功率器件一直以来所具有的), 但是这又变得“众口难调”的情况,只能“折中”。

内部特性权衡

从SiC MOSFET结构出发,大致由一下几种方式,这些可以从其饱和电流的公式大致看出,SiC MOSFET饱和电流

ID,sat=k/2*(Vgs-Vgs,th)2

Vgs为栅极电压,Vgs,th为栅极阈值电压。

其中,k为通道电导率,可表示为

k=(W*Cox*μn)/L

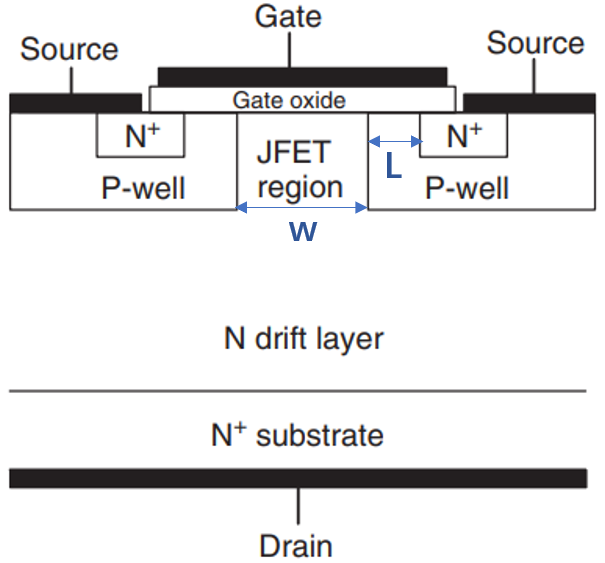

下面是一个DMOSFET的结构,

其中,W为JFET宽度,L为沟道长度,Cox为单位面积氧化物电容,μn为电子迁移率。

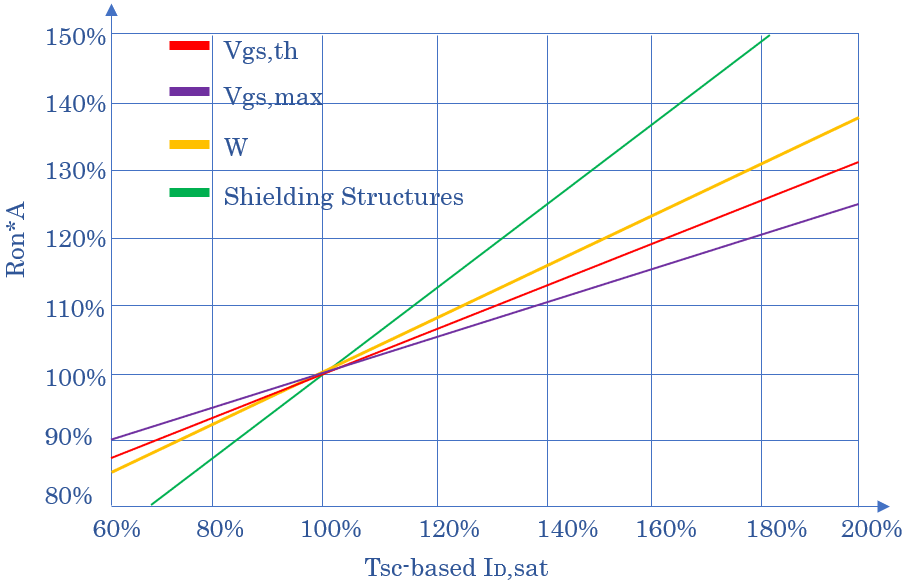

基于短路时间耐量和饱和电流的关系,我们可以看出,通过调整内部特性来提高SiC MOSFET的短路耐量,一般由下面几种权衡:L通道宽度权衡、Vgs,th权衡、Vgs偏置权衡;也可通过Rds,on来权衡(所有短路时间都可以通过牺牲Rds,on来实现)。

但是,这种权衡相应地会对沟道电阻产生影响,从下面的沟道电阻公式我们可以看出来,

RCH=1/((W/L)*Cox*μn*(Vgs-Vgs,th))

栅极偏置控制已经在SiC MOSFET短路保护中被应用,在检测到短路时,Vgs立即降低。

下图给到了这些权衡的关系依赖示意图:

所以,★短路时间和Rds,on之间存在取舍,这也部分说明了SiC MOSFET做出选择的出发点。值得一提的是,以短路时间为代价的低Rds,on只可能在一定程度上实现,因为足够的场屏蔽结构和实现高栅极氧化物的最小栅极氧化层厚度是有限的。这由于元胞设计和电压等级有关联。

为了实现高沟道宽度的低Rds,on,与相同电压等级的Si IGBT相比,SiC MOSFET的"饱和电流和额定电流"的比值ID,sat/Inom往往高很多,一般在10~15倍的范围内;而我们知道的10us短路耐受的IGBT来说一般在4~6倍(有助于保证整体较低的短路能耗)的范围内。

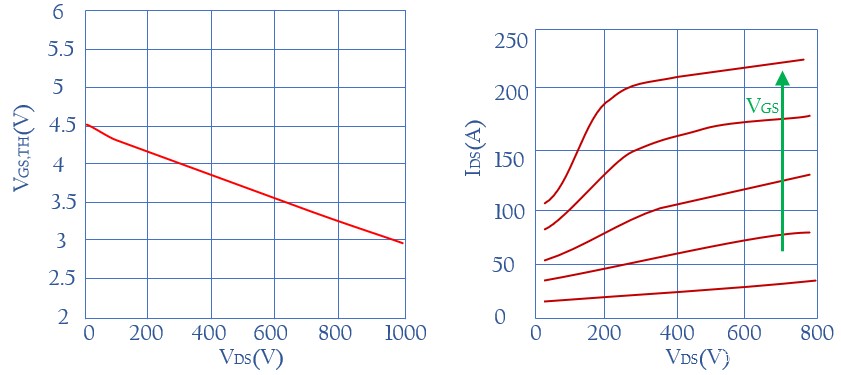

另外,饱和电流和电压等级也有密切关系。这个关系的原因归结于DIBL,即漏感应势垒降低效应(和元胞结构、P屏蔽区域有关),该效应与SiC MOSFET中的短n沟道有关。当漏源电压增加时,电场/空间电荷区域向沟道区域靠近,有效地缩短了沟道。因此,随着漏源电压升高,Vth,gs减小,ID,sat增加(可以结合上面的饱和电流公式来看)。下图是DIBL效应,Vgs,th随VDS升高而减小,ID,sat随VDS升高而升高的示意图。

小结

为了克服Rds,on和短路能力之间的艰难权衡,越来越多的保护措施被提出,比如智能门极驱动方案;好像有的因为SiC MOSFET短路时间短,干脆不进行短路保护。当然,相信未来会发展,一切都有希望......

审核编辑:刘清

-

MOSFET

+关注

关注

146文章

7151浏览量

213114 -

IGBT

+关注

关注

1266文章

3788浏览量

248847 -

SiC

+关注

关注

29文章

2802浏览量

62597 -

栅极电压

+关注

关注

0文章

69浏览量

12793

原文标题:SiC MOSFET短路时间为什么短?!

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何实现SiC MOSFET的短路检测及保护?

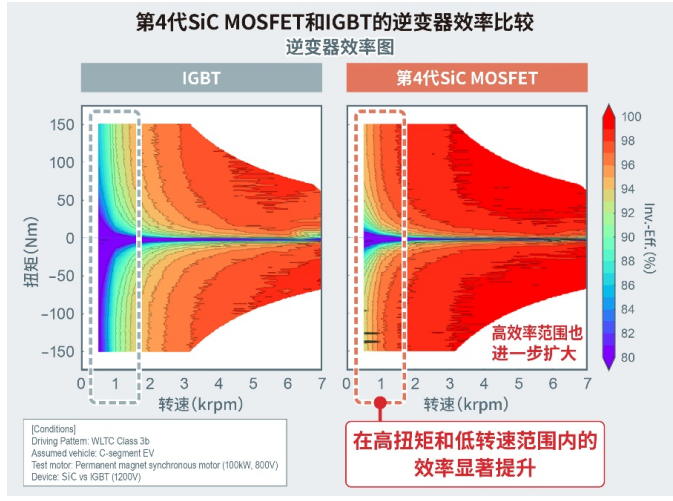

罗姆第4代SiC MOSFET在电动汽车电控系统中的应用及其优势

为何使用 SiC MOSFET

SiC-MOSFET的应用实例

SiC-MOSFET功率晶体管的结构与特征比较

SiC-MOSFET与Si-MOSFET的区别

SiC-MOSFET的可靠性

SiC MOSFET:经济高效且可靠的高功率解决方案

ROHM开发出业界先进的第4代低导通电阻SiC MOSFET

SiC MOSFET学习笔记1:短路保护时间

IGBT短路耐受时间的重要性

为什么SiC MOSFET的短路耐受时间比较小

为什么SiC MOSFET的短路耐受时间比较小

评论