首先,所谓LTSSM,即:Link Training and Status State Machine(链路训练及状态机)

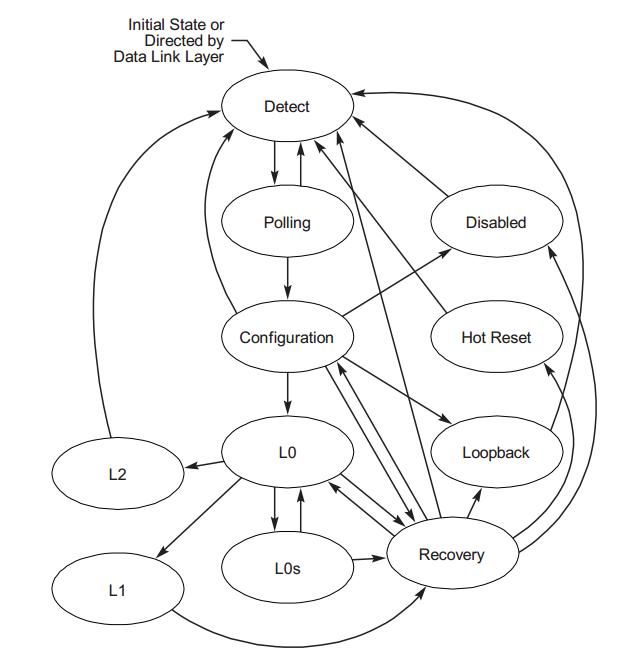

下图为 LTSSM 的状态机及训练过程:

LTSSM 包含 11 个顶层状态:Detect、Polling、Configuration、Recovery、L0、L0s、L1、L2、Hot Reset、Loopback 和 Disable。这些状态可以分为 5 类:

Link Training states(链路训练状态)

Re-Training(Recovery)state(重训练状态)

Software driven Power Management State(由软件控制的电源管理状态)

Active-State Power Management(ASPM)states(动态电源管理状态)

Other states(其他状态)

①各种复位(Reset)之后,状态机的改变为:Detect => Polling => Configuration => L0。在 L0 状态下即可进行标准数据交互。

②链路的 Re-Training 状态也称为 Recovery(恢复)状态。链路进入 Re-Training 状态的原因有多种,例如从低功耗链路状态(如 L1)退出、改变带宽(改变速率或者宽度)等。在该状态下,链路会根据需要重新执行一部分链路训练的流程,然后进入 L0 状态。

③电源管理软件能将设备(Device)切换到低功耗设备状态(D1,D2,D3Hot 或者 D3Cold),这会导致链路进入对应的低功耗链路状态(L1 或者 L2)。

④在某一时刻,如果没有数据在传输,那么 ASPM 硬件可以自动将硬件切换到功耗较低的 ASPM 状态(L0s 或者 ASPM L1)。

另外,软件还可以将链路设置为其它的一些特殊状态:Disabled,Loopback 或者 Hot Reset。

1. Detect 状态

当 PCIe 链路被复位或者数据链路层通过填写某些寄存器之后,LTSSM 将进入该状态。

当 PCIe 链路进入该状态时,发送逻辑 TX 并不知道对端接收逻辑 RX 的存在,因此需要使用 Receiver Detect 识别逻辑判断对端接收逻辑 RX 是否可以正常共工作,之后才能进入其他状态。那么TX怎么去判断对端设备呢?

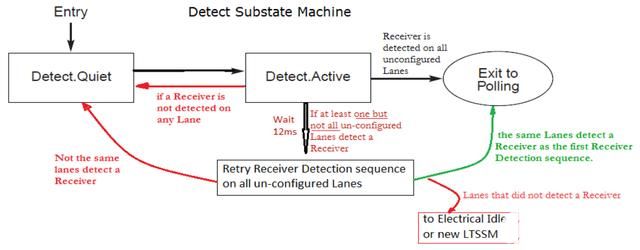

如下图,Detect状态包含了两个子状态:Detect.Quiet和Detect.Active

2. Polling 状态

当 PCIe 链路进入该状态时,将向对端发送 TS1 和 TS2 Ordered Sets(2.5 GT/s),并接收对端的 TS1 和 TS2 Ordered Sets(2.5 GT/s)。

通过接收到的 TS1 和 TS2 序列,完成如下操作:

获取 Bit Lock

获取 Symbol Lock 或者 Block Lock

如果需要,纠正 lane polarity inversion(差分信号极性反转)

检测支持的速率

PCIe 链路处于该状态时,将进行 Loopback 测试,确定当前使用的 PCIe 链路可以正常工作。

3. Configuration 状态

发送逻辑 TX 和 接收逻辑 RX 继续以 2.5 GT/s 的速度交换 TS1 和 TS2 Ordered Sets,完成如下任务:

确定 Link Width

指定 Lane Number

根据需要,对 Lane reversal 进行检查并对其进行纠正

处理 Lane-to-Lane 时序的偏差

Configuration 状态下,scrambling 可以关闭,该状态可以切换到 Disabled 状态或者 Loopback 状态。

在 TS1 和 TS2 中,还指定了 L0 状态切换到 L0s 状态所需要的 FTS Ordered Sets 的个数。

4. L0 状态

L0 状态是 PCIe 链路的正常工作状态。该状态下,PCIe 链路可以正常发送和接收 TLP、DLLP 和 Ordered Sets。如果需要切换到高于 2.5 GT/s 的速度传输,则需要进入 Recovery 状态进行链路重训练(Re-Training)。

5. Recovery 状态

PCIe 链路需要进行重训练(Re-Training)时会进入该状态,可能的原因有:

L0 状态出现错误

从 L1 状态切换到了 L0 状态

从 L0s 状态切换到了 L0 状态,但是使用 FTS 流程并没有将链路训练到可用状态

在 Recovery 状态,重新建立 Bit Lock 和 Symbol/Block Lock 的过程与 Polling 状态相似,但是要比 Polling 状态花的时间更短。

6. L0s 状态

L0s 是 ASPM(Active State Power Management)机制提供的第 1 级低功耗状态,该状态可以在较短的时间内切换到 L0 状态。当设备要从 L0 状态切换到 L0s 状态时,需要向外发送 EIOS。当设备要从 L0s 状态切换到 L0 状态时,需要向外发送多个 FTS,从而快速获取 Bit Lock 和 Symbol/Block Lock。

7. L1 状态

L1 是 ASPM(Active State Power Management)机制提供的第 2 级低功耗状态,它的功耗比 L0s 低,但是需要更长的时间才能切换到 L0 状态。想要进入 L1 状态,位于 PCIe 总线两端的设备需要进行协商,然后同时进入 L1 状态。两种可能的方式如下:

ASPM 机制下硬件自动切换。当 Upstream Port 的硬件发现没有 TLP 或者 DLLP 需要再发送的时候,就会自动和 Downstream Port 进行协商进入 L1 状态。如果 Downstream Port 同意,则二者同时进入 L1 状态;如果 Downstream Port 拒绝,则 Upstream Port 会进入 L0s 状态。

电源管理软件通过命令将设备配置为低功耗状态(D1,D2,D3hot)。此时 Upstream Port 和 Downstream Port 上的设备同时进入 L1 状态。

8. L2 状态

L2 状态是ASPM(Active State Power Management)机制提供的第 3 级低功耗状态,此时设备的主电源被关闭,从而达到更低的功耗。该状态下,几乎所有的逻辑都被关闭,只有一小部分使用 Vaux 供电的逻辑在工作,该部分逻辑可以用来发送 wakeup 事件。

支持 wakeup 功能的 Upstream Port 能向外发送一个低频信号,该信号称为 Beacon。Downstream Port 将 Beacon 信号转发给 Root Complex。通过 Beacon 或者 WAKE# 引脚,设备可以要求系统恢复它的主电源供电。

9. Loopback 状态

该状态是用来测试的,但是协议并没有明确规定 Receiver 在该状态下做些什么。基本的操作很简单:设备 A 作为 Loopback Master,连续对外发送两个 TS1 Ordered Sets,并且 TS1 的 Training Control 区域的 Loopback 位需要设置为 1。设备 B 接收到连续两个 Loopback 位为 1 的 TS1 之后,就会进入 Loopback state,称为 Loopback Slave。Loopback Slave 会将收到的所有内容再发送给 Loopback Master,从而形成回环,验证链路的完整性。

10. Disable 状态

系统软件可以通过设置寄存器,使 PCIe 链路进入 Disabled 状态。当 PCIe 链路的对端设备被拔出时,LTSSM 也需要进入该状态。

该状态下,发送端设备处于 Electrical Idle 状态,接收端设备处于低阻抗状态。对于链接已经变得不可靠或者设备被意外移除时,这种状态很有必要。

系统软件配置 Link Control register 的 Disable 位之后,该设备会对外发送 16 个 TS1 Ordered Sets,这些 TS1 的 Training Control 区域的 Disable Link 位需要设置为 1。接收设备在收到这 16 个 TS1 之后,进入 Disabled 状态。

11. Hot Reset 状态

系统软件将 Bridge Control register 的 Secondary Bus Reset 位设置为 1 之后,Bridge 的 downstream port 会对外发送多个 TS1 Ordered Sets,这些 TS1 的 Training Control 区域 Hot Reset 位必须被设置为 1。接收设备收到连续 2 个这种 TS1 之后,必须对设备进行复位。

当处理器系统进行 Hot Reset 操作时,PCIe 链路将进入 Recovery 状态,然后进入 Hot Reset 状态进行 PCIe 链路的重训练。

-

PCIe

+关注

关注

15文章

1238浏览量

82639 -

状态机

+关注

关注

2文章

492浏览量

27538

发布评论请先 登录

相关推荐

Simulink中的状态机建模方法 Simulink数据可视化与分析功能

基于Pytorch训练并部署ONNX模型在TDA4应用笔记

如何在FPGA中实现状态机

关于SMU状态机的问题求解

请问STM32F051用了操作系统RTX后还需要写状态机不?

在Verilog中实现Moore型和Mealy型状态机的方法简析

关于FX3使用4个线程进行FPGA到USB的数据传输-状态机设置的问题求解

请问GPIF状态机的内部信号需要延迟才能断言吗?

什么是有限状态机?如何解决传统有限状态机「状态爆炸」问题?

Verilog状态机+设计实例

【桃子同学笔记4】PCIE训练状态机(LTSSM)基础

【桃子同学笔记4】PCIE训练状态机(LTSSM)基础

评论