直接比较为半导体技术提供的总体性能数据有时会产生误导。在温度等动态条件下,Rds(on) 等参数的可变性表明情况更为复杂。

我们生活在一个一切都在四个维度内相对连续运动的世界。支持弦理论的物理学家可能会对此进行扩展,认为我们可以同时存在于至少十个维度中,如果包括时间,则可以在十一个维度中存在。然而,从工程师的角度来看,特别是在评估半导体时,感兴趣的维度是时间;设备在动态电气条件和外部影响(例如工作温度变化)下的功能如何。

数据表提供的主要性能数据通常是针对“典型”温度给出的,通常在脚注中定义,并且始终为 25°C。虽然这不太现实,特别是对于功率半导体,但这种做法是整个行业的标准。但是,它至少可以在竞争设备之间进行初步比较。其他有用的品质因数 (FoM) 结合了在实际应用中很重要的特性。一个例子是 RdsA,它是晶体管的导通(或漏源)电阻 (Rds) 和芯片面积 (A) 的乘积。非常低的 Rds 非常适合传导损耗,但如果以大芯片面积为代价,则器件电容会变得更高,开关损耗也会增加。一个相关的 FoM 是 Rds*Eoss,它是 Rds 和开关能量损失的乘积。

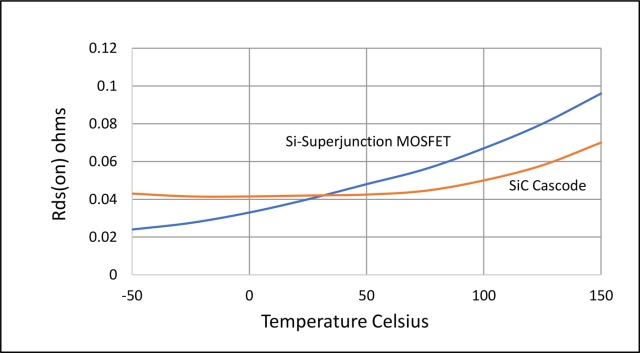

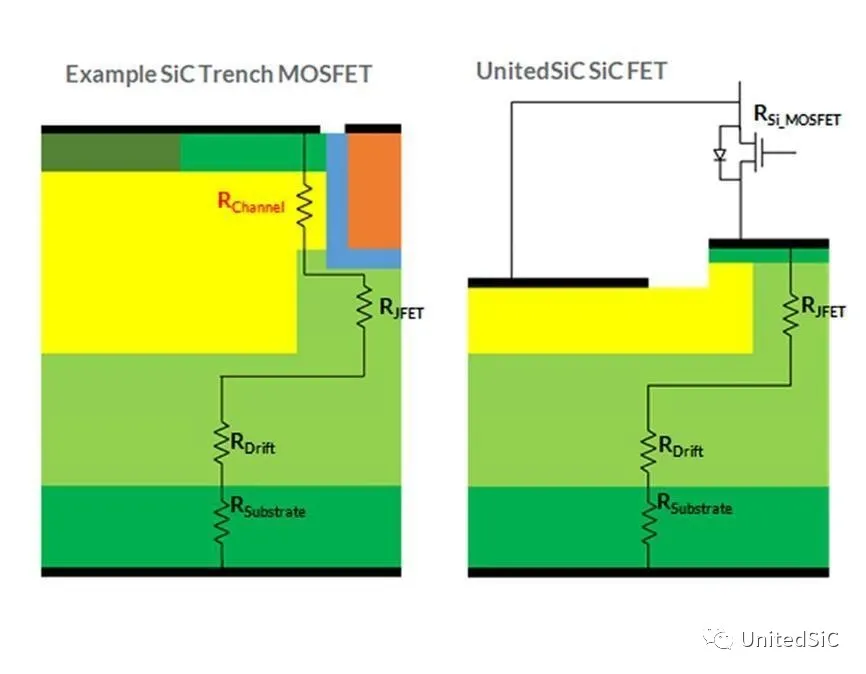

Rds(on) 和 Eoss 的值可以在器件数据表中找到,或者至少可以从器件数据表中找到,但实际上应该考虑温度的额外维度。例如,650V UnitedSiC UF3C065040B3 SiC 级联器件,它具有 Rds (on) 最大值为 52 毫欧(典型值为 42),可以与相同 D 2 PAK-3L 封装中的 650V 硅超结 MOSFET 进行比较,该封装的 Rds(on) 最大值为 45 毫欧(典型值为 40) . 在第一印象中,SJ 器件似乎更好,尤其是它在 25°C 时的最大漏极电流为 46A(而 SiC FET 部件仅为 41A)。但在 150°C 时,SJ 器件的 Rds(on) 值通常为 96 毫欧,而 SiC FET 部分约为 67 毫欧,而在 175°C 时仅为 78 毫欧(图 1)。

显然,在功率组件真正运行的较高温度下,SiC FET 器件的性能优于 SJ MOSFET。这不仅仅是器件评级方式的一个怪癖,而是 Si 和 SiC FET 材料之间的内在差异;在所涉及的掺杂水平(在 SiC FET 中通常高 10-100 倍)下,电子迁移率的下降速度会随着温度的升高而恶化。

图 1:碳化硅共源共栅的 Rds(on) 随温度的增加低于 SJ 共源共栅

这里的关键是,看似相似的部件在更高的温度下可能表现得截然不同,SiC FET 器件的较低传导损耗意味着它在 150°C 时比 SJ 部件消耗的功率少 30%。实际上,应用程序将定义电流水平,而不是开关中的功耗。这意味着对于给定的电流,由于 SiC 的热阻低于 Si,因此温度更低,因此 SiC FET 的性能有望优于 Si。SiC FET 较低的开关损耗和体二极管损耗也降低了整体封装耗散,从而提供较低的相对结温上升和仍然较低的相对 Rds(on) 值。考虑到 SiC FET 器件的较低栅极电荷和由此产生的节能效果,例如,具有较小的缓冲器,

选择半导体开关时,有必要研究数据表规格的详细信息——尤其是 Rds(on) 等关键参数如何随温度变化。这些额外的尺寸是它们在现实生活中运作的地方,考虑到碳化硅选项,可能会有一些惊喜等待工程师。

审核编辑:汤梓红

-

半导体

+关注

关注

334文章

26913浏览量

214789 -

碳化硅

+关注

关注

25文章

2687浏览量

48814 -

RDS

+关注

关注

0文章

101浏览量

16808

发布评论请先 登录

相关推荐

开关Rds(on)如何随温度变化

开关Rds(on)如何随温度变化

评论