1、信号串扰

串扰指的是在两条信号线之间的耦合现象。信号因为空间距离近的原因导致的信号线之间会出现不希望看到的电感性和电容性耦合从而互相干扰。电容性耦合会引发耦合电流,而电感性耦合则引发耦合电压。在电路设计中,是一个比较棘手的问题。

2、本文概要

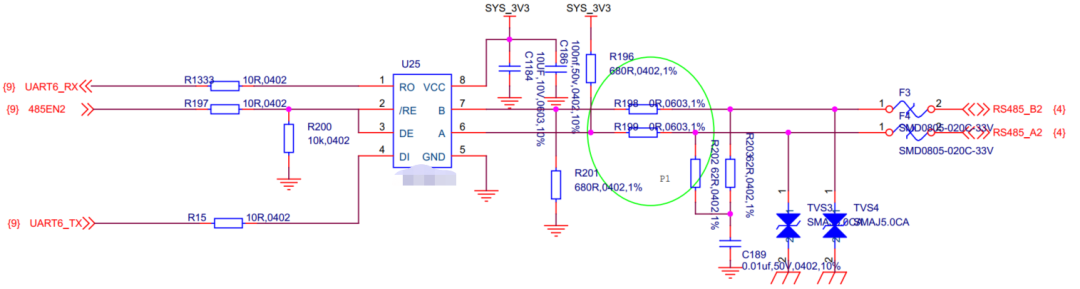

本文要解决的是RS485发送端波形噪声干扰大的问题,如下图1所示是其原理图,RS485的发送,接收,使能控制引脚通过一个10R电阻分别直接连接到MCU端口上。这个电路是目前市面上比较常用的RS485方案,具体的实现方式如下:

在空闲期间,485EN为低电平,MCU处于接收状态;在准备发送数据之前,MCU会先拉高485EN,U25处于发送状态;发送完毕之后,485EN重新处于低电平,U25处于接收状态。此方案的关键是要掌握好控制485EN引脚的高低的时机,否则会有丢包问题。

图 1RS485 典型应用原理图

3、问题发现及解决过程

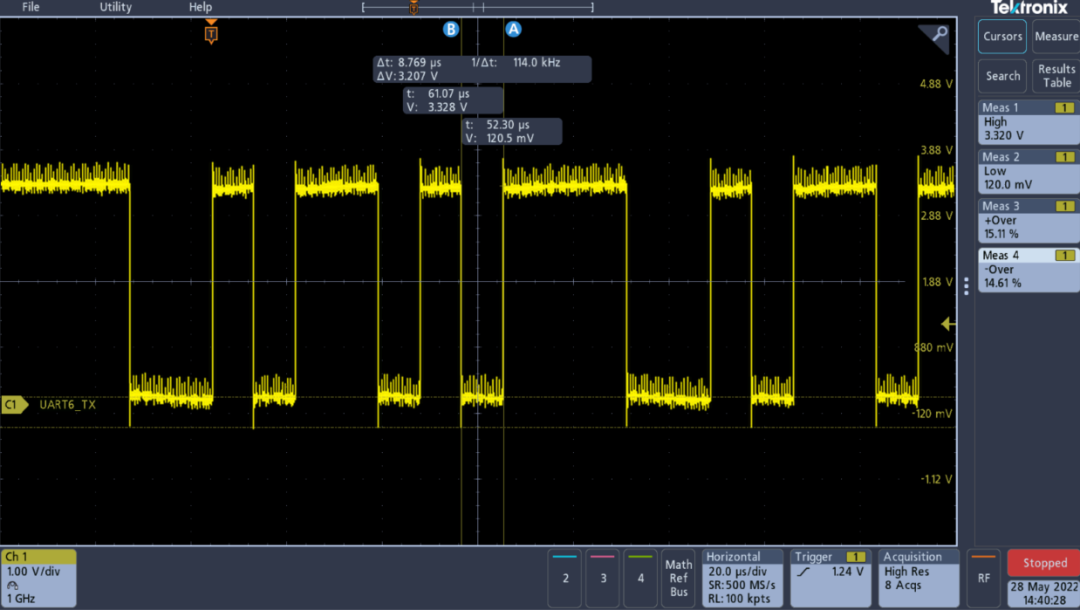

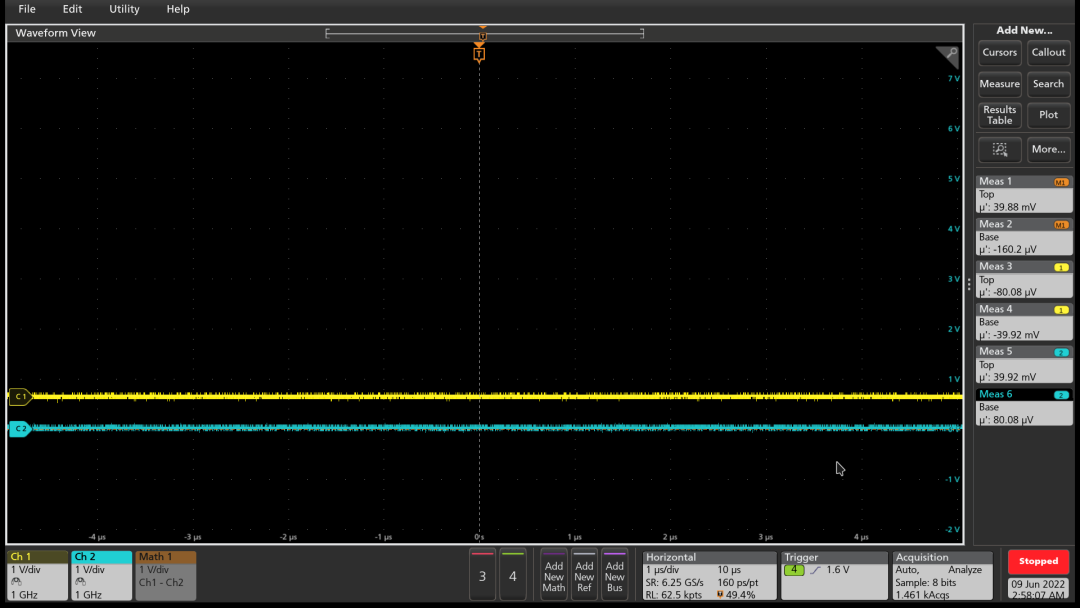

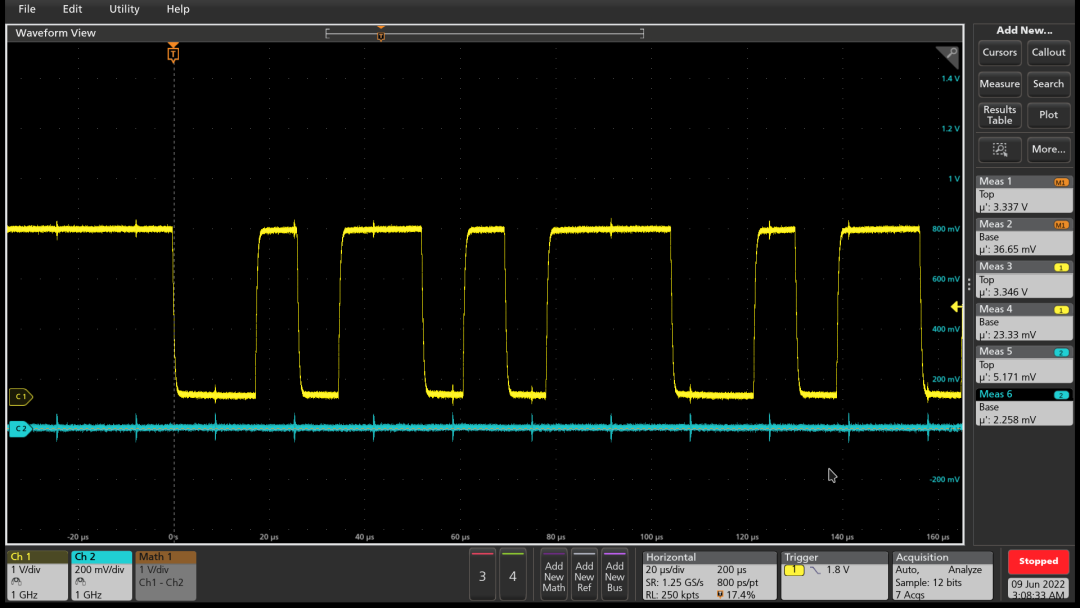

硬件测试时发现发射端DI的波形如下图2所示,在信号上有很大的毛刺(电阻R15前后都一样),测量另外一路同样的RS485电路就不会有这种问题,分析电路原理上是不会有问题的,怀疑是这路信号被其他信号干扰了。

图 2RS485发射引脚DI(UART6_TX)的波形图

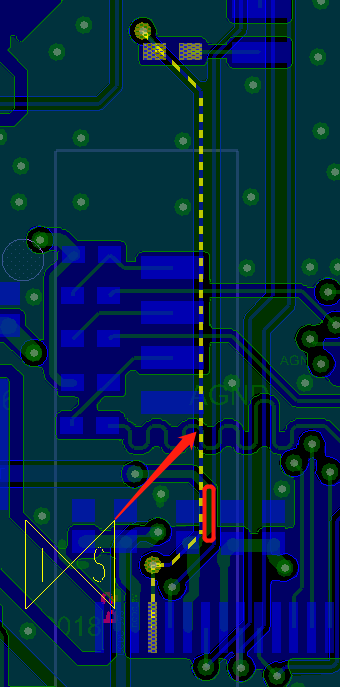

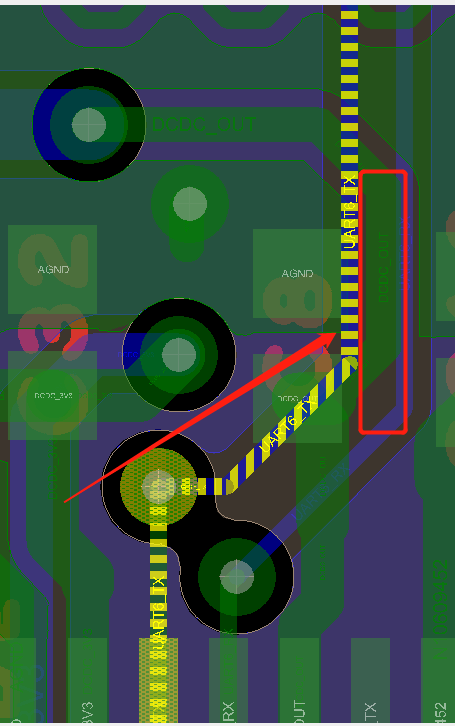

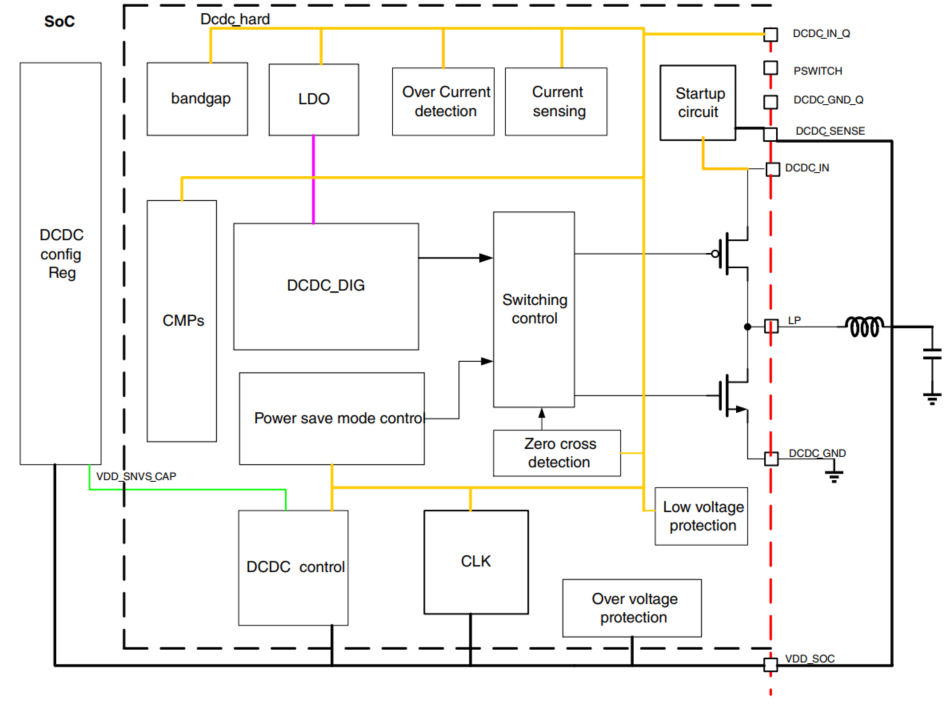

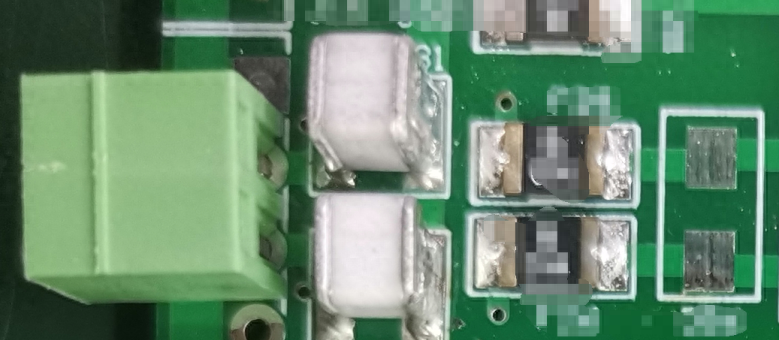

打开PCB图,找到UART6_TX这根线对应的PCB走线图,如下图3、图4所示。我们可以看到这根线从MCU出来后通过过孔到第三层,然后径直往上,在上面通过过孔回到第一层,然后通过R15电阻接入RS485芯片的DI引脚,整个路径除了和第一层的DCDC_OUT这根线有一段短距离的平行布线之外,其余还算干净。查看DCDC_OUT信号,发现DCDC_OUT是MCU的内核电压,系统选用的MCU内部含有PMU单元,内部DCDC单元是其中的一部分,其框图如下图5所示。考虑到buck芯片的强干扰影响,猜测是内核DCDC输出布线对UART6_TX造成的耦合干扰。

图 3UART6_TX走线路径图

图 4UART6_TX与DCDC_OUT平行走线部分

图 5 DCDC block diagram

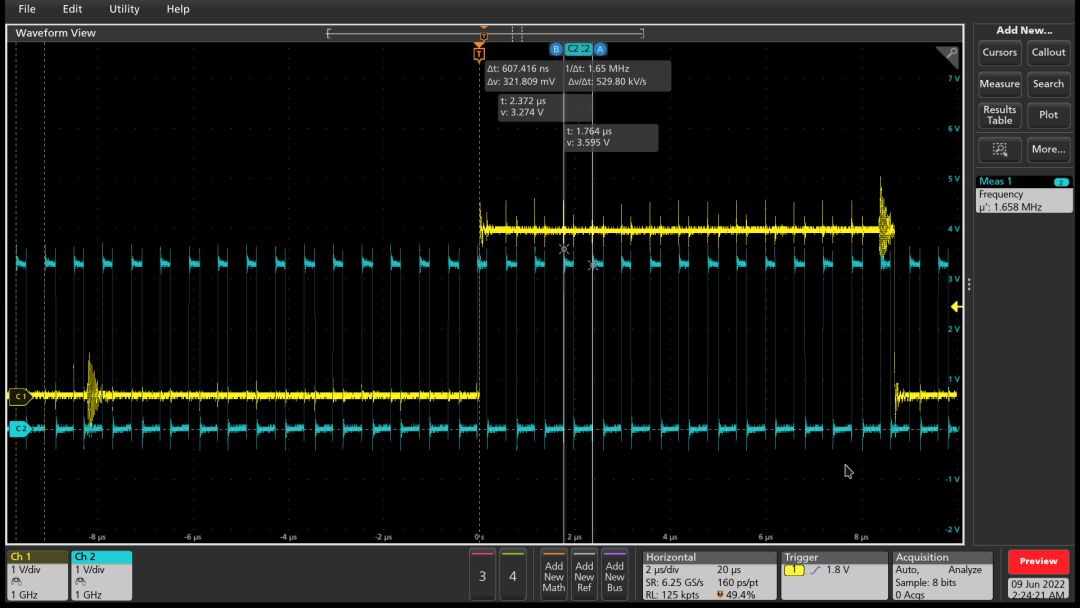

同时监测RS485发送引脚波形DI与LP点(图5框图中电感前)的电压波形,如下图6所示,可以发现,干扰的频率与LP处频率基本一致,基本可以判断是芯片内核电源buck芯片的平行输出布线耦合到RS485 DI引脚上去的。

注:黄色代表RS485上波形、LP处波形

图 6 发送端DI与LP处波形

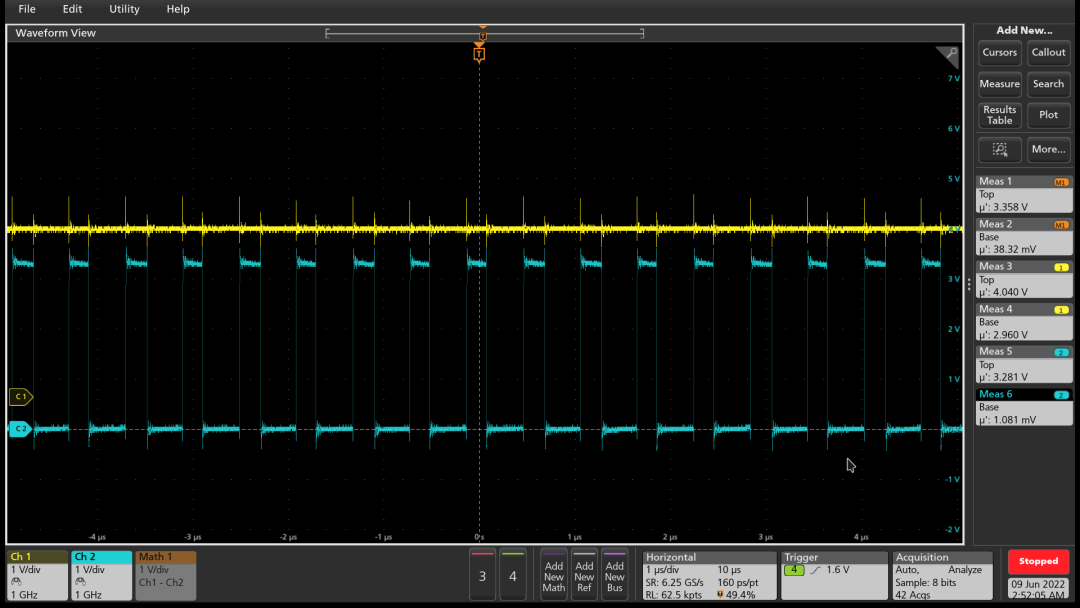

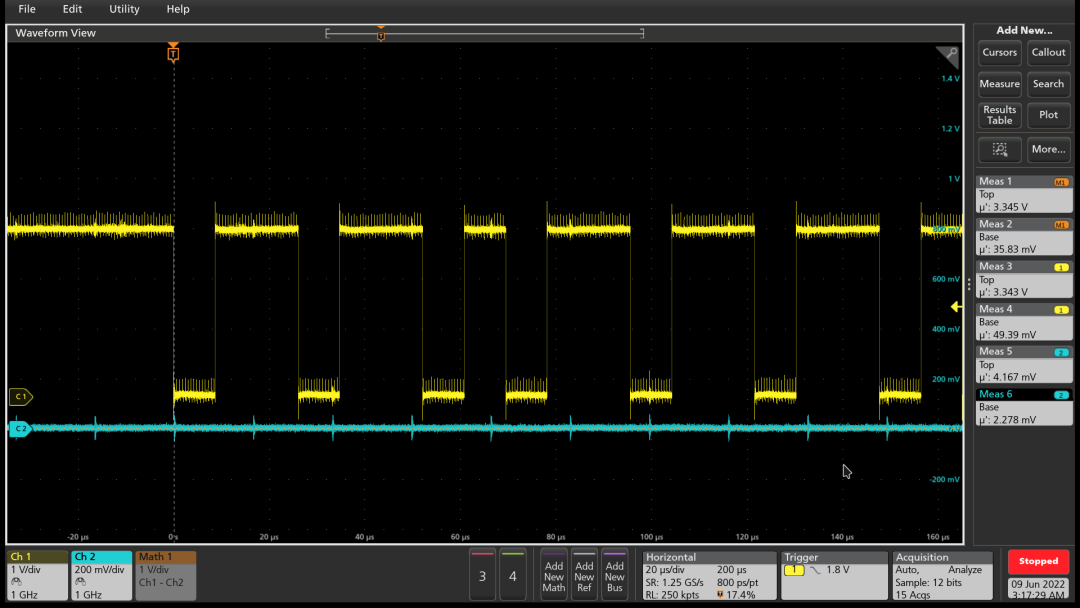

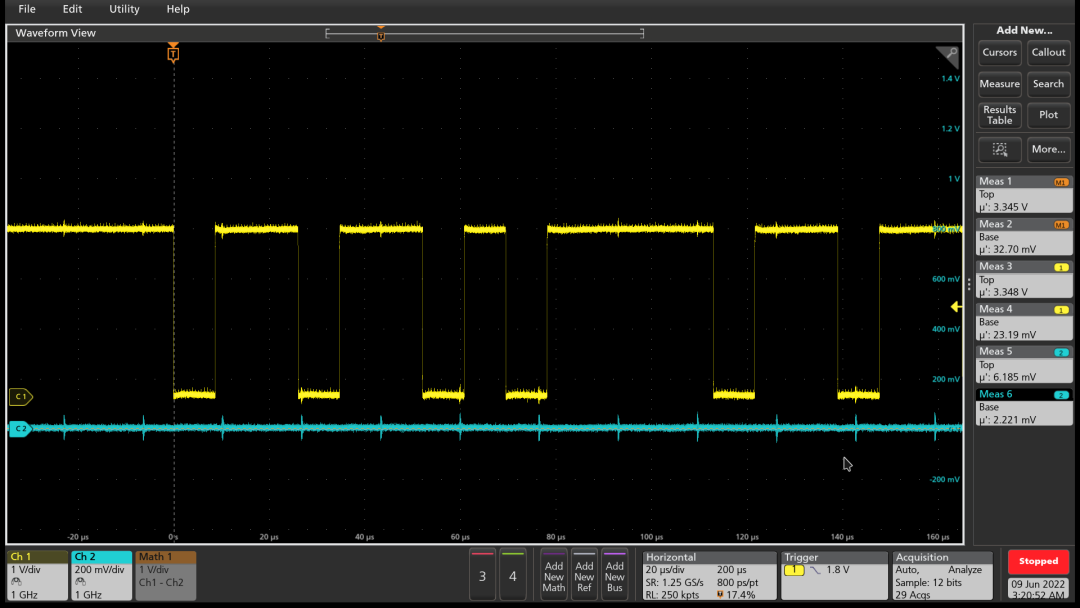

那有人说了,这样判断是不是有点草率了?有没有可能是RS485芯片部分的接收到其他地方的干扰传导前面发射端的呢?好的,那我们再来验证一下:我们先把R15电阻断开,然后观测靠近MCU端的波形和LP点输出电压波形,如下如7所示,发现断开R15后,干扰波形依然存在,测量DI端波形,如下图8所示,波形无干扰。因此,基本确定干扰由前级DCDC_OUT与UART6_TX平行布线部分串进来的。

图7 R15断开后测量的MCU端与LP处波形

图8R15断开后测量DI端波形(黄色)

4、解决方法

原因找到了,那么如何去除干扰呢?

1、布线的时候将这段平行布线改掉,避免平行布线或拉远布线间距;

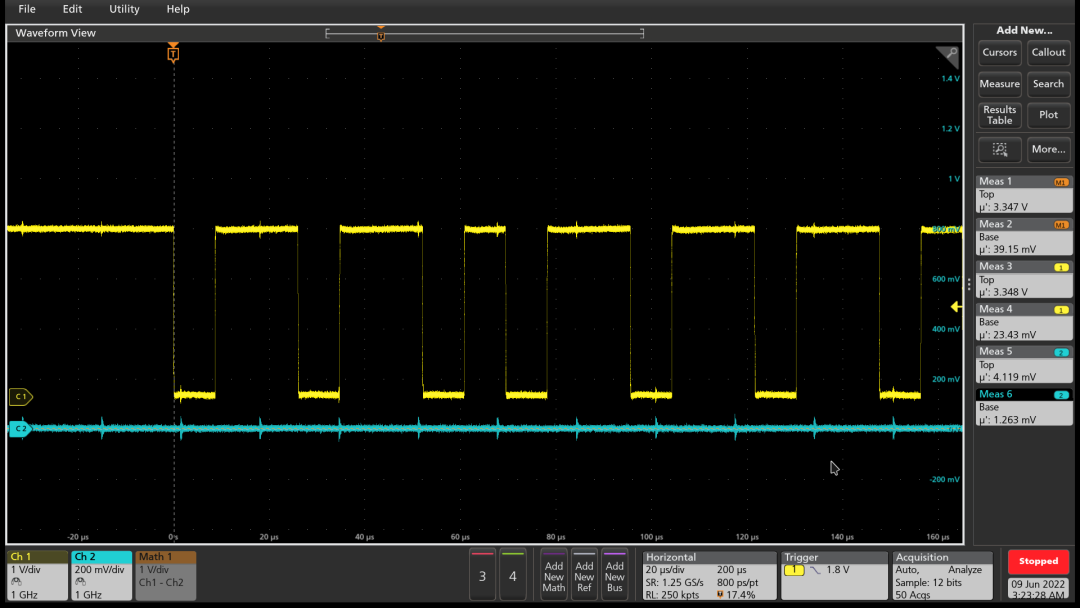

2、RS485发送DE引脚加一个小电容滤除噪声,因为噪声频率在1.65MHz,RS485频率最大110k,频率相差比较大,好滤除。如下是在DI引脚处添加不同容值的电容时的测试波形图,考虑到既要去除干扰又要保证信号波形上升下降沿的质量,因此最终选择用1nF电容。

图 9 22pF时DI引脚波形图

图 10 220pF时DI引脚波形图

图 11 1nF时DI引脚波形图

图 12 10nF时DI引脚波形图

审核编辑:汤梓红

-

噪声

+关注

关注

13文章

1115浏览量

47351 -

RS485

+关注

关注

39文章

1135浏览量

82104 -

信号串扰

+关注

关注

0文章

15浏览量

8571

原文标题:实例讲解:RS485发射端串扰问题如何解决?

文章出处:【微信号:hjldws,微信公众号:硬件微讲堂】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

RS485发送数据的时候,AB线上同时在发送数据,B线上的数据是错误的为什么?

RS485转以太网的应用、解决方案和关键技术

关于RS485通信信号问题

rs485总线通信故障。当接受串口关闭时候,串口发送数据时rs485总线出现途中干扰是什么原因?

RS485通信网络的EMC解决方案

RS485简介

RS485是什么?RS485通信的特点有哪些

MCU中RS485接口设计资料分享

我用stm32通过RS485发送数据到串口,串口收到数据是乱码是怎么回事啊?

RS485发送时,影响其他串口接收?为什么呢?

STM32F103ZET6基于RS485发送接收简单例程

RS485的实际应用和维护RS485的常用方法

为什么需要485隔离?常见RS485隔离方案介绍

RS485发送端波形噪声干扰大的解决方案

RS485发送端波形噪声干扰大的解决方案

评论