修复关键路径时序一直都是数字IC designer最耗时的工作任务之一,而且伴随着同一个RTL设计应用于不同的业务场景,时序、面积和功耗的约束也是不同的,所以时序优化的方向也是多变的。

简单来说,时序优化的任务是常见的,并不是说RTL写得足够好,就不存在后续的时序优化迭代。

本文介绍3个时序优化的RTL改动以及在其中Formal SEC的角色。

其中一种比较常用的关键时序修复方法是将两个pipe之间的组合逻辑重新分配。

这个道理就是木桶原理,限制同步设计时钟频率的路径就是关键时序路径,如果一个木桶中所有的木板长短都是一样的,那就是没有短板,或者说全部都是短板。

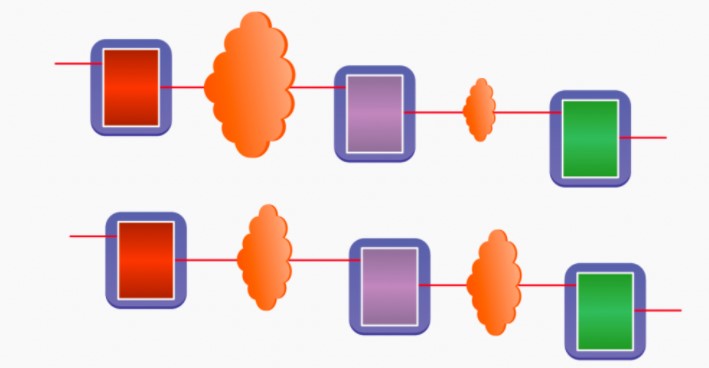

如上图所示,上方的设计是存在时序问题的设计,在第1个PIPE和第2个PIPE之间有一个比较长的组合逻辑,通过组合逻辑重新分配,让组合逻辑在2个PIPE比较均匀地分配就可以优化这类时序问题。

注意:前提是保证端到端功能是一致的,即使中间阶段寄存器的状态可能不一致。由于中间寄存器的状态不一致所以不能够使用combinational FEV,只能使用sequential FEV或者transaction FEV。

经验表明,这种时序优化有非常非常大的概率引入bug。修复时序的前提的保证功能,方向错误,跑得越快,越不是好事情。

这种由于修复时序引入的bug很容易通过修改前RTL(SPEC RTL)和修改后RTL(IMP RTL)之间的等价性(sequential FEC)比对来确保设计的时序优化修改没有引入新的bug。

critical path reduction

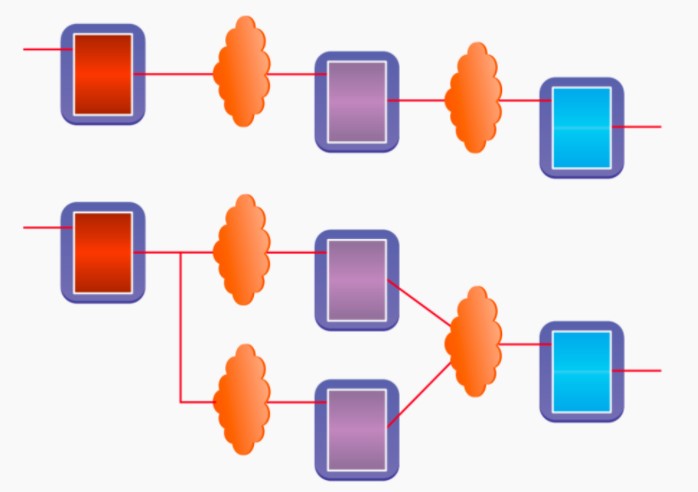

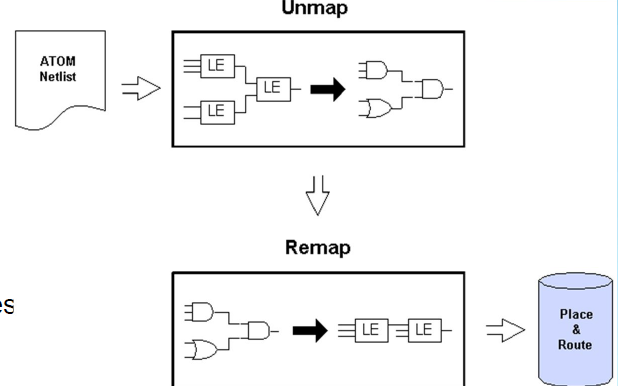

在某些情况下组合逻辑重分配不可行时,可能需要将一个比较长的组合逻辑分拆成并行的2个比较小的组合逻辑,然后在后面的PIPE使用逻辑再汇聚在一起,如下图所示。

对于上面的修改,上方的设计存在时序问题,下方的设计是优化后的问题,这个转化的过程同样非常非常容易导致bug的引入,也同样可以通过FEC来保证。

Pipeline optimizations

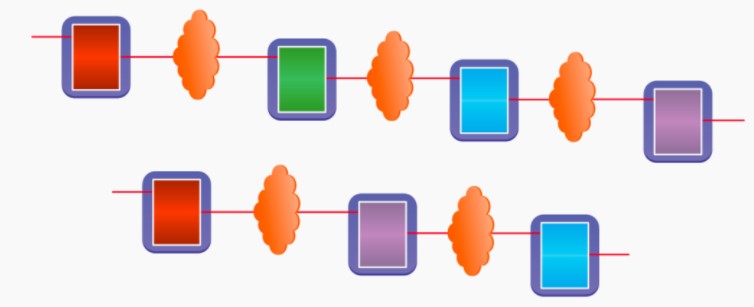

随着这个RTL设计的不同应用场景需求变化(工艺变化、业务场景变化、算法变化以及物理实现的变化等等),designer发现时序无论如何也无法优化,只能够以牺牲latency的代价增加pipe数来优化时序。又或者发现可以减少pipe来优化latency,提升芯片的局部性能。

注意:同样需要保证端到端的功能一致。

如上图所示,上方是优化前的设计,下方是优化后的设计(减少了一个pipe)。

对于这种pipe个数变化,但是端到端功能不变的修改,同样可以使用sequential FEC来进行等价性比对。只不过有所区别的是,需要指定比对是latency差异。

审核编辑:刘清

-

寄存器

+关注

关注

31文章

5334浏览量

120211 -

RTL

+关注

关注

1文章

385浏览量

59752 -

数字IC

+关注

关注

1文章

38浏览量

12543

发布评论请先 登录

相关推荐

进行RTL代码设计需要考虑时序收敛的问题

优化 FPGA HLS 设计

FPGA中的I_O时序优化设计

推荐一个时序优化的软件~~

vivado:时序分析与约束优化

介绍RTL设计引入的后端实现过程中的布线问题

你知道RTL时序优化迭代的技巧有哪些吗

A Roadmap for Formal Property

如何降低面积和功耗?如何优化电路时序?

可以通过降低约束的复杂度来优化Formal的执行效率吗?

Formal Verification的基础知识

介绍3个时序优化的RTL改动及其中Formal SEC的角色

介绍3个时序优化的RTL改动及其中Formal SEC的角色

评论