许多系统设计,包括工业机械、医疗设备和汽车,都对安全至关重要,需要能够实时检测自身的操作故障,并以一种避免伤害使用它们的人的方式做出反应。因此,创建一个基于处理器的系统来提供这种功能安全需要结合使用硬件错误检查、硬件自检和系统冗余来提供这些系统所需的独立于软件的故障检测和安全解决方案。幸运的是,有可用的处理器可以处理安全关键系统所需的大部分硬件繁重工作。

基于处理器的系统对功能安全的需求正在上升,尤其是在汽车应用中。即使抛开自动驾驶汽车的整个发展趋势,汽车也越来越依赖微处理器来实现关键功能。防抱死制动系统、发动机控制和转向只是现在在处理器控制下具有重大安全意义的少数车辆功能。如果这些处理器中的任何一个犯了一个错误而没有被抓住,结果可能是致命的。

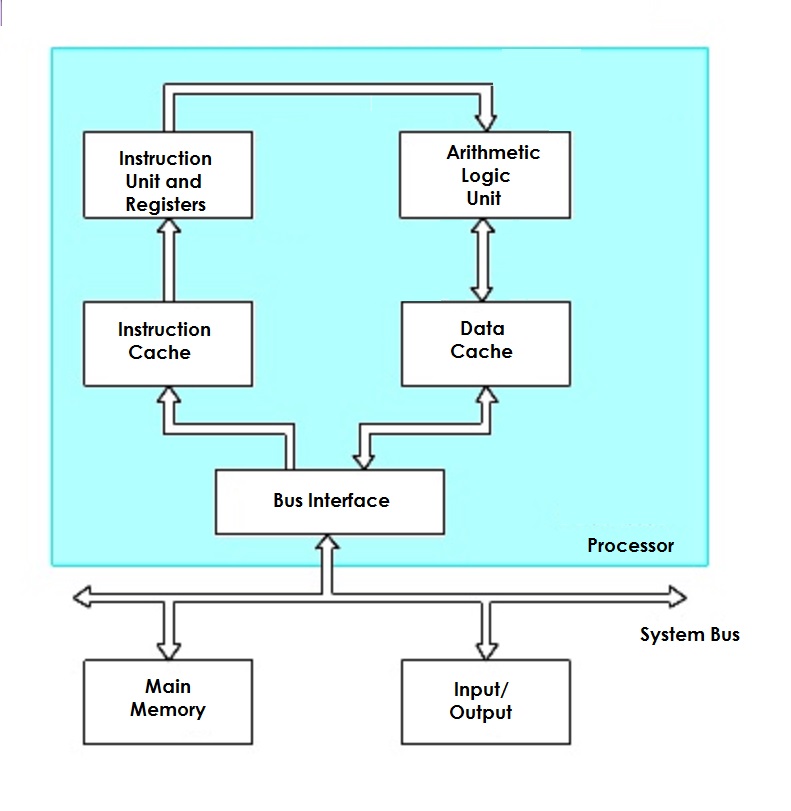

不幸的是,在基于处理器的设计中出现问题的机会很多。如下图所示,正确的代码执行需要许多系统元素才能正常工作。处理器及其所有内部寄存器、程序和高速缓存存储器、RAM 和它们之间的总线接口,以及系统电源和时钟,都必须以精确的时序完美运行。但正如任何无缘无故锁定计算机的人都知道的那样,系统中任何地方的任何一点变化都可能使整个操作脱轨。总线上任何线路上的噪声故障、杂散的阿尔法粒子或宇宙射线撞击(是的,它们确实发生,而且比人们想象的更频繁)改变内存或寄存器中的位、低电压、时钟漂移和许多其他来源可能会导致系统崩溃。

基于处理器的系统的核心为噪声毛刺和其他单一事件扰乱提供了许多机会,以完全破坏正确的软件执行。

通过精心设计,此类错误不太可能发生,但无法消除。因此,要使系统被认为是安全的,它必须能够实时检测到此类错误并做出适当的响应以减轻其影响。构成适当缓解的因素高度依赖于应用程序,但检测错误的方法已经成熟,并且在安全关键设计中很常见。例如,可以通过在每个事务中包含纠错编码 (ECC) 或循环冗余校验(CRC) 数据来监控系统总线上的事务。电压监视器可以监视电源,看门狗定时器可以帮助监视时钟信号。

看门狗定时器还可以通过让处理器定期重置定时器来提供正确的处理器操作的总体指示。如果处理器在该任务中出现故障,则一旦计时器用完,看门狗就会发送信号以提醒系统出现故障。然而,这涉及在频繁的定时器复位的软件开销和信号处理器故障的延迟之间进行权衡。

然而,检测故障只是功能安全的一部分。另一部分是以保持系统安全运行的方式对故障做出响应。此响应不能完全基于软件。您不能指望能够使用无法缓解自身问题甚至无法对警报做出反应的处理器。必须有一个独立的硬件机制。

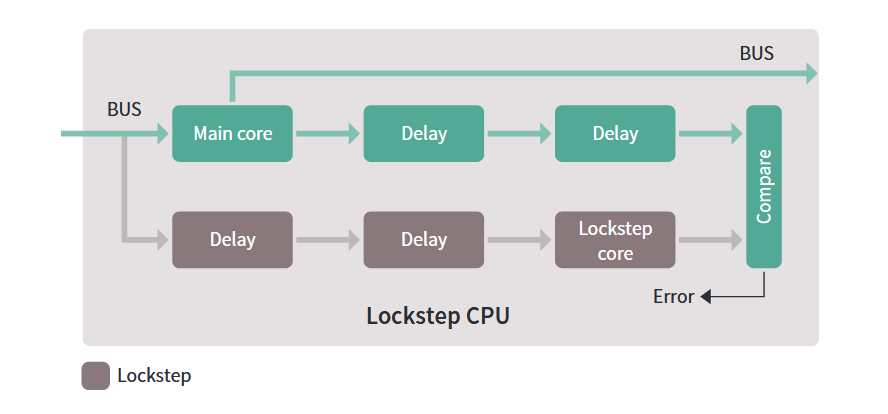

多年来,各种体系结构已经发展,以在基于处理器的系统中提供这种独立的机制。这些架构包括使用带有硬件检查器的单个处理器,以及使用具有相同或不同类型的第二个处理器作为主单元的两个处理器。第二个处理器可以独立运行,运行相同或独立的软件,作为逐周期验证主处理器行为的试金石。不过,更流行的替代方案是让第二个处理器与主单元同步运行,使用相同的代码和数据。但是,辅助处理器通常会在主处理器稍有延迟的情况下工作,以避免两个处理器都受到系统总线上的瞬态错误的影响。

已经开发了多种支持检测和缓解随机处理错误的架构。

这些架构的共同点是需要对基本处理器设计进行大量添加,包括比较硬件和可能的完整辅助处理器。多核处理器的出现为芯片供应商提供了一个机会,可以从系统开发人员那里卸下大部分硬件设计负担,许多人已经通过推出专为安全关键型应用设计的处理器来加紧努力。其中许多安全处理器主要面向根据ISO 26262标准进行 ASIL(汽车安全完整性等级)认证的汽车设计人员销售,但同样适用于工业控制、医疗、军事和航空航天领域的其他安全关键应用。

这些提供商不仅仅是提供硬件功能。他们还为设计人员提供实施安全设计、可追溯性和验证文档以及支持获得安全认证的开发工具和诊断软件库方面的帮助。

以下是目前市场上一些具有代表性的安全处理器系列:

ARMCortex R52:作为 ARM v8-R 架构的一部分,R52 内核为 ARM 被许可方提供了实现安全处理器所需的基础功能。双核器件可以在锁步模式下运行以进行故障检测,并可选择额外的分离配置,允许两个内核在需要时独立运行。核心设计还包括所有总线和内存接口上的 ECC,能够进行双位错误检测和单位错误纠正。此外,该内核还提供高覆盖率的内置自测试 (BIST) 功能和可许可的安全包,以简化产品安全实施。

InfineonAurix:Aurix 系列器件包含多达三个独立的内核,提供双锁步处理器,实现了额外的架构多样性。这两个内核运行相同的代码,但具有旨在减少出现常见原因错误的机会的硬件设计差异。设计差异有助于确保在主处理器上产生错误的事件不会在比较处理器上导致相同的错误。

英飞凌的 Aurix 锁步处理器设计使用延迟执行通用指令和数据流来避免未检测到单事件扰动。

英特尔至强 D-1529:英特尔的 D-1529 不是针对汽车应用,而是旨在满足IEC 61508安全集成级别 (SIL) 认证标准下的工业需求。该设计包括冗余锁步处理器对、窗口看门狗定时器、时钟和电源监视器以及处理器温度监控。这些处理器可以支持混合的安全关键和非关键任务执行,并在其 PCI 和 SATA 接口上提供诊断和错误检测逻辑。

MIPSi6500-F 内核:这种内核设计允许 MIPS 被许可人基于 64 位 CPU 的可配置集群创建安全处理器。它包括所有总线上的奇偶校验、RAM 上的 ECC 和逻辑 BIST 支持。它已被认证为 ASIL B 级的脱离环境 (SEooC) 安全元件,支持旨在获得 ASIL D 级认证的设计。

NXPS32S24:针对 ASIL-D 设计,S32S247 使用四个带有硬件管理程序的 ARM R-52 锁步内核来保持应用程序执行独立。大型(至 64 MB)集成闪存允许处理器保存多组应用程序代码以支持无线软件更新,并且所有存储器接口都包括 ECC。

STMicroSPC5:SPC5 产品线包括多种变体,包括锁步、延迟锁步和解耦并行处理选项。处理器包括带有 SPC57S 系列的 BIST 硬件,另外还提供内存上的 ECC。

Texas InstrumentsHercules:Hercules 系列安全处理器已通过使用锁步 Cortex-R 处理器的 IEC-61508 SIL 3 级和 ISO-26262 ASIL D 级认证。此外,它们还提供系统存储器上的 ECC、选定外设和 DMA 接口上的 ECC 或奇偶校验、串行和网络通信外设上的 CRC 或奇偶校验、片上时钟和电压监控、IO 环回和 ADC 自检以及存储器 BIST。错误信号模块提供了一个外部信号引脚,以促进对处理器内检测到的错误作出额外的系统响应。

XilinxZynq 7000:虽然它实际上不是处理器,但 Zynq FPGA 可以配置为在单个设备中提供两个独立的安全通道,使用经过认证可用于功能安全应用的设计包、方法和工具。这些工具包括对隔离设计流程的支持,这些流程在物理上分离冗余元件以防止使用 FPGA 资源,以及软错误缓解 IP 的可用性。

然而,选择安全处理器仅仅是开始。安全关键系统的开发人员仍需要对硬件和软件采用设计和评估方法,严格评估发生错误的可能性,并验证系统设计对此类错误的恢复能力。不过,以安全为目标的处理器及其供应商提供的支持在很大程度上减轻了开发人员的负担。

审核编辑:郭婷

-

处理器

+关注

关注

68文章

19329浏览量

230142 -

芯片

+关注

关注

456文章

50908浏览量

424486 -

cpu

+关注

关注

68文章

10873浏览量

212094

发布评论请先 登录

相关推荐

如何在多处理器系统中使用EMIF?

异构多处理器系统Cache一致性解决方案

基于NiosII的SOPC多处理器系统设计方法

用Xilinx的EDK工具构建MB处理器系统

处理器系统接口部件的设计

基于处理器的系统设计

基于处理器的系统设计

评论