通信、工业甚至嵌入式设计越来越需要更高性能的接口。诸如 DDR4 内存、10 Gigabit 以太网、PCIe、串行 ADC 和 DAC 接口等协议正在变得司空见惯。虽然这些高速接口通常出现在高端 FPGA 上,但对于大多数应用来说,这通常是一种过度杀伤的方法并且成本过高。使用低端 FPGA 也不是一种选择,因为它们不能提供必要的性能。

现在,部署这些接口的成本可以通过使用新型节能、中等密度的 FPGA 显着降低,这些 FPGA 经过成本优化,功耗更低,提供比更昂贵的 FPGA 更小的外形尺寸,同时仍然提供大量高- 速度接口选项。

应对新的市场动态

尽管各个细分市场是独一无二的,但它们也有几个共同点。对更高价值和更低成本的需求正在成为所有应用和细分市场的增长动力。此外,随着物联网 (IoT) 的出现,速度更快、数量更多的网络接口现在变得更加普遍。最后,大多数嵌入式设计中的高速处理是一种新规范。

这些因素要求架构包含千兆以太网等接口,以及足够快的收发器以支持 10 GbE、JESD204B ADC/DAC、PCIe 接口、HDMI 2.0b 和 DDR4 等内存总线,仅举几例。

既然这些类型的接口可用于成本优化、低功耗的中档 FPGA,设计工程师就有了重要的新选择来应对其产品的最新市场动态。其中最有价值的选项之一是能够在 FPGA 的通用输入输出 (GPIO) 引脚上使用串行千兆位媒体独立接口 (SGMII),而不必使用高速收发器。

在 GPIO 上利用 SGMII

在许多通信和工业设计中最常用的接口是千兆以太网 (GbE)。最常见的是,FPGA 通过串行 SGMII 接口连接到 PHY。过去,使用 FPGA 实现 SGMII 接口也需要使用高速收发器。这一切都随着新的成本优化的中档 FPGA 的出现而改变,这使得 SGMII 接口可以在通用 GPIO 引脚上使用,以实现 GbE 到 FPGA 链接的最低功耗实现。

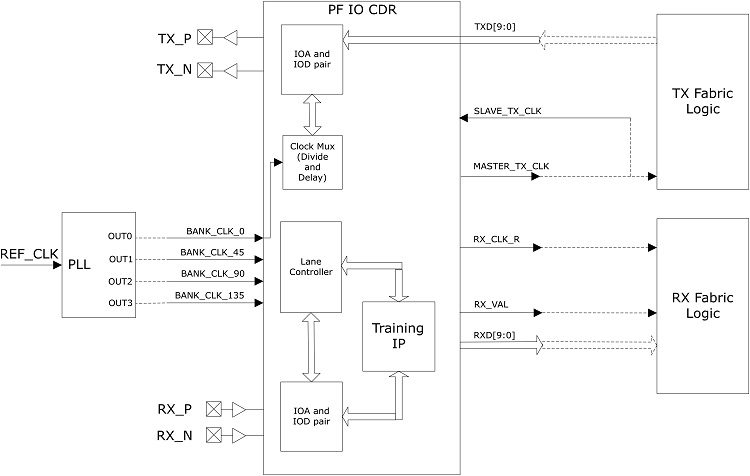

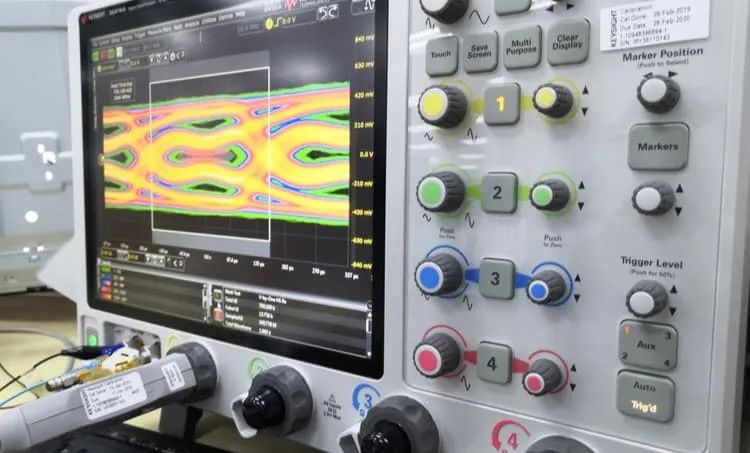

许多嵌入式产品开发人员使用 GbE 来实现越来越多的连接。这些链接不再仅适用于数据有效负载,而且在控制、管理、状态等方面变得无处不在。虽然低端和传统中端 FPGA 都可以支持这些 1-Gbps 速度,但它们需要收发器来实现 1.25-Gbps SGMII 接口以及其他高速接口。理想情况下,设备应具有专门分配的通用 I/O 引脚以支持 SGMII(图 1)。

图 1:传统和中档 FPGA 可以支持 1-Gbps 速度,但它们需要收发器来实现 1.25-Gbps SGMII 接口。

低端 FPGA 和传统中端 FPGA 没有这个特性,所以它们必须依赖收发器。以这种方式实现接口可能具有挑战性,因为这些收发器接口非常珍贵且经常稀缺。为了有足够的它们来满足更高性能的接口要求,设计人员以前必须选择更昂贵、更高密度的 FPGA 架构。

工业设计中通常不需要这些大型 FPGA 结构,但设计人员无论如何都被迫选择它们,只是为了拥有足够的额外收发器。此外,这些更大的设备意味着需要更大的封装尺寸。结果是工业市场需要相反的更高的功耗和成本。

当今的低功耗、成本优化的中档密度 FPGA 逆势而上,提供了一种通过 GPIO 上的 SGMII 满足众多千兆以太网链路要求的新方法。一些解决方案更进一步,将时钟和数据恢复 (CDR) 电路集成到可支持 1.25 Gbps 的高速 LVDS I/O 中。这些特性使器件能够在众多 GPIO 引脚上支持 SGMII 接口。与使用传统中端或高端 FPGA 创建的设计相比,使用这种架构,设计人员可以降低其设计的成本、尺寸和功耗。

平衡速度、成本和功耗

并非每个带有通信接口的设计都需要极高的性能,但在整个市场中,处理需求都在增加,而接口却越来越快。这些因素要求 FPGA 支持高达 12.5 Gbps 的串行接口,以实现以下越来越常见的选项:

PCIe Gen2 需要 5 Gbps

HDMI 2.0b,需要 6 Gbps

10 GbE 需要 10 Gbps

JESD204B,最高可运行 12.5 Gbps

这些高速串行接口要求收发器以上述速度运行,但功耗也应优化。对于基于高端架构的高端 FPGA 或中端 FPGA,这些速率的性能微不足道。不幸的是,这些设备也消耗非常高的功率,需要很大的外形尺寸,并且通常超出许多设计的预算。

另一方面,低密度 FPGA 通常没有收发器,并且包含它们的那些不支持列出的性能速率。平衡收发器速度、低成本和功率效率的答案是使用具有逻辑元件 (LE) 和收发器的正确组合的中等密度 FPGA,以支持所需的数据速率。

通过这些选项,工业架构师可以支持最新的高速串行接口,同时还拥有足够的片上 LE 来实现必要的电路板功能。此外,在 GPIO 和收发器上实现 SGMII 的能力通常使设计人员能够选择更小的封装尺寸和密度。这降低了系统成本并降低了 FPGA 功能所需的功率。

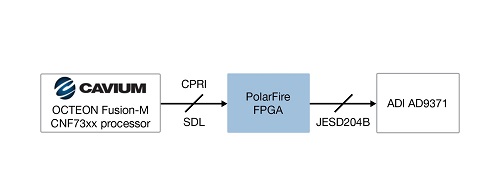

需要串行接口的一个例子是无线微蜂窝。这些设计通常使用处理器来处理大部分信号处理,同时利用 FPGA 进行自定义信号调节并连接到 ADC 和 DAC,如图2 所示。

图 2:串行接口设计示例。

在此示例中,FPGA 使用收发器实现 CPRI 或专有串行数字链路 (SDL) 到 Cavium 处理器,并通过 JESD204B 实现到 Analog Devices ADC/DAC 的串行链路。除了执行串行桥接功能外,FPGA 的结构还可以实现信号调理算法,例如波峰因数降低 (CFR) 和其他功能。该实施方案为小型蜂窝和微蜂窝应用提供了更低功耗的解决方案和更小的占位面积。

实现 DDR4 接口 的新方法

工程师倾向于连接到 FPGA 的最常见存储器是基于 DDR DRAM 的设备。有几代可供选择,最好的选择通常是使用已经出货一段时间且不是绝对最新标准的内存。

对于 DRAM,DDR4 提供最佳的每比特成本,并且其架构将被支持多年。尽管 DDR3 仍然是设计的可行选择,但大多数新设计都选择 DDR4,因为它将在未来提供更低的价格、更快的性能和更宽的单芯片数据总线。

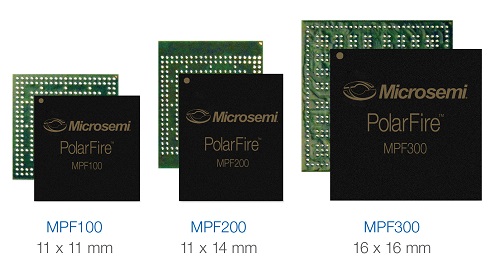

没有支持 DDR4 存储器接口的低密度 FPGA,因此设计人员必须使用基于高端架构构建的中等密度 FPGA 来实现这些接口。相比之下,当今最新的中端 FPGA 专为这些接口而构建,以显着降低的成本和功耗提供所需的 DDR4 性能,同时实现嵌入式设计所需的更小尺寸(图 3)。这些器件的封装尺寸范围从 16 x 16 mm 到 11 x 11 mm。

图 3:多种密度和外形尺寸的 FPGA。

随着通信、工业和嵌入式设计对更高性能接口、更多连接和更低成本的需求不断增长,系统架构师和工程师需要寻找新的解决方案。当今的低功耗、中等密度 FPGA 解决了这些设计挑战,将更大的价值与更低的功耗相结合,同时仍提供现代设计所需的接口选项和其他功能。

-

FPGA

+关注

关注

1625文章

21665浏览量

601776 -

接口

+关注

关注

33文章

8494浏览量

150821 -

GPIO

+关注

关注

16文章

1196浏览量

51906

发布评论请先 登录

相关推荐

高速ADC与FPGA的LVDS数据接口中避免时序误差的设计考虑

中端FPGA如何降低高速接口的成本

中端FPGA如何降低高速接口的成本

评论