这段时间,会翻一翻PCIe相关协议规范,看到不同章节不同地方会有关于SSC扩频时钟的内容,那就讲讲SSC扩频时钟。

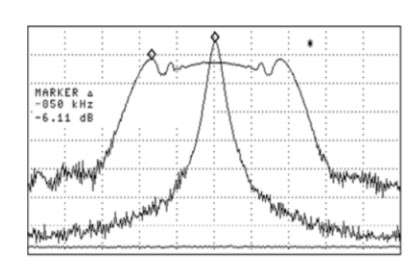

SSC,全称Spread Spectrum Clocking,即扩频时钟。由于信号的能量过于集中在其载波频率位置,导致信号的能量在某一频点位置处的产生过大的辐射发射。为了有效地降低EMI辐射,芯片厂家在设计芯片时也给容易产生EMI的信号增加了SSC扩频时钟的功能,频率变化的时钟,其频谱能量被分散在一定频谱范围上。当前PCIE、SATA、SAS、USB3.0等高速芯片都支持SSC的功能。采用SSC的功能可以有效的降低信号所产生的EMI。

说到扩频,会想到分频和倍频,也有过混淆的情况。分频和倍频说的是CPU与总线、外设之间工作频率的关系。为什么会有分频、倍频?是因为有些外部设备达不到CPU的工作频率,一般情况下,CPU的工作频率永远是高于外部设备的,为了协调CPU与外部设备的工作时序,就只有进行分频和倍频处理。

CPU的频率,即主频为外频与倍频两者的乘积。

SSC不仅对时钟振荡频率(基波)有抑制作用,对高次谐波(准确地说是基频的奇次谐波)的峰值也有抑制作用。

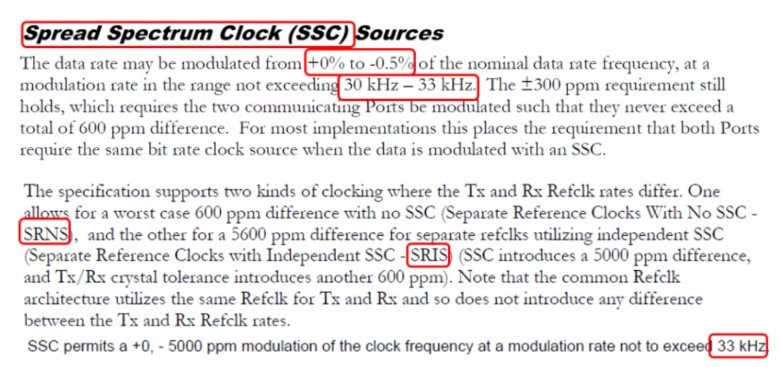

SRIS - Separate Refclk Independent SSC. 独立参考扩频;

SRNS - Separate Refclk with No SSC。独立参考无扩频;

SRNS允许600ppm,而SRIS允许5600ppm(其中SSC允许5000ppm,TX/RX允许600ppm);

一般芯片支持SRIS也会支持SRNS。

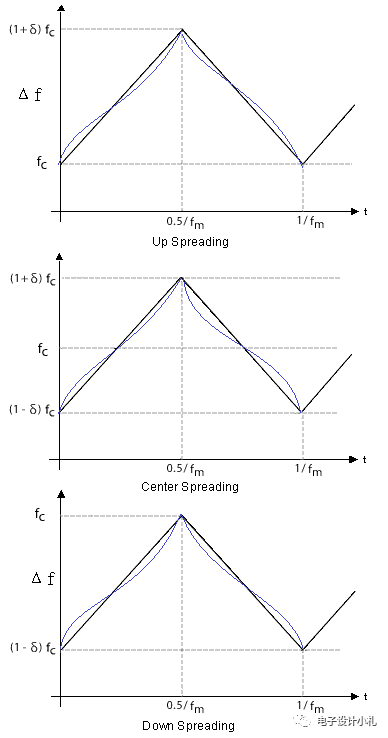

+0%~-0.5%这个说的是扩频类型。扩频类型有三种:中心扩频,向上扩频还有向下扩频。由于中心和向上扩频都会产生超过系统时钟的频率,会对系统造成影响,所以一般使用向下扩频。

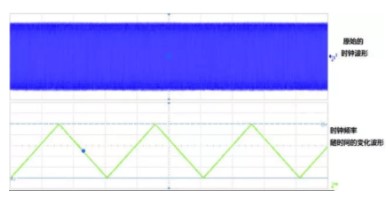

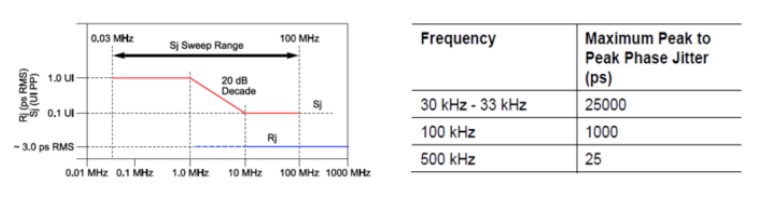

30KHz~33KHz这个说的是被调制信号频率范围内的变化速度。调制频率太快,后级的PLL电路可能跟踪不上,应远小于源时钟的频率,以免引起时序问题(建立/保持时间等);调制频率太慢,会产生人耳可识别的声音的频率范围(20Hz~20KHz)音噪。

在实际应用中,调制频率一般选择30KHz~33KHz。

后级PLL电路,这里扩充一些。

时钟展频只引入非常小的周期间抖动,当展频的时钟输出到下游的PLL时,此时PLL表现为低通滤波器,允许输入的低频部分通过,衰减其中的高频部分。扩频时钟输入PLL时,PLL可能出现无法锁住频率的问题。务必确保PLL必须能检测展频时钟的频率变化并允许展频时钟通过。以上取决于PLL的带宽,如果带宽太低,PLL可能无法可靠地侦测输入时钟,造成侦测偏差,给系统引入更大的Jitter。

PLL 受控变量通常是信号的相位。

一阶用于相位变量/ 状态,二阶是一阶的导数,即频率。

调制解调器之间任何载波频率偏移将始终产生恒定的相位滞后,只能通过二阶PLL来消除。

调制波形之前也说过,有正弦波,锯齿波,还有三角波等

三角波调制方式简单,调制后信号的频谱比较均匀,调制波形一般采用三角波。

PCIE串行总线3.0速率为8Gbps,规定扩展率为0~-0.5%,调制频率为30~33kHz,这样的要求不但满足了EMI的衰减要求,同时也为兼顾扩频时钟带来的周期抖动最小化的要求。

SSC是为了系统EMI问题,滤波和屏蔽的方法才是实际工作中常用的解决之道。SSC在实际工作中都是关闭状态。这里面有个问题,既然打开对EMI有利,其标准又符合相关抖动Jitter的标准,为什么不将其打开?

SSC也有资料给出时钟展频有三个主要的控制参数:调制速度(Modulation Rate)、调制深度(Modulation Depth)和调制方式(Modulation Profile),里面的理论和知识大同小异,这里就不做展开。

审核编辑:刘清

-

emi

+关注

关注

53文章

3582浏览量

127321 -

PCIe

+关注

关注

15文章

1217浏览量

82423 -

扩频时钟

+关注

关注

0文章

8浏览量

10585 -

ssc

+关注

关注

0文章

24浏览量

11172

发布评论请先 登录

相关推荐

无线扩频系统由什么组成

CDCS502带可选SSC的晶体振荡器/时钟发生器数据表

CDCS503带可选SSC的时钟缓冲器/时钟乘法器数据表

CDCE(L)949:支持SSC以降低EMI的灵活低功耗LVCMOS时钟发生器数据表

讲讲SSC扩频时钟

讲讲SSC扩频时钟

评论