1. 绪论

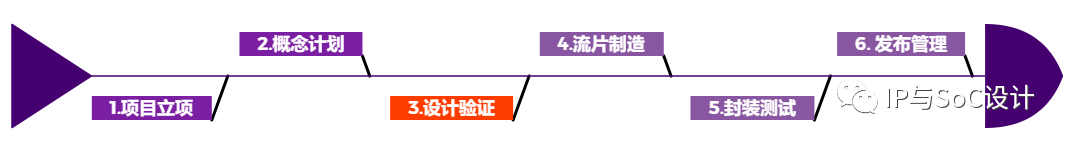

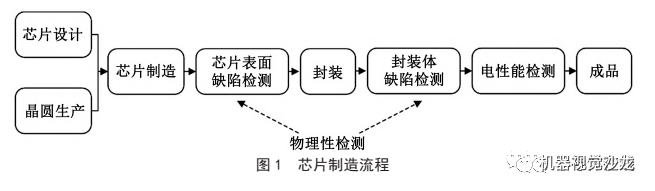

这个内容就挺多了,也可能是大家最关心的一个部分,可能要分几次讲。在整个流程中处于这位置。

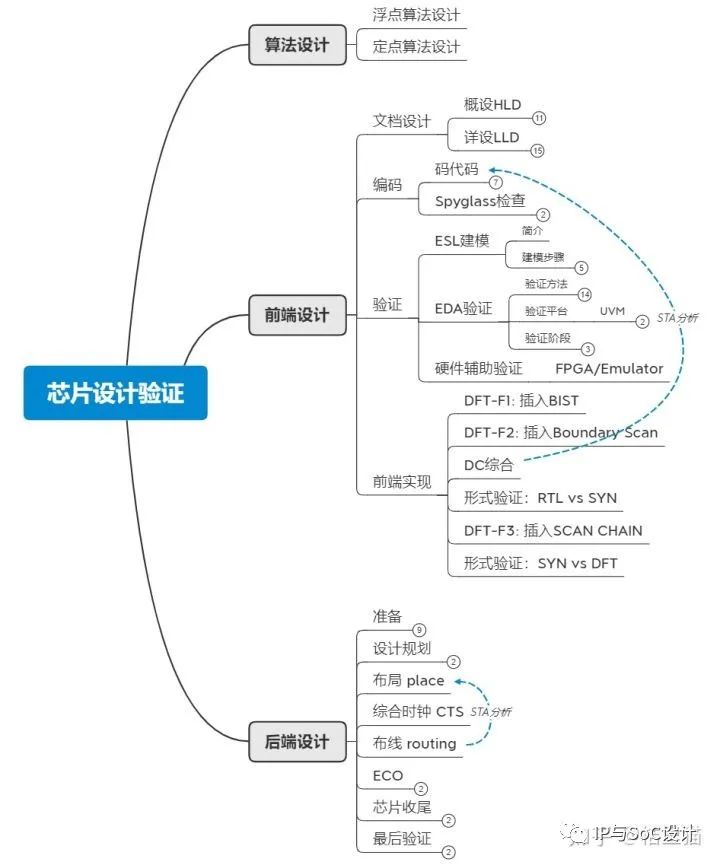

此处由于我自己还是对数字芯片系统更了解,所以按数字的来。模拟芯片的设计流程后续有精力或者请个大佬补个概述。芯片的设计流程还是比较长的,我们先来个birdmap。这个图很复杂,看不懂的名词不要慌,我会一步一步讲。

2. 算法设计

我们先来讲第一部分,这个部分其实比较简单。所以就在此处讲讲,后续不再单独开章节来讲这个东西。芯片最终还是算法的一种加速。如果一个东西你用C++都实现不了,芯片怎么可能实现。第一步就是算法。

算法实现其实有两个步骤的。为什么有两个步骤呢,这就涉及到浮点和定点的区别。浮点精读高,但是硬件实现代价大,定点成本低,硬件实现代价小。一般先设计浮点算法,然后再牺牲一点精度,搞成定点算法。

浮点算法设计浮点算法偏重于功能,由于浮点精度高,最原始的功能一般会用浮点实现。比如你要整一个AI芯片,你首先得用pytorch或者tensorflow训练出一个浮点网络,看看效果是不是还行,能不能实现网络正常的功能。算法链路先测试好了后续才能用芯片加速。浮点算法一般由纯软件工程师设计的。他们并不需要知道硬件实现,只需要对功能的正确性负责即可。

定点算法设计定点算法就是找个位置,把浮点中的指数为给归一了。精度是肯定会损失的,但是换来了硬件设计的简单。这个也容易理解,用芯片算一个3.5+0.025和用芯片算一个3500+25复杂程度完全不一样啊。为了平衡精度和定点位宽,此处定点化可以有各种门道,比如采用批处理的定点化,一部分数据采用一个定点位置,另一部分数据采用另一个定点位置等等。总之就是,这一步实现的是如何用最小的定点位宽,在精度可接受的前提下实现浮点的算法。

3. 前端设计

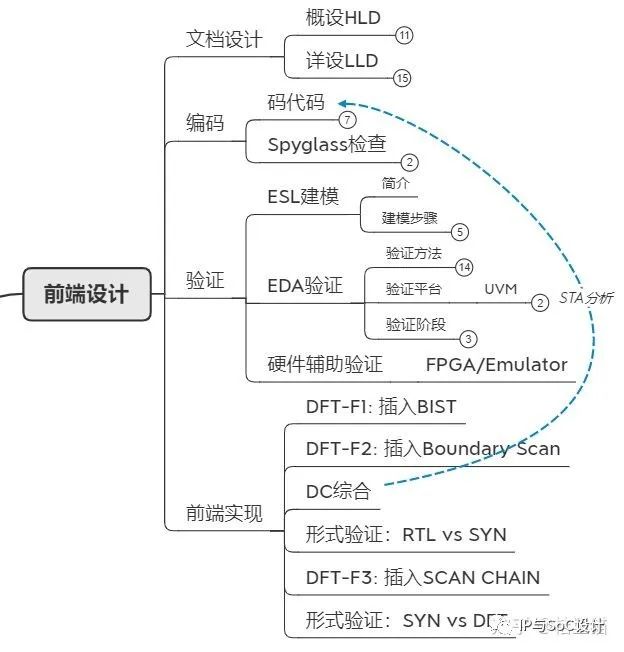

和其他一些复杂的东西类似,比如编译器,网站等等类似,芯片设计也有前端和后端之分,前端到网表,后端到版图。

前端主要包含4个步骤:文档设计、编码、验证、前端实现。主要就是从设计需求到网表的一个流程。

4. 后端设计

这个步骤,主要是把网表整成我们最后的版图。可以直接丢给代工厂生产了。

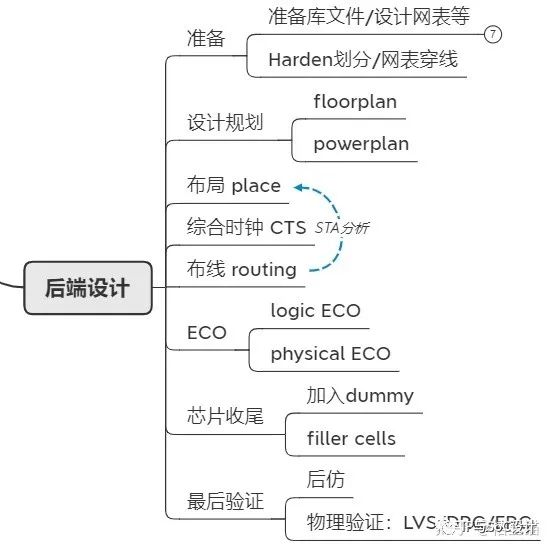

一共7个步骤。此处给个概述,后面专门写文章介绍。

准备:这一个步骤中准备主要是准备一些库文件,前端准备好的网表,划分好harden, 然后穿线。

设计规划:设计规划主要是摆放一些大件,比如memory硬核,IO PAD, 电源网络等等,方便下一个步骤摆放小单元。

布局:这个步骤就把具体的单元摆放到版图上。

综合时钟:把时钟网络摆放好,保证到各个地方的长度都差不多。

布线:真正把线联通。此处会通过STA,不断调整布局以及routing。

ECO:版图搞定后,需要工程师手动修一些东西。

芯片收尾:加入dummy, filler cells等等,让密度满足光刻需求。

最后验证:交芯片前,最后再验证一把。主要包含了后仿,形式验证,物理验证。

这7个步骤完成以后,就可以交版图给代工厂了,接下来就是等芯片回片。

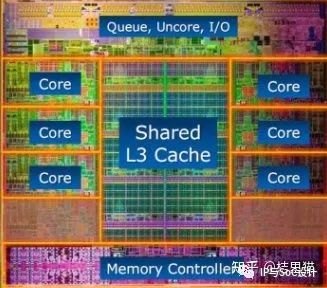

最后的输出大概这设个样子的。

5. 总结

本篇内容是芯片设计的提纲。这个阶段的输入是设计需求,输出是芯片版图。设计主要涉及到3方面的内容,算法设计,芯片前端设计,芯片后端设计。一整个流程很长,至此芯片的设计过程就结束了,下一个过程就是制造!

审核编辑 :李倩

-

芯片

+关注

关注

456文章

50889浏览量

424298 -

算法

+关注

关注

23文章

4615浏览量

92996 -

数字芯片

+关注

关注

1文章

110浏览量

18407

原文标题:一颗芯片的前世今生:设计(流程概述)

文章出处:【微信号:IP与SoC设计,微信公众号:IP与SoC设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

【「从算法到电路—数字芯片算法的电路实现」阅读体验】+阅读第一章部分笔记

GDS文件在芯片制造流程中的应用

浅谈芯片制造的完整流程

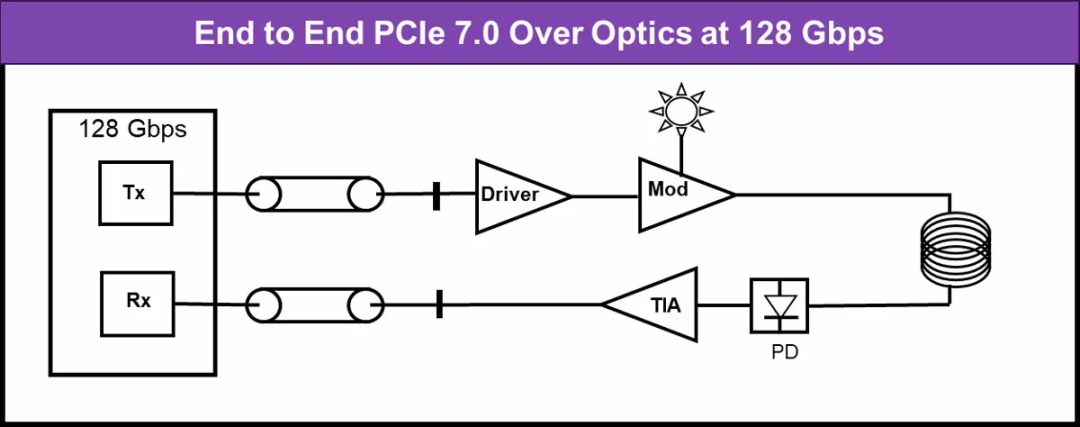

PCIe光传输的优势与挑战

新思科技7月份行业事件

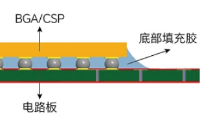

芯片底部填充工艺流程有哪些?

新思科技携手英特尔推出可量产Multi-Die芯片设计解决方案

新思科技引领EMIB封装技术革新,推出量产级多裸晶芯片设计参考流程

新思科技面向英特尔代工推出可量产的多裸晶芯片设计参考流程,加速芯片创新

新思科技面向台积公司先进工艺加速下一代芯片创新

芯片设计流程及各步骤使用工具简介

芯片的设计流程

芯片的设计流程

评论