在通过Verilog语言完成芯片设计,且通过测试平台设计(编写testbench)对所设计的芯片施加激励和观测输出后,需要在计算机上模拟芯片设计,以判断所编写的代码是否符合预期。

在计算机上模拟芯片设计需运用仿真工具,常用的EDA仿真工具主要由三家集成电路公司提供,分别是Mentor Graphics、Cadence、SYNOPSYS。

MentorGraphics的产品是Modelsim,该产品主要在WINDOWS系统上运行,也可以在LINUX系统上运行,适合初学者使用。

Cadence的产品是NC-Sim,该产品主要在LINUX系统上运行,也可以在WINDOWS系统上运行。

SYNOPSYS的产品是VCS,该产品主要在LINUX系统上运行,不能在WINDOWS系统上运行。

上文提及的LINUX系统和WINDOWS系统是EDA仿真工具的两种主要操作系统。

WINDOWS系统主要运用于可编程逻辑器件,如CPLD、FPGA的仿真,这是因为进行验证的工程师(芯片生产前需要进行验证,目的是防止实际生产的芯片出现漏洞导致百万元到千万元人民币的损失)主要使用WINDOWS系统。可编程逻辑器件的仿真工具主要是Modelsim。

LINUX系统主要运用于ASIC设计,即专用集成电路设计的仿真,因为芯片设计到生产过程中使用的仿真以外的其他工具均支持LINUX系统,所以ASIC设计的仿真也主要使用LINUX系统。

根据课程推荐,ASIC设计人员或有学习更专业仿真工具想法的人员最优选择是NC-Sim和VCS这两种专业软件。课程由于证书(license)限制,只能使用Modelsim的教学版进行芯片仿真讲解。

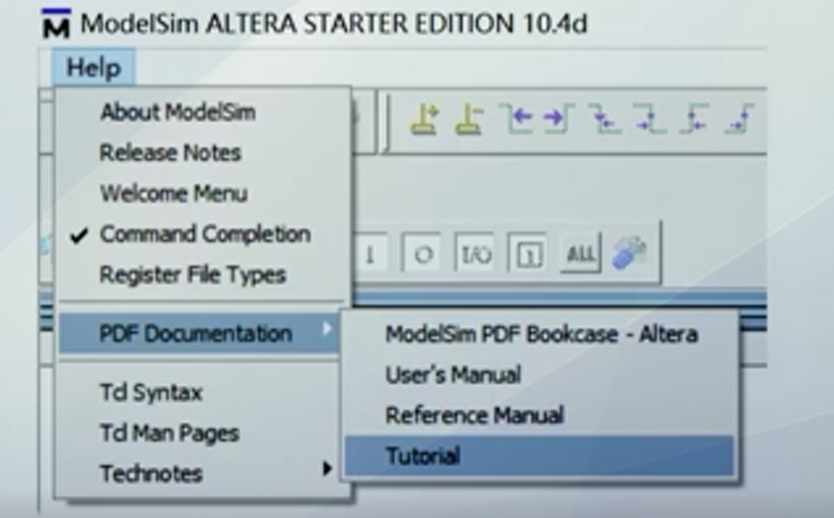

Modelsim中内嵌有教程和用户手册,如果需要学习Modelsim更高级的功能可以查找用户学习手册,网络上也有高级教程可供学习和参考。

图片来源:学堂在线《IC设计与方法》

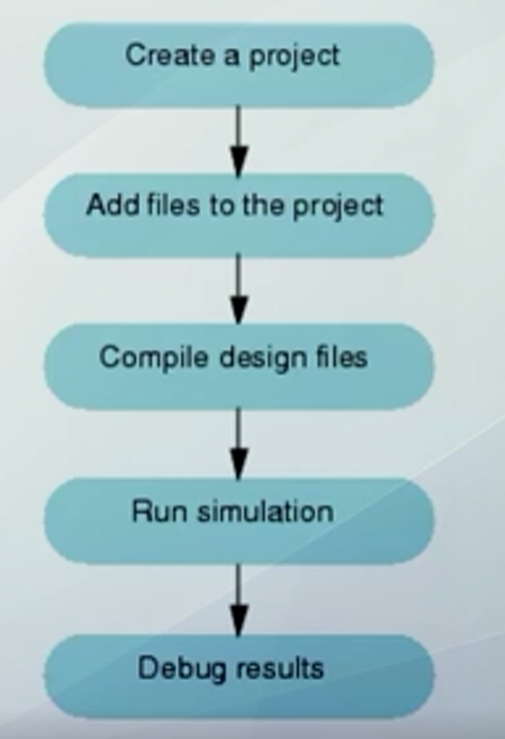

仿真的步骤如下:

(1)设置环境。包括在软件里设置相应的工程环境,设置相应的库文件,库文件是其他人员已完成的设计文件,当设计芯片需要某些已设计完成的文件时,可以调用库文件。

(2)编写Verilog代码。编写Verilog代码既可以使用文本编辑工具,也可以使用Modelsim中提供的代码编辑工具。

(3)编译。编译的目标是将Verilog代码转化成计算机上可以执行的程序。

(4)仿真。在仿真工具中模拟电路执行过程。

(5)分析仿真结果。分析仿真结果是比较重要的步骤。分析仿真结果的目的是检查电路模拟的结果是否正确,是否符合预期的设计目标。分析仿真结果的方法有多种:最直接的方法是用波形的方式检查,更高层次的方法包括数据流图(以图形方式来表达系统的逻辑功能、数据在系统内部的逻辑流向和逻辑变换过程)、有限机(全称有限状态机,是一种用于进行对象行为建模的工具,作用是描述对象在其生命周期内所经历的状态序列,以及如何响应来自外界的各种事件),或用比较高效的方法定位故障发生的位置。

图片来源:学堂在线《IC设计与方法》

审核编辑 :李倩

-

芯片设计

+关注

关注

15文章

1033浏览量

55133 -

仿真

+关注

关注

50文章

4142浏览量

134282 -

Verilog

+关注

关注

28文章

1355浏览量

110660

原文标题:芯片设计相关介绍(21)——仿真工具

文章出处:【微信号:行业学习与研究,微信公众号:行业学习与研究】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

芯片封装需要进行哪些仿真?

模拟IC设计中Spectre和HSPICE仿真工具的起源、差别和优劣势

车载总线监控分析及仿真工具 - VBA

NVIDIA发布全新AI和仿真工具以及工作流

芯片开发必备工具|好用的文件比对工具有哪些?

C2000 MCU的ADC输入电路评估(使用TINA-TI仿真工具)

C2000 AD的电荷共享驱动电路(使用PSPICE-FOR-TI仿真工具)

C2000 ADC的电荷共享驱动电路(使用TINA-TI仿真工具)

免费好用的在线仿真工具Wokwi

模拟电路仿真软件包含大部分芯片吗

演进中的电力电子设计:安森美先进仿真工具

芯片设计之仿真工具

芯片设计之仿真工具

评论