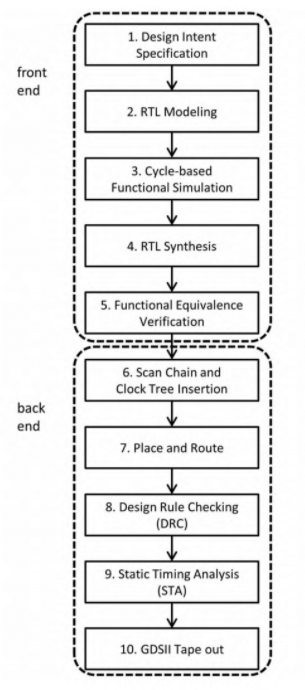

1、ASIC设计流程

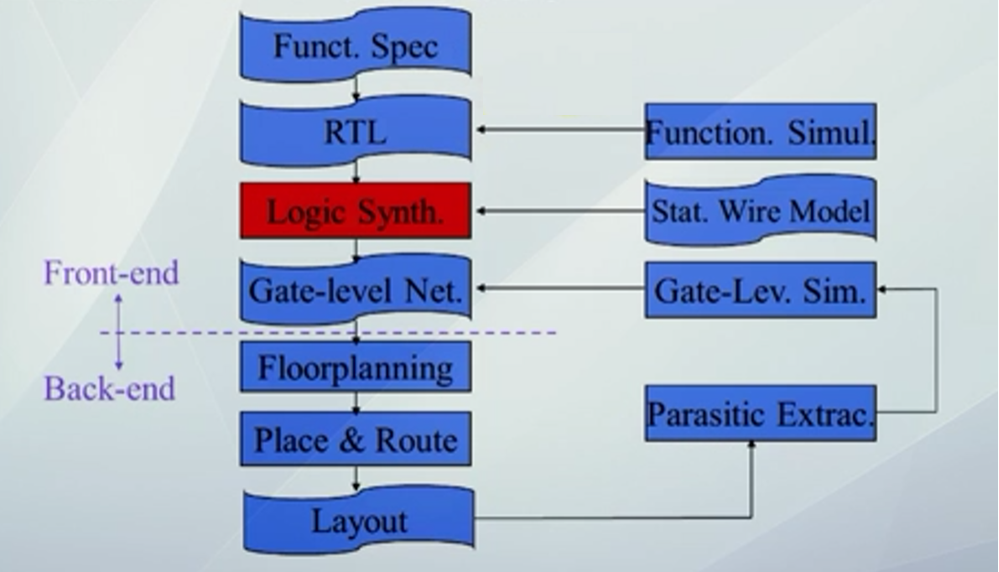

ASIC(专用集成电路)的设计如下,Front-end部分是前端设计,Back-end部分是后端设计。

图片来源:学堂在线《IC设计与方法》

Funct.Spec代表设计需求,在具体设计需求提出后,编写RTL代码(Verilog代码设计电路的一种设计类别);RTL代码编译完成,进行Function.Simul,即仿真;仿真结束后,进行逻辑综合(Logic Synth.),将Verilog代码转化为电路,术语称该电路为门级网单(Gate-Level Net.)。

逻辑综合(Logic Synth.)过程需要约束(Stat. Wire Model)以产生规定条件下的电路。具体电路设计完成后,需进行门级仿真(Gate-Lev.Sim),以检查电路设计是否出现失误。

门级网单确定后,进入后端设计。首先是布局规划(Floorplanning),摆放门级网单中的各个元器件位置。然后是布局和布线(Place&Route),将各个元器件连接。最后产生电路的版图(Layout)。

在将电路的版图加工制造前,为防止后端设计失误,需要进行验证。验证前需提取版图的寄生参数(Parasitic Extrac.),寄生参数包括导线的寄生电容、寄生电感、寄生电阻,寄生参数会造成信号传输延时、失真、干扰。验证中,将寄生参数反标到门级网单上,再次做门级仿真(Gate-Lev.Sim)。最终的仿真结果没有问题后,电路版图可以用于加工制造。

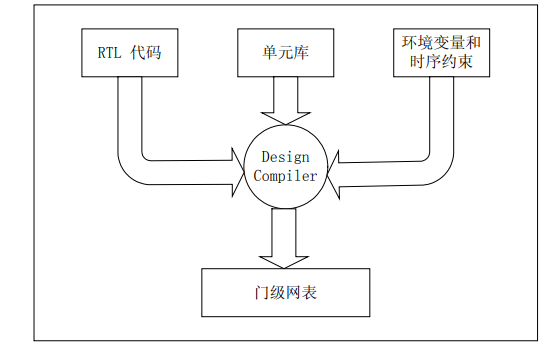

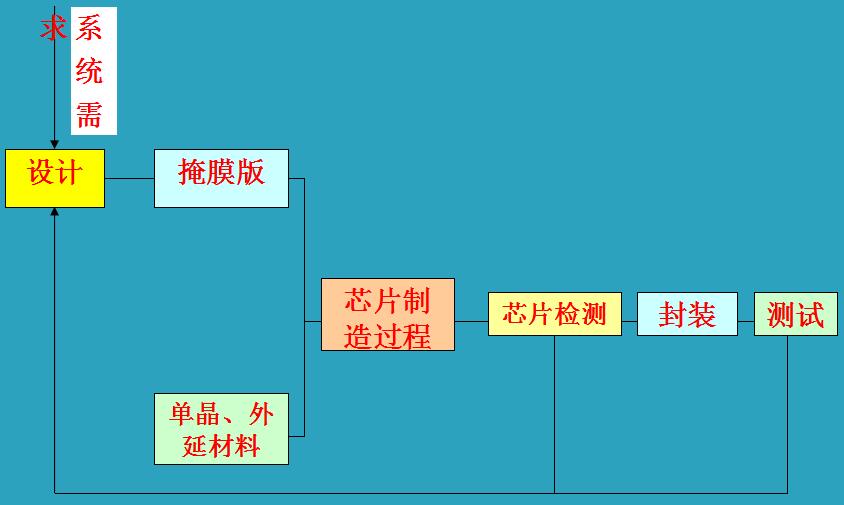

2、逻辑综合

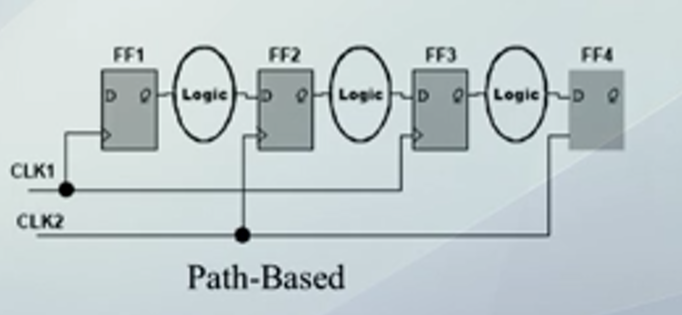

芯片代码仿真的下一步是逻辑综合,逻辑综合将Verilog代码转化为电路图。逻辑综合的目的是决定门级结构,寻求时序、面积、功耗的平衡。寻求平衡的方式有两种:约束驱动和路径驱动。

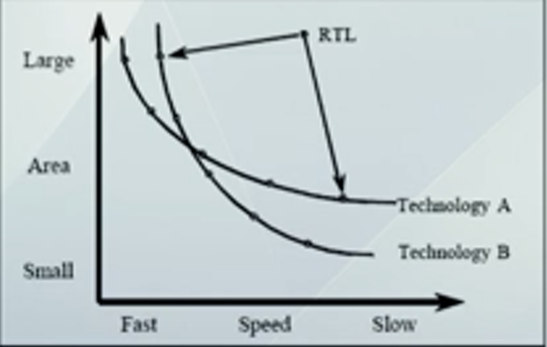

约束驱动是平衡面积和速度的方式。一个厂家(如TSMC)的一种工艺条件(如0.18um工艺)下,芯片的速度快和面积小相互制约,速度更快的芯片需要更大的面积,面积更小的芯片速度更慢。不同厂家的同种工艺面积和速度的制约程度不一定相同,有经验的设计人员可以选择合适的厂家寻求最优的面积和速度。

图片来源:学堂在线《IC设计与方法》

路径驱动是将电路中的元器件以最优的方式连接。

图片来源:学堂在线《IC设计与方法》

逻辑综合过程可运用预先设计完成的逻辑单元,提高设计效率。逻辑单元包括标准单元和宏单元。标准单元的尺寸有一定的标准,包括基本门电路、寄存器等。宏单元功能相对复杂,难以在固定高度内安装,包括RAM存储器、ROM存储器、数值运算单元等。

标准单元的名称详细,如ARM UMC L180GⅡ 1.8V标准单元库表示:由ARM公司(个人理解:设计公司)提供的,针对UMC(联华电子公司,个人理解:制造公司)厂家的,针对逻辑工艺的,180nm(0.18um)的,GⅡ工艺的,1.8V的标准单元库。

标准单元包括元器件数量多,ARM UMC L180GⅡ 1.8V标准单元库包含124种元器件,数量为470个。

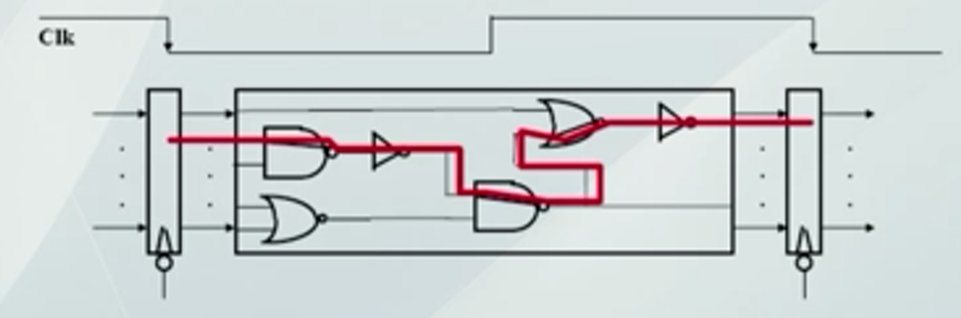

逻辑综合过程还需进行静态时序分析。静态时序分析的前提是触发器使用同一时钟,即全同步电路。静态时序分析的准则为:

时钟周期>Clockto Q+穿越组合逻辑电路的最长延时+Set up

其中Clock to Q是时钟沿出现到触发器输出信号的延时,Set up时间是下一级触发器输入信号稳定建立的延时。

图片来源:学堂在线《IC设计与方法》

当静态时序分析的准则成立时,时序逻辑电路可以稳定工作。

审核编辑 :李倩

-

集成电路

+关注

关注

5403文章

11698浏览量

364687 -

asic

+关注

关注

34文章

1209浏览量

121163 -

仿真

+关注

关注

50文章

4155浏览量

134486

原文标题:芯片设计相关介绍(23)——ASIC设计流程和逻辑综合

文章出处:【微信号:行业学习与研究,微信公众号:行业学习与研究】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

典型的基于RTL的ASIC设计流程分析

ASIC逻辑综合及Synopsys Design Compi

ASIC与大型逻辑设计实习教程

面向ASIC和FPGA设计的多点综合技术

ASIC逻辑综合及Synopsys Design Compiler 的使用资料说明

芯片设计之ASIC设计流程和逻辑综合

芯片设计之ASIC设计流程和逻辑综合

评论