作者:潘文明

1.引言

Vivado中提供了1种IBERT工具用于对Xilinx FPGA芯片的高速串行收发器进行板级硬件测试。通过IBERT我们可以获取误码率,观察眼图,调节串行收发器的参数,从而有助于判断可能存在的问题,便于验证硬件的稳定性和信号完整性。本测试实例教程使用IBERT工具对与SFP连接的GTX进行5 Gbps速率下的测试。从误码率和眼图两个角度来验证电路板GTX部分工作的稳定性和可靠性。本测试实例基于Vivado 2019.1版本开发。

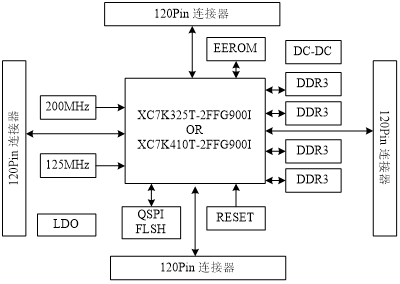

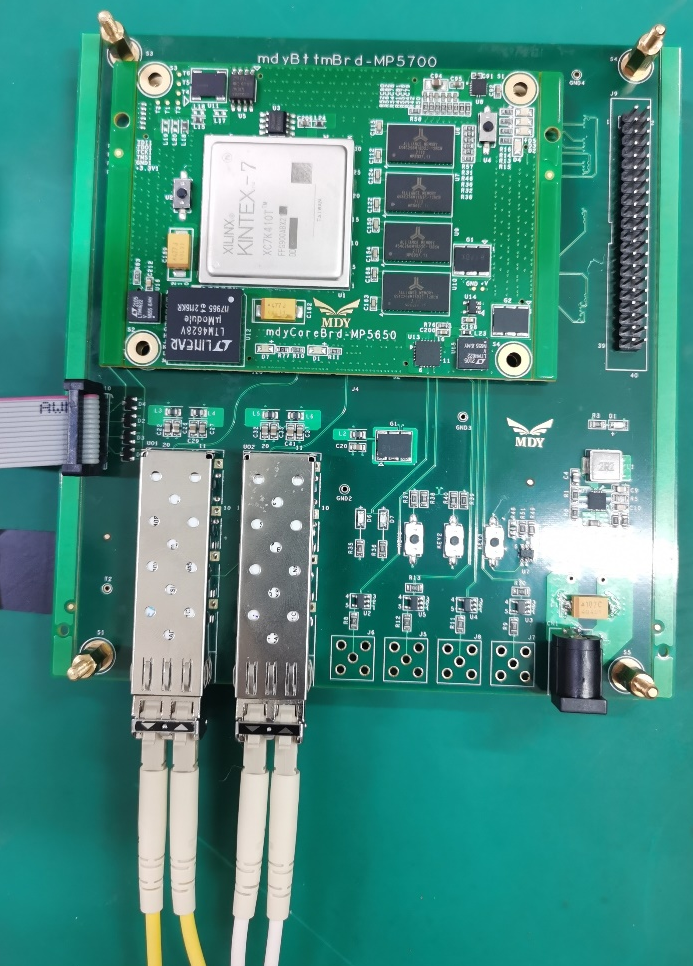

本测试实例是在购买的明德扬(MDY) K7核心板上进行的,这款核心板能够方便二次开发利用。在FPGA 芯片的HP 端口上挂载了4片DDR3存储芯片,每片DDR3 容量512 MB 字节,组成64bit 位的数据位宽。4个板对板连接器扩展出了276个IO,全部IO的电平可以通过更换核心板上的磁珠来修改,满足用户对+3.3V、+2.5V、+1.5V电平接口的需求,另外也扩展出了16对高速收发器GTX接口。供电范围大,5-12V电压均可。通过手册了解到同一个BANK管脚到连接器接口之间走线做了等长和差分处理。该核心板的结构示意图如图1。

图1 该核心板结构示意图

2.测试原理

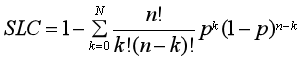

IBERT中的BERT是Bit Error Ratio Test的缩写,指比特出错概率测试,简而言之就是误码率测试。误码率(Bit Error Rate,BER)作为高速数据传输技术中的重要指标,它代表了数据传输的可靠性。对于数字通信系统,BER可以定义为出现错误码的估计概率。这意味着任何通过系统传输的比特都可能被错误地接收。因此,发送的“1”接收到为“0”,或传输为“0”被接收到的为“1”。在实际测试中,误码率是通过系统传输一定比特的比特数和计算接收到的不正确的比特数来测量的。误码率是接收到的错误比特数与传输的总比特数之比。利用累积分布函数定义置信系数SLC(Statistical Level of Confidence):

式中,N为传输中发生错误的比特数,n为传输的总的比特数,p = 10-12,通过置信系数得到在传输n bit后误码率为:

式中,BER 传输n bit发生错误概率,ln[.]是自然对数。当没有检测到错误(N = 0)时,式5.7中的第二项等于零,方程的求解得到了很大的简化。

首先对明德扬Xilinx K7核心板光纤接口进行了误码率。Vivado中IBERT工具的测试原理是通过收发器由外部回环进行自收自发而实现。就是将同一组收发器的TX和RX进行短接,TX发送端通过发送某种特定序列的数据流,在RX接收端接收后,通过比对发送和接收的数据,从而得出接收端误码的统计值。将光模块插入SFP屏蔽笼内,然后通过单根光纤将光模块的TX和RX短接,便可以通过IBERT工具对GTX进行测试。

3.QUAD(GTX BANK)、CHANNEL、GTX间的关系

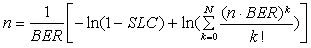

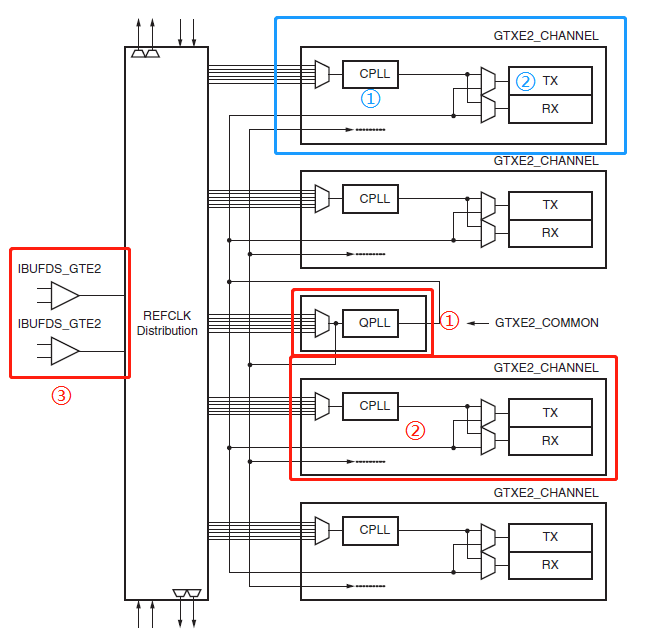

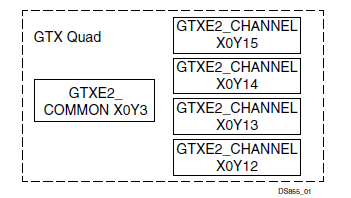

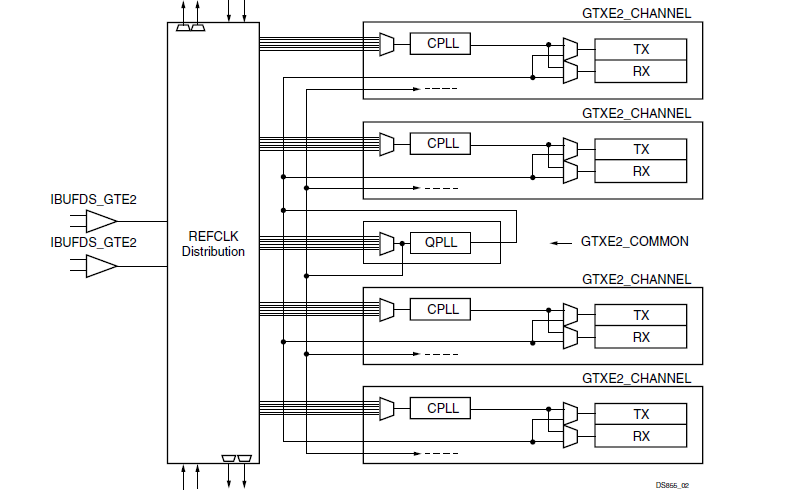

首先可以从图2中看到XC7K325T中共有16个GTX,每4个GTX组成一个Bank,称为Quad,即XC7K325T芯片共有4个Quad。

图2 Kintex-7 FPGA(XC7K325T)GTX结构图

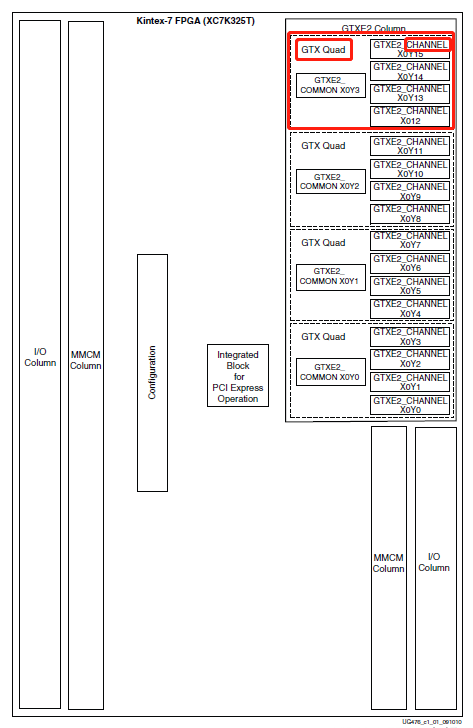

如图3所示,具体看Quad布局图,可以看到一个Quad包含4个GTX_channel(简称GTX或channel)和一个QPLL。

图3 Quad布局图

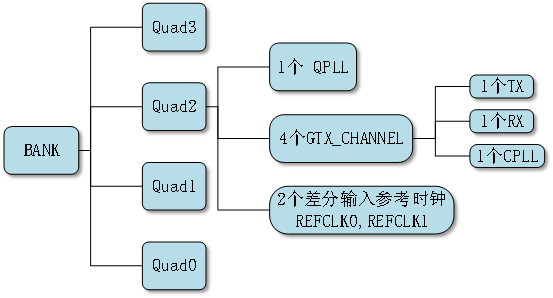

所以Kintex-7 FPGA(XC7K325T)中quad、channel、GTX相互关系如图4所示。1个Quad中有2个参考时钟(REFCLK0,REFCLK1),根据板卡设计图可知具体使用REFCLK0还是REFCLK1,参考时钟频率应根据核心板实际晶振频率来选择。

图4 quad、channel、gtx相互关系

4.测试结果

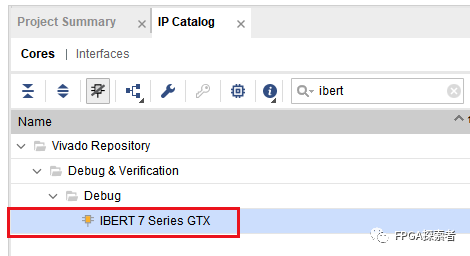

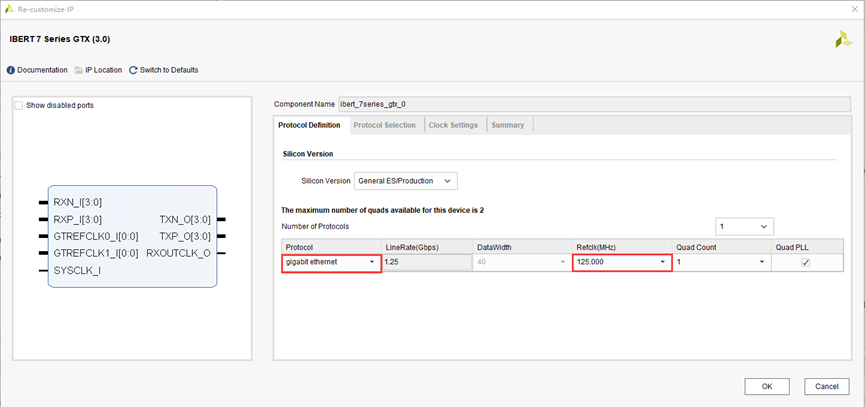

通过新建IP核工程,为IBERT协议配置定义界面,IP核有一些预置的协议,如收发器线速率选择,位宽选择,收发器参考时钟来源和频率等。本设计SFP+来自Quad116,参考时钟来自MGTREFCLK1_116。本设计将GTX收发器参考输入时钟作为其系统时钟。之后例化,生成bit流文件,完成FPGA配置文件生成。按照测试原理,我们将SFP+的光纤模块的TX和RX短接,如图5所示。连接好硬件,将bit文件下载到硬件电路板。

图5 硬件实物图与连接

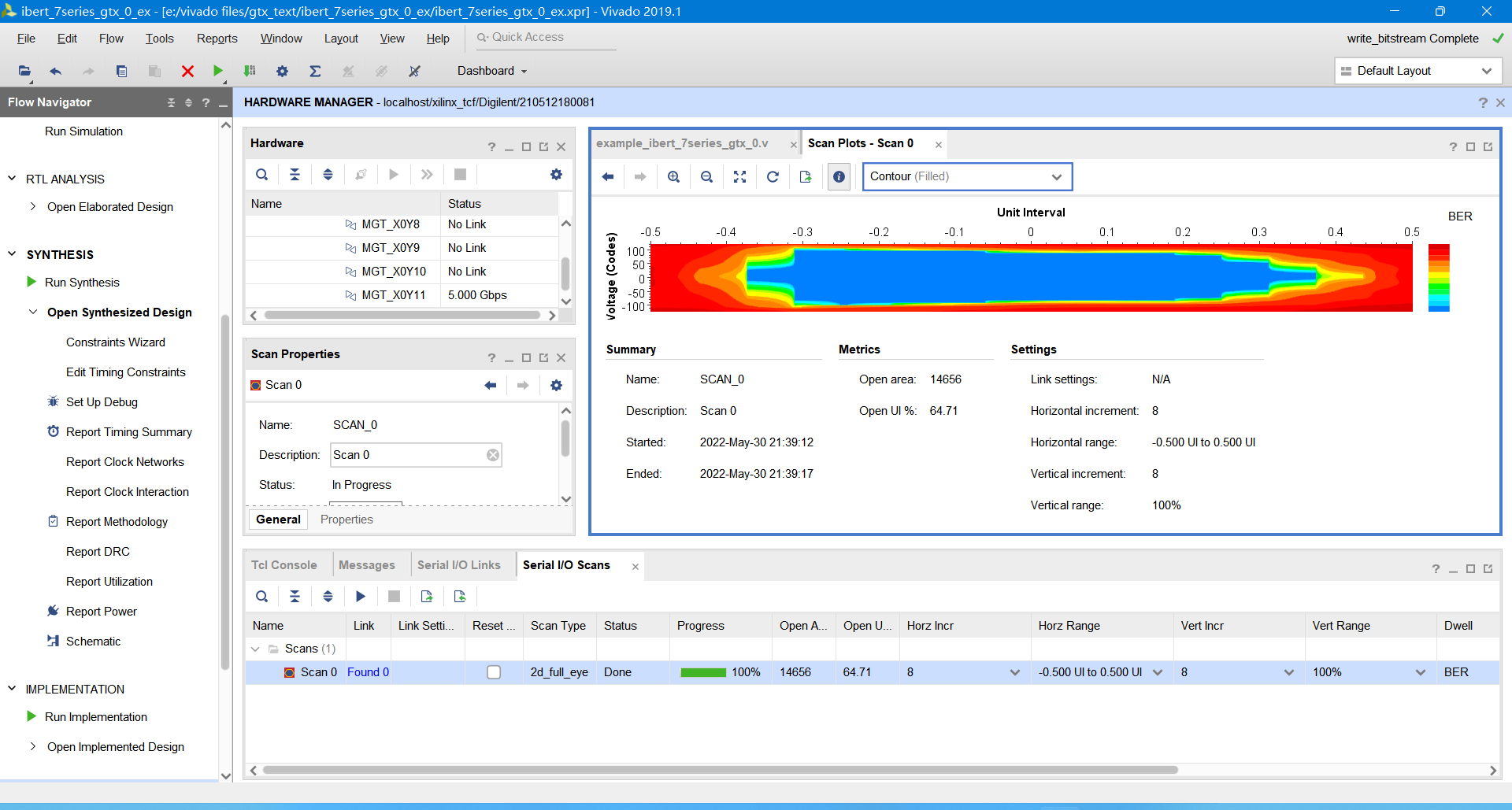

选择需要查看眼图的链路,眼图参数可以使用默认参数,收发器眼图测试结果如图6所示。

图6 测试收发器眼图

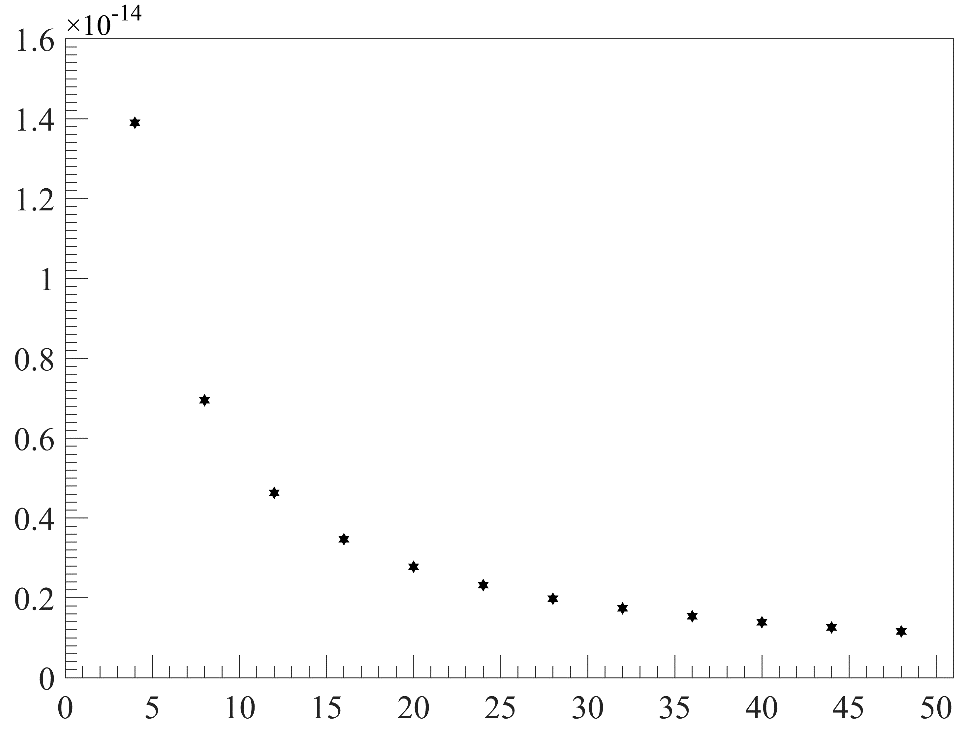

利用单根光纤将光模块输入输出短接进行回环测试,使用IBERT IP核测试,通过Xilinx下载器将数据读出。回环测试序列使用PRBS-31。每2小时记录一次数据,总共测试48小时。测试结果如图7所示,横坐标为时间,连续运行48小时后,纵坐标为误码率,光纤通信误码率为2 × 10-15,速率稳定在5 Gbps,除去编码开销实际速率为4 Gbps,满足一般的速率需求。

图7 误码率测试

5.总结

通过环回方式的误码率测试,可判断出存在的问题以及测试出板卡实际支持的速率。IBERT可在运行过程中设置高速串行收发通道的各项参数,并提供了多种环回模式及多种测试激励源,并可通过自动扫描测试,确定收发的最佳参数。可以满足硬件测试时对高速串行收发通道信号测试的大部分需求,在故障定位等场合均可使用。

审核编辑:汤梓红

-

FPGA

+关注

关注

1664文章

22502浏览量

639189 -

收发器

+关注

关注

10文章

3838浏览量

111451 -

GTX

+关注

关注

0文章

36浏览量

11489

发布评论请先 登录

IBERT GT收发器误码率测试实例

利用 IBERT 进行 GTX 信号眼图测试 精选资料分享

基于FPGA的误码率测试仪的设计与实现

IP集成式误码率测试器(IBERT)的主要性能和优势介绍

BER误码率 影响误码率的因素

误码率是指什么_误码率是怎么表示_怎么计算

virtex-7 GTX的Chipscope集成误码率测试资料说明

用于Kintex-7 FPGA GTX的Chipscope Pro集成误码率测试资料说明

关于ZC706评估板的IBERT误码率测试和眼图扫描详细分析

ZC706评估板IBERT误码率测试和眼图扫描

利用IBERT IP核实现GTX收发器硬件误码率测试实例

利用IBERT IP核实现GTX收发器硬件误码率测试实例

评论