Icarus Verilog(以下简称iverilog )号称“全球第四大”数字芯片仿真器,也是一个完全开源的仿真器。由于Synopsys、Cadence、Mentor版权的关系,国外很多高校在数字芯片设计的教学中都采用iverilog。 GTKWave是一个开源的波形文件察看工具,支持Verilog VCD/EVCD文件格式。因此,通过“iverilog +gtkwave”的方式,可以很方便地实现商用仿真器的功能。 本文为我的学生整理自 iverilog 和 gtkwave 官方网站。 介绍 iverilog Icarus Verilog是一个verilog仿真工具. 以编译器的形式工作, 将以verilog编写的源代码编译为某种目标格式. 如果要进行仿真的话, 它可以生成一个叫做vvp的中间格式. 这个格式可以由其所附带的vvp命令执行. gtkwave wave viewer. 可以用于查看标准的verilog VCD/EVCD, 以及其他的一些格式的波形文件。 安装 iverilog

linux a. 包管理器安装下载:sudo pacman -S gtkwave b. 从上面的链接下载源码, 然后编译

使用 1. 示例:

1//adder_rtl.v 2moduleadder(clk,rst_n,a,b,c); 3input[3:0]a; 4input[3:0]b; 5output[7:0]c; 6inputclk,rst_n; 7 8wire[3:0]a; 9wire[3:0]b; 10wire[7:0]c; 11 12always@(posedgeclkornegedgerst_m)begin 13if(rst_n==1'b0) 14c<= 8'b0; 15 else 16 c <= a+b; 17 end 18endmodule 2. 编译:

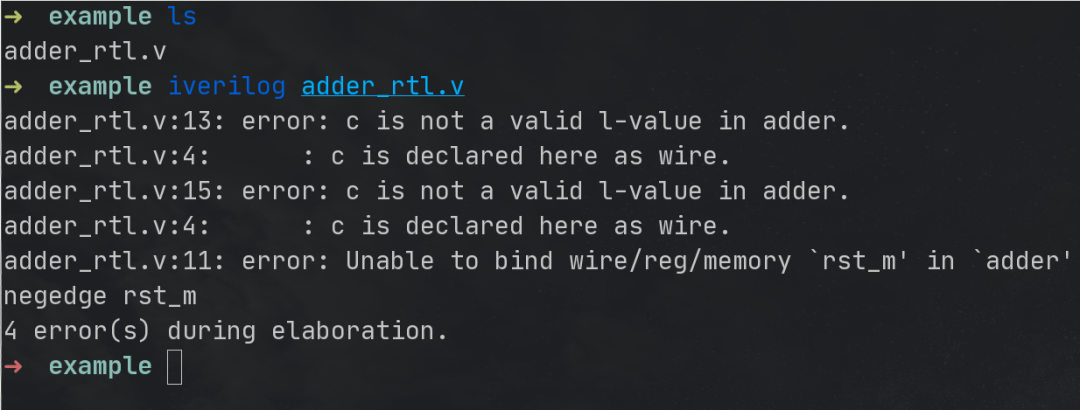

1iverlogadder_rtl.v

抄错了. damn.

抄错了. damn.

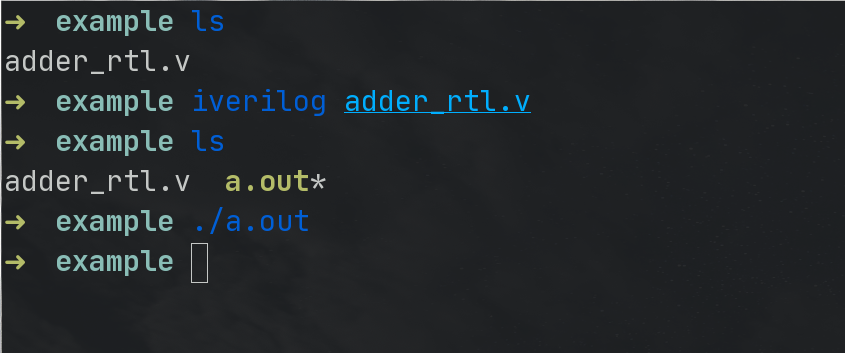

1moduleadder(clk,rst_n,a,b,c); 2input[3:0]a; 3input[3:0]b; 4output[7:0]c; 5inputclk,rst_n; 6 7wire[3:0]a; 8wire[3:0]b; 9reg[7:0]c; 10 11always@(posedgeclkornegedgerst_n)begin 12if(rst_n==1'b0) 13c<= 8'b0; 14 else 15 c <= a+b; 16 end 17endmodule 3. 编译: 1iverlogadder_rtl.v

无事发生. tb:

无事发生. tb:

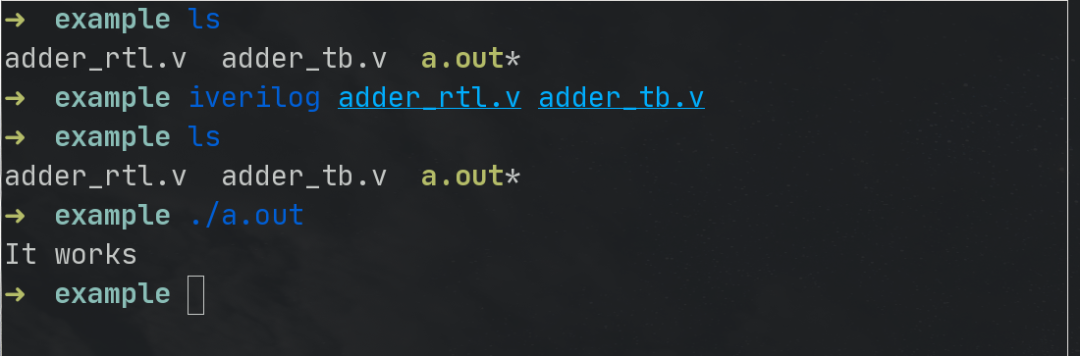

1//adder_tb.v 2`timescale1ns/1ns 3moduleadder_tb(); 4reg[3:0]a; 5reg[3:0]b; 6wire[7:0]c; 7 8regclk,rst_n; 9 10adderDUT( 11.clk(clk), 12.rst_n(rst_n), 13.a(a), 14.b(b), 15.c(c) 16); 17 18alwaysbegin 19#10clk=0; 20#10clk=1; 21end 22 23initialbegin 24rst_n=1; 25test(4'b1111,4'b1111,5'b11110); 26$finish; 27end 28tasktest; 29input[3:0]in; 30input[3:0]in2; 31input[7:0]e; 32begin 33a=in; 34b=in2; 35@(posedgeclk); 36@(negedgeclk); 37if(c==e)begin 38$display("Itworks"); 39endelsebegin 40$display("opps%d+%d~=%d,expect%d",in,in2,c,e); 41end 42end 43endtask 44endmodule 4. 编译运行:

1iverilogadder_rtl.vadder_tb.v

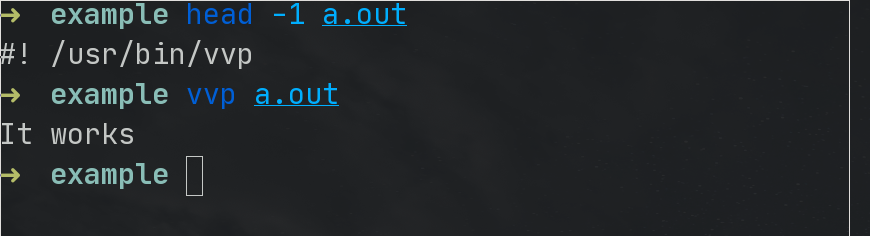

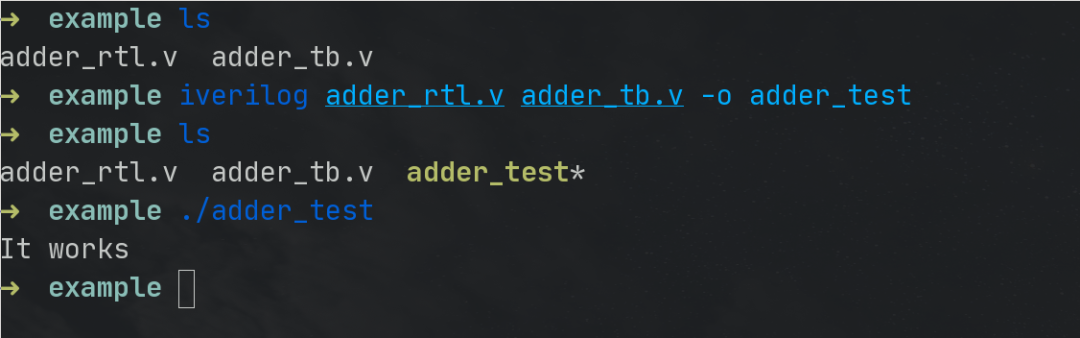

5. 使用-o选项指定输出文件的名称

5. 使用-o选项指定输出文件的名称

1iverilogadder_rtl.vadder_tb.v-oadder_test

6. 在tb中添加dump:

6. 在tb中添加dump:

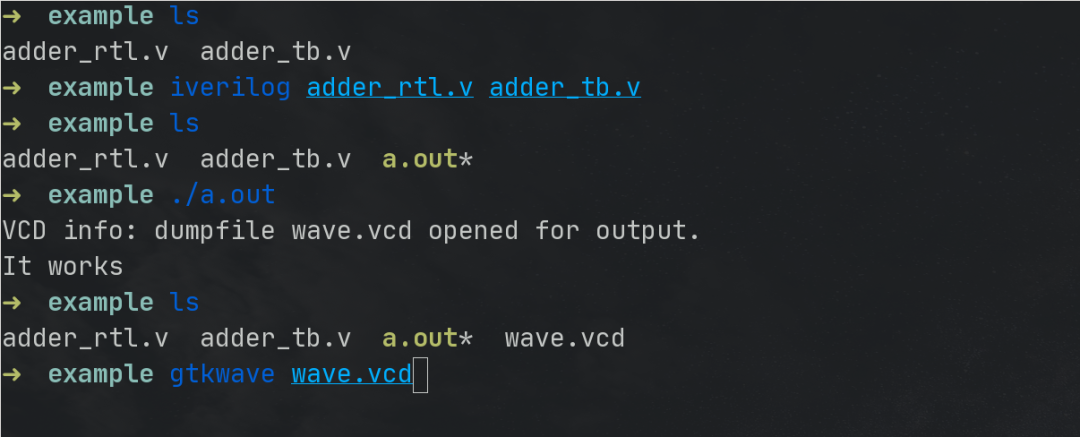

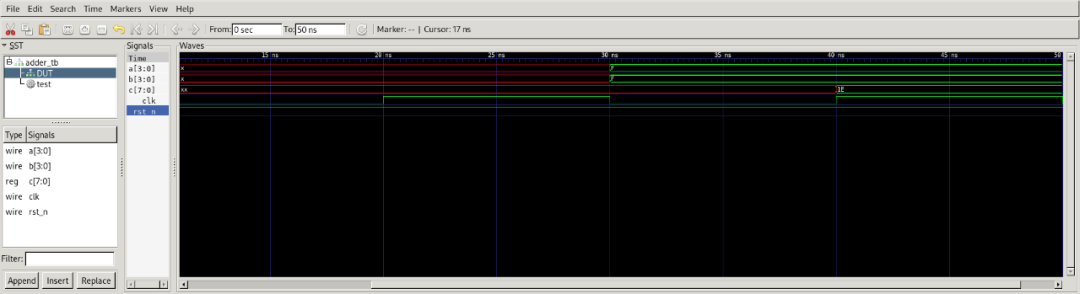

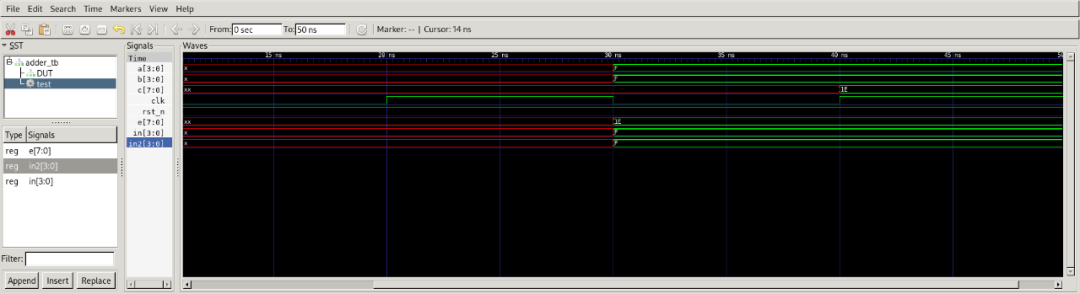

1initialbegin 2$dumpfile("wave.vcd");//指定用作dumpfile的文件 3$dumpvars;//dumpallvars 4end 7. 重新编译运行一遍, 生成了一个vcd文件, 使用gtkwave查看.

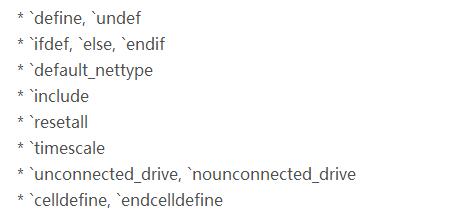

iverilog的一些选项:

iverilog的一些选项:

-D: 定义宏

-P: 覆盖root module中的一个参数的值

-E: 只预处理(进行宏替换), 不编译

-g1995, -g2001, -g2005 ...: 选择支持的verilog语言版本.

-I includedir: 指定(添加)verilog中include指令的搜索路径

-s topmodule : 指定要建立的顶层模块. 默认是没有被实例化的哪些module

VPI: Verilog Prodecure Interface(VPI), 最开始也称作PLI 2.0, 一个主要面向C语言的接口. 可以让行为级别的Verilog代码调用C函数, 让C函数调用标准Verilog系统函数.

1//adder.c 2#include

1//adder_tb.v 2`timescale1ns/1ns 3moduleadder_tb(); 4reg[3:0]a; 5reg[3:0]b; 6wire[7:0]c; 7 8regclk,rst_n; 9 10integeri,n,nf; 11 12adderDUT( 13.clk(clk), 14.rst_n(rst_n), 15.a(a), 16.b(b), 17.c(c) 18); 19 20alwaysbegin 21#10clk=0; 22#10clk=1; 23end 24 25initialbegin 26$display("============================="); 27$display("Tbstartathere"); 28rst_n=1; 29n=0; 30nf=0; 31//$test($random%4,2); 32for(i=0;i< 20; i++) 33 test($urandom%5'b10000,$urandom%5'b10000); 34 $display("%d total, %dfail", n, nf); 35 $finish; 36 end 37 task test; 38 input [3:0] in; 39 input [3:0] in2; 40 begin: test 41 reg [7:0] e; 42 a = in; 43 b = in2; 44 $sum(a,b,e); // HERE 45 @(posedge clk); 46 @(negedge clk); 47 n = n + 1; 48 if (c == e) begin 49 $display("Itworks, %d + %d = %d", in, in2, e); 50 end else begin 51 nf = nf + 1; 52 $display("opps%d + %d ~= %d, expect %d", in, in2, c, e); 53 end 54 end 55 endtask 56 57 // initial begin 58 //$dumpfile("wave.vcd"); 59 // $dumpvars; 60 // end 61endmodule 编译运行:

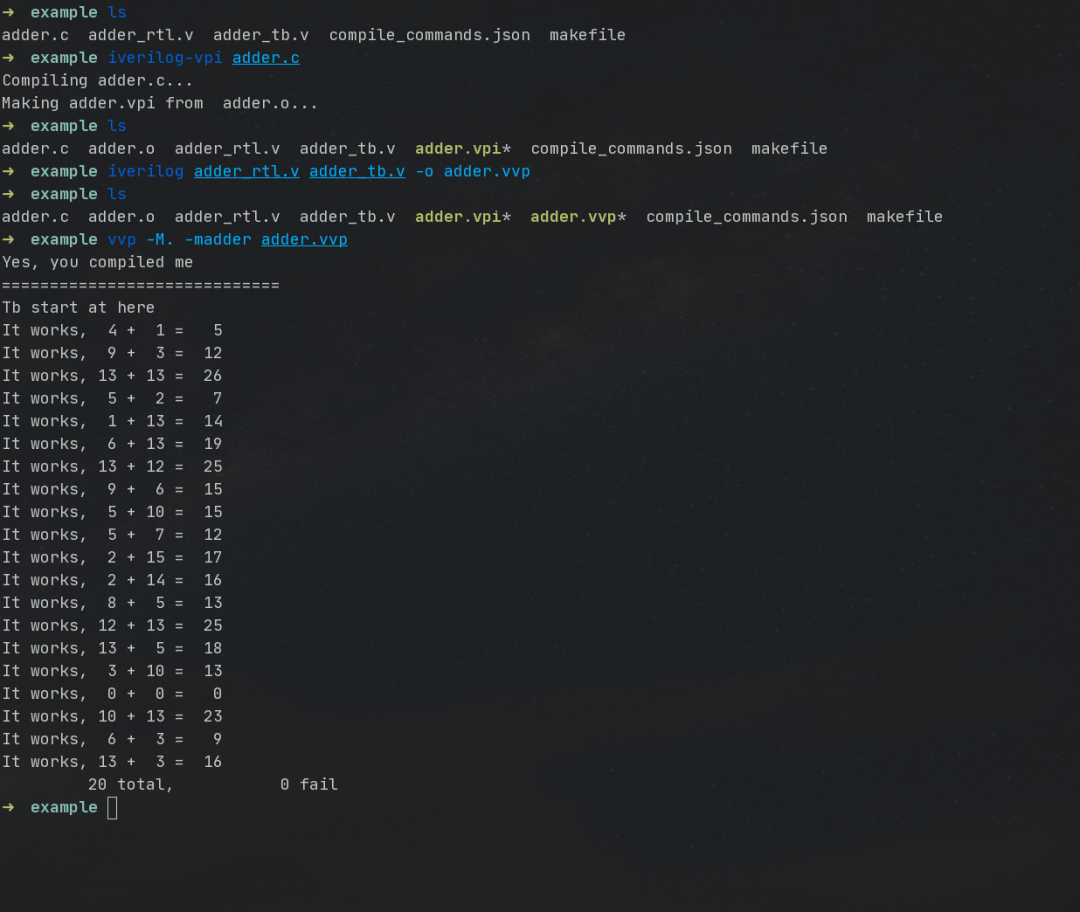

1iverilogadder_rtl.vadder_tb.v-oadder.vvp 2iverilog-vpiadder.c 3vvp-M.-madderadder.vvp iverilog-vpi: 自带的帮助生成库的脚本 -M path: 将path加入定位VPI模块的路径, .: 当前路径 -m module: 告诉vvp在执行simulation之前加载指定的module.

-

Verilog

+关注

关注

30文章

1374浏览量

114709 -

编译

+关注

关注

0文章

696浏览量

35271 -

仿真工具

+关注

关注

0文章

38浏览量

11359

原文标题:一文学会使用全球第四大数字芯片仿真器iverilog!

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

使用NucleiStudio生成tb仿真需要的.verilog文件

FPGA Verilog编译和Syntesi工具怎么使用

基于Verilog的顺序状态逻辑FSM的设计与仿真

北大微电子verilog讲义课件

如何使用Icarus Verilog+GTKWave来进行verilog文件的编译和仿真

verilog仿真工具编译

verilog仿真工具编译

评论