内核到 I/O 口的躁声串扰

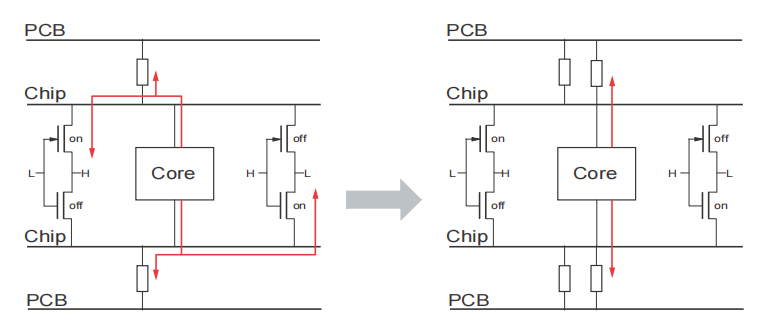

任何两个电路在它们的供电时共用同一阻抗,彼此之间将会产生串扰。下例图左边部分说明了核和

I/O 利用同一电源的情况下的核噪声。 这个噪声是由与压降相关的核电流引起的,这里的压降是通过粘

合线和引脚自感引起的,在图 3-3 中,以电阻的形式表示。即使 PCB 的电源电压系统是远离各种纹波电

压,但片内电源也是有躁声的。因为端口缓冲区和内核是同一种内部电源,噪声通过激活的晶体管传递到

每个输出接脚,这不仅影响输出管脚,还影响输入引脚,输入引脚被影响取决于芯片内部的寄生电容(例

如保护电路)。 在对 EME 敏感的情况下,可能需要对每一个引脚滤波,至少对于多引脚的微控制器,这是

基于成本和空间的原因。

共用与隔离电源的串扰

审核编辑 黄昊宇

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

mcu

+关注

关注

146文章

17171浏览量

351495 -

电路设计

+关注

关注

6676文章

2454浏览量

204533 -

串扰

+关注

关注

4文章

189浏览量

26958

发布评论请先 登录

相关推荐

MCU IO口的作用和特点

MCU(微控制器)的IO口(Input/Output Port,输入输出端口)是单片机与外界进行信息交互的关键接口。这些IO口在微控制器的功

高频电路设计中的串扰问题

在高频电路的精密布局中,信号线的近距离平行布线往往成为引发“串扰”现象的潜在因素。串扰,这一术语描述的是未直接相连的信号线间因电磁耦合而产生的不期望

信号的串扰介绍

信号串扰(Crosstalk)是指在信号传输过程中,一条信号线上的信号对相邻信号线产生的干扰,这种干扰是由于电磁场耦合或直接电容、电感耦合引起的。根据耦合类型和位置的不同,信号串扰主要

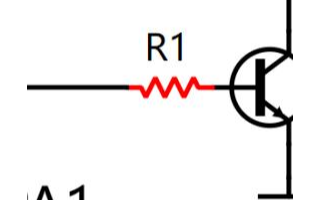

电路设计必知的MCU IO口用作输出和输入时要串联多大的电阻才合适?

拉电流就是流出,灌电流就是流入,二者都是有限制的,不可超过IC规格书中规定的最大值。回到我们最开始的问题,当MCU IO口用作输出和输入时要串联多大的电阻才合适呢?其实就是去查阅MCU

嵌入式开发中引起串扰的原因是什么?

电路布线常会有串扰的风险,最后简单说明几个减小串扰的方法,常见增大走线间距、使两导体的有串扰风险的区域最小化、相邻层走线时传输线互相彼此垂直

发表于 03-07 09:30

•1844次阅读

PCB产生串扰的原因及解决方法

PCB产生串扰的原因及解决方法 PCB(印刷电路板)是电子产品中非常重要的组成部分,它连接着各种电子元件,并提供电气连接和机械支撑。在 PCB 设计和制造过程中,串扰是一个常见的问题

如何使用SigXplorer进行串扰的仿真

问题愈发严重。当受害线路上有信号传输时,串扰产生的噪声会叠加在该信号上,导致信号畸变。这种畸变可能会导致信号的幅度噪声增加或眼图(EyeDiagram)宽度发生变化。

MCU—IO口的噪声串扰

MCU—IO口的噪声串扰

评论