前面讲过反射,讲过损耗。接下来讲串扰(Crosstalk)。

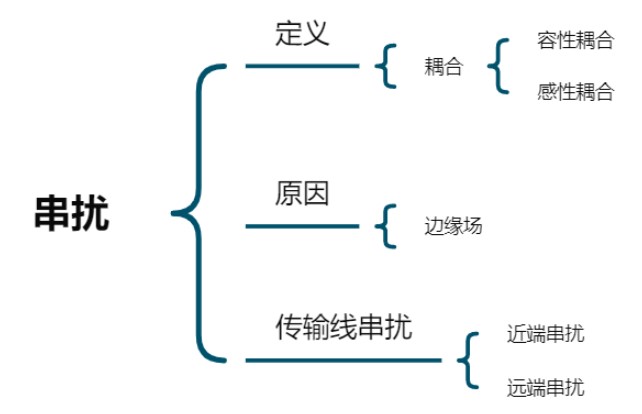

话不多说,直接上图,串扰的分类:

一个网络传递信号,有些电压和电流通过网络之间的耦合(容性耦合和感性耦合),传递到相邻网络,这就是串扰。

对于相邻网络而言,不管给什么,不是想要的,都会以噪声的形式耦合过来。

串扰与网络的信号路径及返回路径与另一个网络的信号路径及返回路径都有关系。

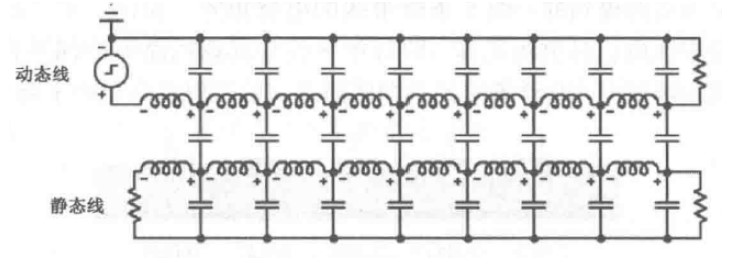

这里面有概念的东西:动态线网&静态线网;攻击线网&受害网络。

既然说是网络之间的耦合(Coupling),那什么是耦合?

耦合简单来说就是能量从一个介质(PCB板,金属导线等)传播到另一种介质。

耦合分为容性耦合和感性耦合。

实际的工作中,该怎么考虑?或者说哪一种耦合更要注意,也分两种情况:

均匀传输线且有均匀很宽的返回路径,容性耦合和感性耦合相当;

非均匀传输线,比如接插件或封装的场合,感性耦合占主导地位。这里面要注意开关噪声(SSN):开关噪声大多发生在插件、封装和过孔处,耦合电感很大。

地弹就是返回电流重叠出现的一种特殊情况。

导线中有电流产生,就会有围绕在信号路径和返回路径导体周围的磁力线圈。由于信号路径和返回路径之间的空间是不封闭的,所以会延伸到周围的空间,这个延伸出去的空间称之为边缘场。

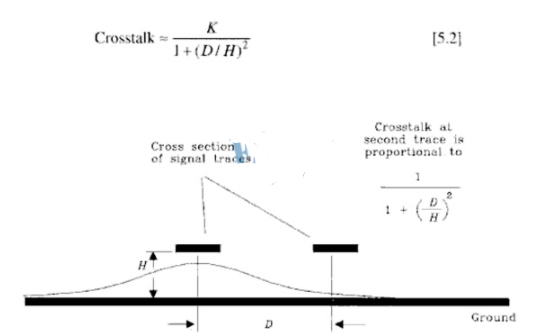

既然是所谓的边缘场引起的串扰,那么越远,受的影响就越小。惹不起还躲不起嘛,离它们远远的,简单粗暴。话是这样说,实际工作中,PCB板走线的密度限制,不可能给你想要的空间。怎么办?

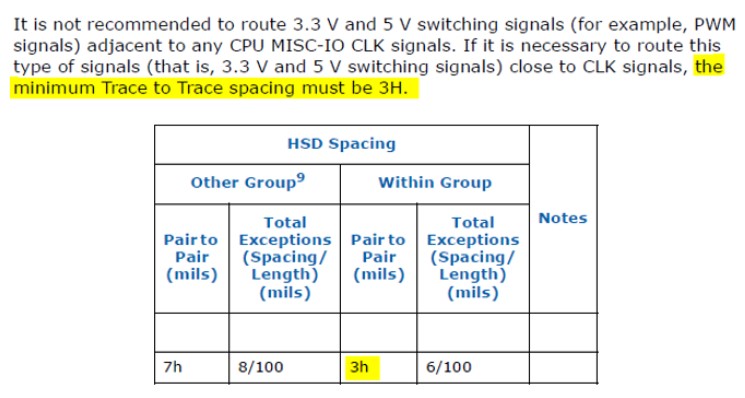

Intel的规范给出了一个HSD组内的间距还有普通线之间的间距,都是3H。

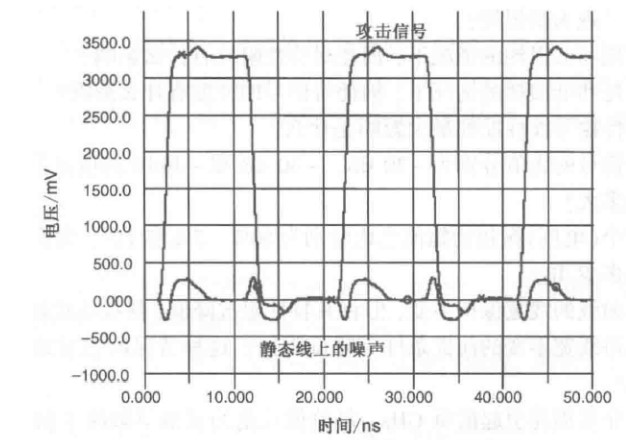

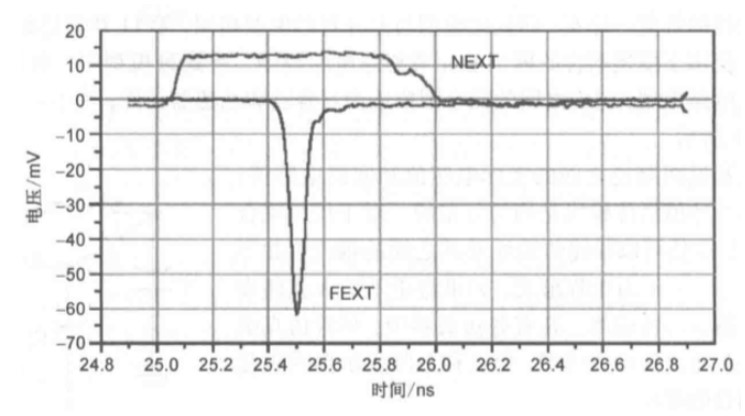

讲到传输线串扰,下图是一张必须知道的图:

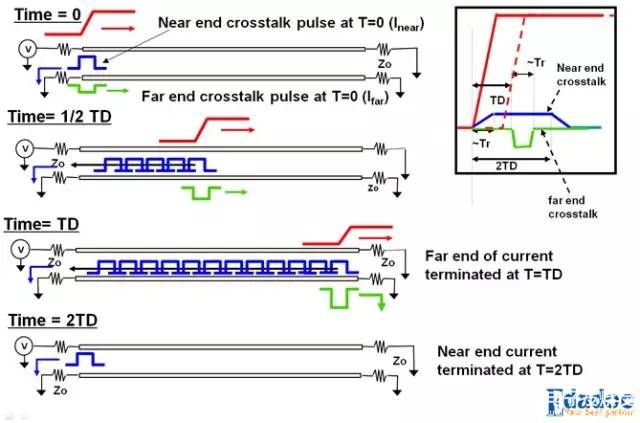

NEXT:近端串扰 FEXT:远端串扰

两根传输线,信号从其中一根传输线的一端输入,远端放端接消除末端反射。如果不放端接,那就会有反射,至于反射的能量消耗,前文有讲过。

噪声电压在静态线的两端进行测量。为了区分两个末端,把距离源端最近的一端称为“近端”,也成为信号传输方向的“后方”,而把距离源端最远的一端称为“远端”,远端信号传输方向的“前方”。

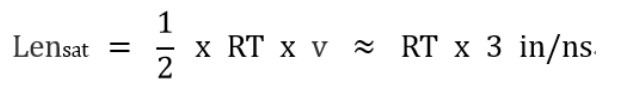

一对传输线,耦合区域的总时长为TD,当信号的上升边RT 是2xTD时,或者说耦合长度是上升边空间延伸的一半,那这个长度为饱和长度。

Lensat 表示近端串扰的饱和长度(单位为in),RT表示信号上升边(单位为ns),V表示信号在动态线上的传播速度(单位为in/ns)。

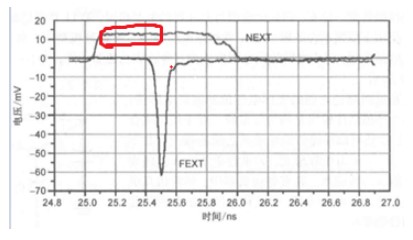

噪声电压即近端串扰幅值(NEXT)达到一个稳定值,当耦合长度大于饱和长度。

当耦合长度小于饱和长度,则电压峰值将小于NEXT。

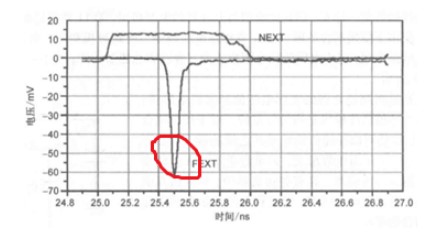

远端噪声以脉冲形式出现,信号进入算起,一直要经过TD 时延之后才会出现噪声。噪声在静态线上的传播速度与信号的速度相等。

FEXT远端噪声幅值除了跟远端噪声峰值电压与信号电压比值有关,还与另两个外在参数(耦合长度和上升边)呈比例变化。

这里需要强调一点:

因为感性耦合电流的方向是从返回路径到信号路径,呈逆时针方向,这与容性耦合电流的方向相反。所以,在远端的净噪声是容性耦合噪声与感性耦合噪声之差。

产品的更新换代,版图的密集性以及速率的提升,通过调整耦合长度和上升时间(RT)来管控的情况已经很少了,所以我们能做的大多数就是调整线距来控制串扰,而调整线距确实可以减小串扰。

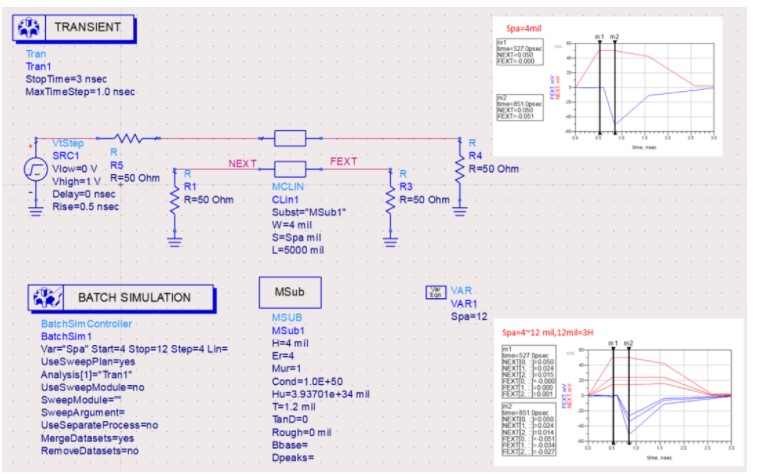

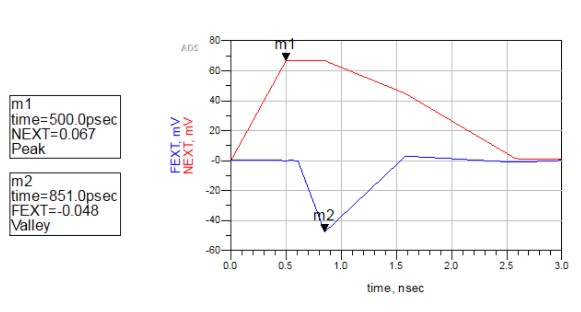

下图为调整Spa的链路以及仿真结果:

Spa=4 mil,噪声的幅值最大。

需要说明的是,想用的是3H原则,只不过很不巧,竟然也是3W原则。

实际工作中,串扰的管控除了重点关注线间距,返回路径也需要注意。至于带状线层布线,使用介电常数较低的材料等,这些深入且细节的知识,后面有机会再讲。

审核编辑:刘清

-

传输线

+关注

关注

0文章

376浏览量

24040 -

串扰

+关注

关注

4文章

189浏览量

26955 -

耦合电感

+关注

关注

0文章

77浏览量

20100 -

PCB

+关注

关注

1文章

1809浏览量

13204

发布评论请先 登录

相关推荐

串扰是什么?如何去减小串扰

串扰是什么?如何去减小串扰

评论