之前,和EE的小伙伴交流,谈到高速信号。他说:你们SI只要看看那些频率大于100MHz的信号,什么USB、PCIe就行了,其他的就不用关心了。那些时钟Buffer出的100M,那些UART,SPI等低速信号我们就看看线长,随意管控就行了。

查了查,整理一下市面上对高速信号的相关定义:

1.频率大于100MHz的信号;

2.上升沿(或下降沿)小于100ps的信号;

3.上升时间小于5倍的信号传输延时。

想一想:时钟Buffer出的100M,算不算高速信号?

从理论上来说,这个信号是不是高速信号,就是判断这个信号是否在传输过程中有SI 的问题,需不需要管控?

关于高速信号定义的第一点。频率大于多少就定性为是否是高速信号,那就是高频和高速的区别。高频是否就是高速?

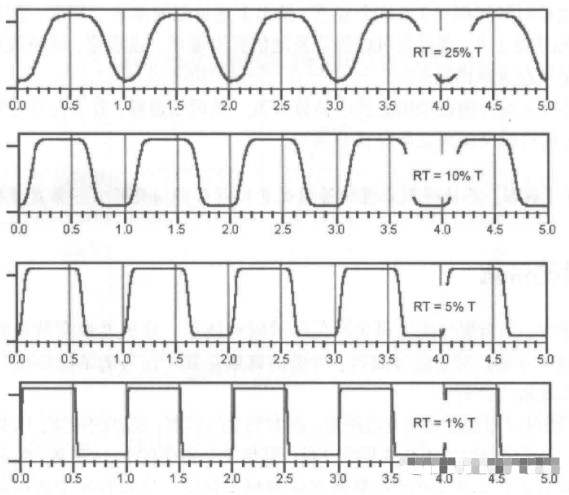

话不多说,直接上图:

同样是1GHz的信号,信号的边沿越陡峭,高频分量就越多,就需要管控其信号完整性。同样,信号的边沿不陡峭,就不需要管控了,所以频率大于多少的信号,是否是高速信号,要看情况。不能简单地认为高频就是高速,不能把高频和高速混为一谈。

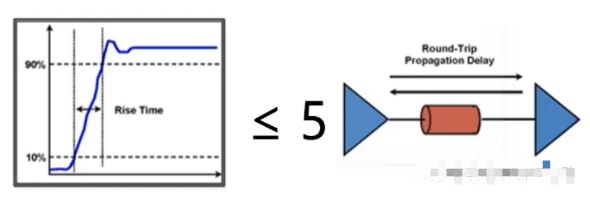

接下来讲高速信号定义的两点,都是关于上升时间有关。实际上,SI 的大多数问题也都是和信号的上升时间(RT)有关。

上升时间:低电平到高电平,电压幅值从10%~90%的时间。也有一种说法:20%~80%。我们这里选择10%~90%。

当传输线时延大于信号上升边20%,会有信号完整性问题,振铃噪声可能影响电路功能,需要加以管控。反推出,传输时延和信号上升时间的关系:

注:5倍只是一个理论预估值,不是绝对值

接下来,我们举例子来说明一下 :

100 M时钟的线长,方便计算,我们这里取10000 mil。考虑建模搭建的是微带线,信号传输时延取值约为170 ps/in ,时延时间为170 * 10 =1700 ps =1.7 ns。推算出五倍时延为1.7 * 5 =8.5 ns。

微处理的产品,典型的上升边一般是周期的10%,当然也有的是5%,我们这里取10%,得出100 M时钟信号的上升边约为1 ns。

8.5 ns 大于信号上升时间1 ns。也就是说,从理论上来看,需要对信号进行管控。对比传输线长为100 mil时候,时延只有17 ps ,不会对信号产生影响,则不需要管控。

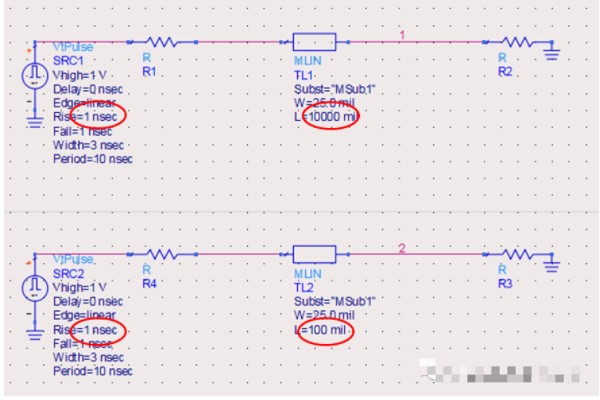

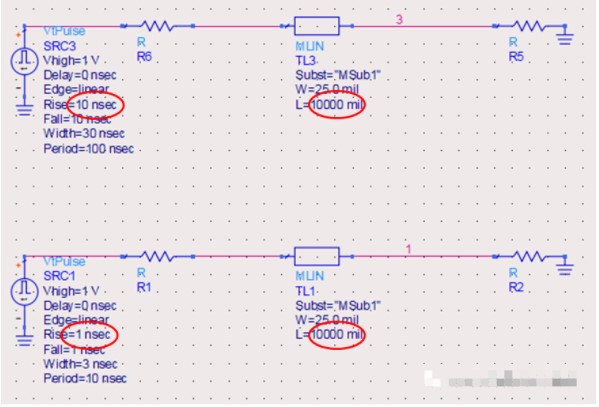

用仿真软件搭建相关电路:

第一种情况

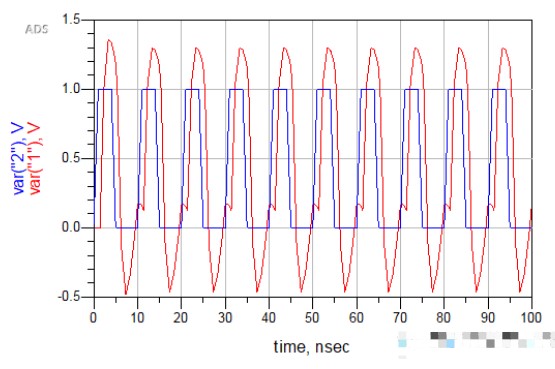

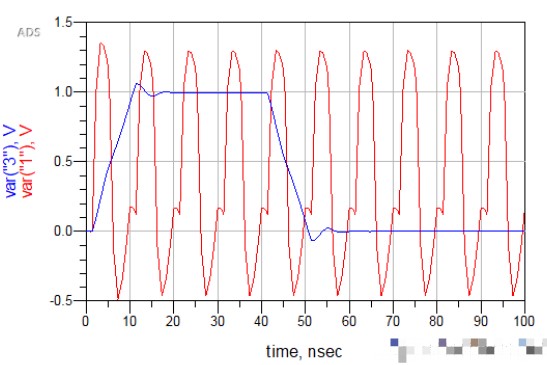

仿真出相应节点的波形:

当信号线长为10000 mil时,振铃现象很严重,阻抗突变带来很明显的影响。而信号线长为100 mil时,阻抗突变带来的变化对信号根本没有任何影响。

第二种情况

将信号的上升时间调整为10 ns,10 ns大于 8.5 ns,理论来看,阻抗突变对信号的影响有限。来看一看仿真的结果:

随着上升时间变大,阻抗突变对信号的影响可以忽略。

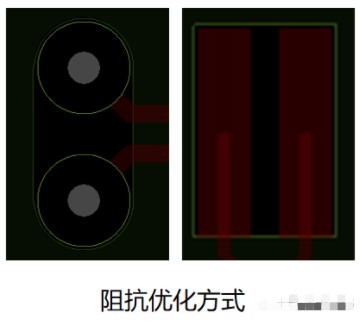

当高速信号需要管控的时候,考虑到阻抗不匹配反射对信号质量的影响,针对本例来看,需要对链路中的过孔和SMT连接器进行阻抗优化处理,来减少阻抗突变对信号质量的影响。

优化方式见下图:

审核编辑:刘清

-

连接器

+关注

关注

98文章

14824浏览量

137779 -

时钟

+关注

关注

11文章

1756浏览量

132137 -

smt

+关注

关注

41文章

2949浏览量

70072 -

buffer

+关注

关注

2文章

120浏览量

30222 -

高速信号

+关注

关注

1文章

234浏览量

17817

发布评论请先 登录

相关推荐

使用adc08200 100M采样,当有高压脉冲干扰时,AD输出出错怎么解决?

高速AD加上时钟后,输入信号会有一个两倍于时钟信号的毛刺产生是什么原因

想用DAC904输出一个较高频率的正弦波,可以用100M的晶振作为时钟源吗?

使用TXB0108时,时钟信号为什么会改变?

请ADC08100不能工作在100M采样速率吗?

LMX2594EVM自带的时钟板没有100M的时钟输出,是什么原因?

OPA690可以将100M的信号进行同向放大吗?

为什么opa695在达到100M前输出会有波动?

200M示波器用100M探头会怎样呢?

STM32F767+DP83848K速度到不了100M的原因?

100mΩ,2.5 A 单通道汽车智能高侧开关TPS1HC100-Q1数据表

40V、100mΩ 单通道智能高侧电源开关TPS1H100-Q1数据表

60V、100mΩ、单通道智能高侧开关TPS281C100x数据表

时钟Buffer出的100M算不算高速信号?

时钟Buffer出的100M算不算高速信号?

评论